-

질문 & 답변

카테고리

-

세부 분야

반도체

-

해결 여부

미해결

lab18,19 질문

23.07.25 04:35 작성 23.07.25 21:41 수정 조회수 284

1

안녕하세요 맛비님! 항상 강의 잘 듣고 있습니다.

lab18, 19에서 질문이 있습니다!

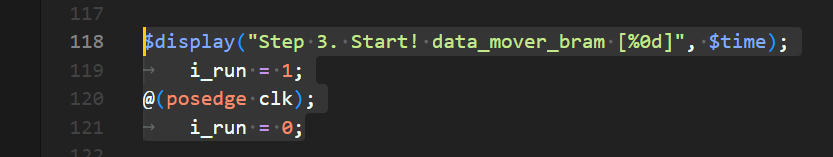

lab18의 tb 코드에서 보면 i_run을 한 clk 주기동안만 켰다가 바로 끄도록 해두셨는데 이렇게 하신 이유가 있을까요? (i_run을 켜두면 이후에 문제가 생긴다든가..)

lab19의 main.c 코드에서는 ctrl_reg에 run 신호를 주고 이후에는 손대지 않는 것 같은데 이 부분이 tb와 어떻게 같아지는지 궁금합니다!

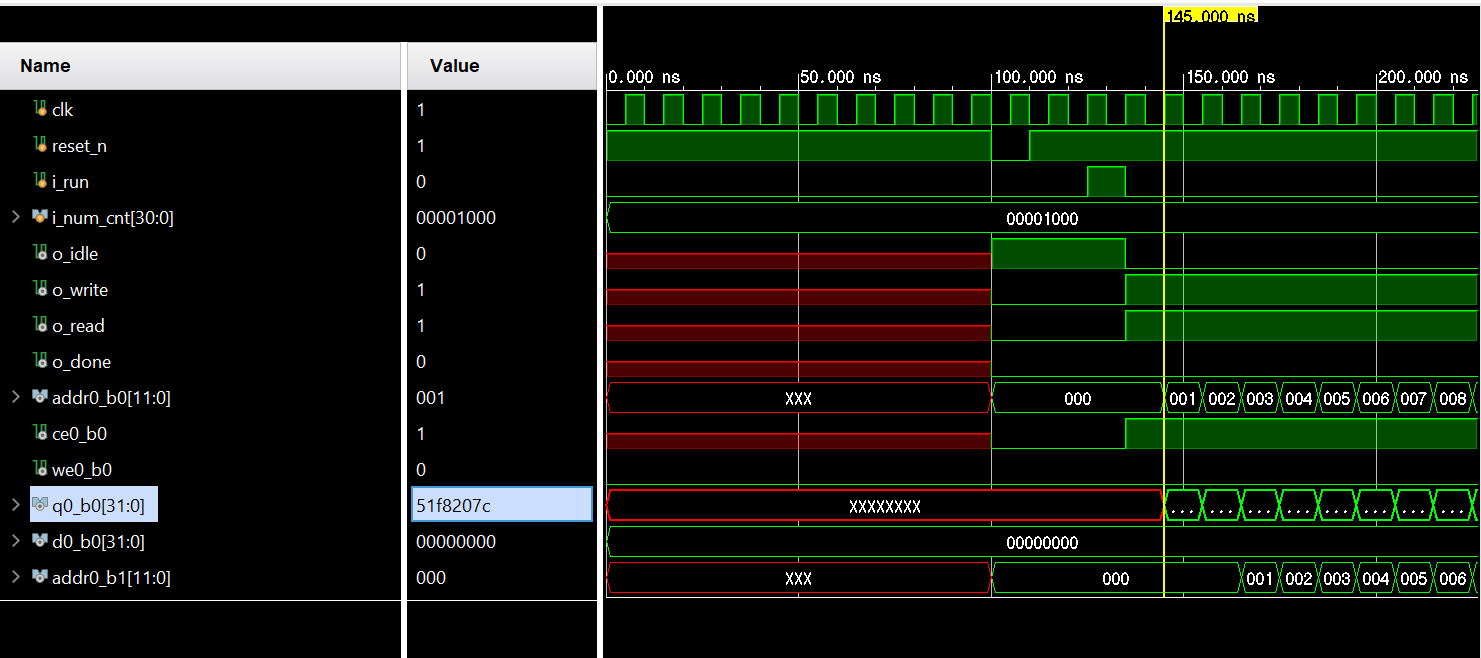

lab19의 main.c 코드에서는 ctrl_reg에 run 신호를 주고 이후에는 손대지 않는 것 같은데 이 부분이 tb와 어떻게 같아지는지 궁금합니다!lab19의 data_mover_bram에서 input으로 i_run을 받을 때 q_b0가 동시에 들어오지 않고, 다음 clk에 o_read가 켜지고 그 다음 clk에 q_b0가 들어오게 되는 이유가 궁금합니다!(tb 시뮬레이션에서 보았습니다)

느낌상 bram을 거쳐야 하기 때문에 <<data_mover_bram의 ce가 켜지면서 output으로 나가고 이게 u_bram0에 input으로 들어가면서 bram이 q0를 내보내줄 수 있는.. >> 이런 과정일 것 같은데 이게 두 클락만에 벌어질 수 있는 일인가요,..?? 이게 아니라면 어떤 과정이 있어서 i_run과 q_b0가 두 클락 차이가 나는지 궁금합니다2번 그림에서 o_write가 켜지는 동시에 bram0의 reg의 값을 읽는 게 아니라 o_write가 켜지고 다음 상승 엣지에서 bram0의 0번째 값을 읽는 거 아닌가요? 그런데 왜 addr0_b0(data_mover_bram에서의 cnt 값)가 다음 상승 엣지에서 바로 1이 되는지 궁금합니다. cnt가 1이 됐다는 건 0번째 값을 이미 읽었다는 의미가 아닌가요,,??

너무 장황하게 쓴 것 같은데 생각의 흐름에서 틀린 부분이 있다면 짚어주시면 감사하겠습니다ㅜㅜ!!!

답변을 작성해보세요.

0

설계독학맛비

지식공유자2023.07.28

안녕하세요 :)

A1. 설계자의 스펙이라고 생각해주시면 될 것 같습니다. 질문자님 말씀대로 쭉 '1' 로 주도록 설계하고 싶다. 그렇다면 그렇게 하셔도 됩니다. 현업설계에서 다양한 방법으로 run 을 주오니, 그렇게 큰 의미를 두지 않으셔도 될 것 같습니다. (회사마다 스타일이 달라요)

A2. bram 의 read latency 의 영향으로 cycle 이 밀린거에요. (코드를 자세히 보면 답이 되실꺼에요)

A3. 3번질문은 제가 이해가 잘 안되는데요 ㅠㅠ 핵심은 bram read 의 sync 를 맞춰야 valid 한 read 값을 사용할 수 있다 입니다. 그 점을 유의해서 보시면 될 것 같아요.

즐공하세요 :)

0

인프런 AI 인턴

2023.07.27

안녕하세요, 인프런 AI 인턴이에요.

lab18의 i_run 신호를 한 클럭 주기 동안만 켰다가 끄는 이유에 대해서는 직접 강의를 듣고 작성된 코드를 살펴봐야 정확한 이유를 알 수 있을 것 같습니다. 하지만 일반적으로, i_run 신호를 한 클럭 주기 동안만 켜고 끄는 것은 특정한 동작을 수행하기 위한 제어 신호의 역할을 할 수 있습니다. 이렇게 제어 신호를 사용하여 특정 조건에서만 동작하는 경우, 신호의 길이를 제한함으로써 잘못된 동작을 방지하거나 신호 전달 시간을 최적화하는 등의 목적을 가질 수 있습니다.

lab19의 main.c 코드에서 ctrl_reg에 run 신호를 밖에서 주고 이후에도 손대지 않는 이유에 대해서는 동영상 강의를 통해 자세히 알 수 있을 것 같습니다. run 신호는 제어 신호로서 동작을 제어하는 역할을 할 수 있습니다. main.c에서 run 신호를 주고 이후에는 손대지 않는 이유는 해당 신호가 초기에 설정된 조건에 따라 동작을 적절히 수행함으로써 원하는 결과를 얻기 위함일 수 있습니다.

data_mover_bram에서 i_run 신호와 q_b0 신호 간의 클럭 싱크 차이에 대해서는 두 클럭 신호가 다른 동작을 수행하기 때문에 발생할 수 있는 것으로 보입니다. 신호의 수신 및 처리가 한 클럭 싸이클에서 이루어지는 것이 아니라 여러 클럭 싸이클을 거쳐서 이루어질 수 있기 때문에 그런 차이가 발생한다고 생각됩니다. 하지만 정확한 동작 원리를 알기 위해서는 상세한 코드와 설계 내용을 확인해야할 것 같습니다.

마지막으로, 2번 그림에서 o_write가 켜지면서 bram0의 reg 값을 읽는 시점에 대해서는 직접 코드를 살펴봐야 정확한 답변을 드릴 수 있을 것 같습니다. 하지만 일반적으로 레지스터의 값을 읽는 것은 해당 신호가 상승 에지에서 발생할 때 이루어지는 경우가 많습니다. 따라서 o_write가 켜진 다음 상승 에지에서 bram0의 값이 읽히는 것으로 예상됩니다.

더 자세한 설명을 위해서는 작성된 코드와 디자인 내용을 참고해야 하므로, 강의 또는 관련 자료를 확인해보시기 바랍니다. 좋은 결과를 얻을 수 있도록 도움을 드리겠습니다. 감사합니다.

답변 2