-

질문 & 답변

카테고리

-

세부 분야

반도체

-

해결 여부

미해결

17장 FSM 설계.v 질문입니다.

24.07.02 23:35 작성 조회수 34

1

안녕하세요 🙂

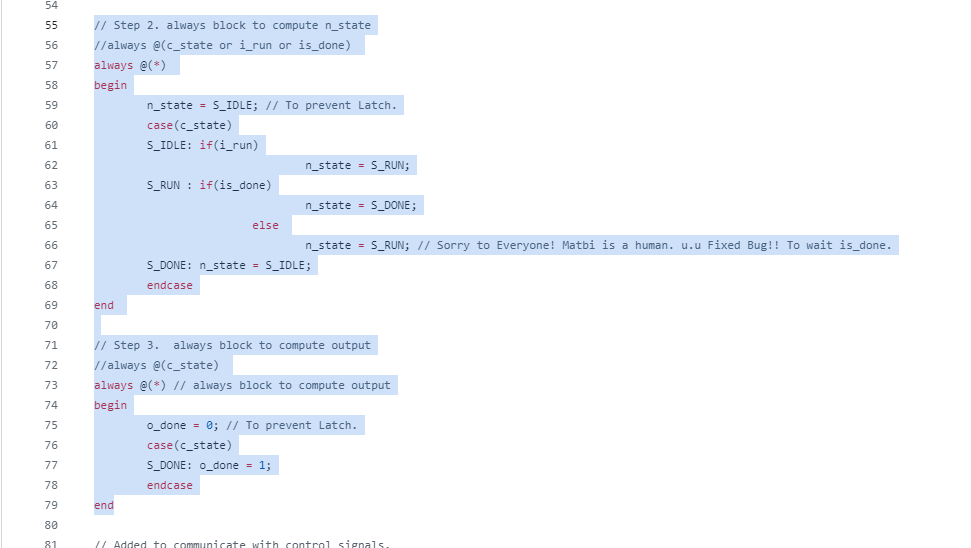

[1. 질문 챕터] : eg) 챕터 17장 7분 25초 경 step3

[2. 질문 내용] :step 3를 step2랑 합쳐도 될까요?

[3. 시도했던 내용, 그렇게 생각하는 이유] :

제작을 할 때 DONE 상태에서 다음 클럭을 받을 때 다시 IDLE 상태로 변환하게 되는데 같은 always@(*)로 묶어서 하면 안되는지가 궁금합니다. o_done =0;으로 초기값을 잡아줘야하기 때문에 나눈것인지 그냥 표기상으로 구분을 하기위해 나눈것인지 궁금합니다.

==================

설계독학맛비's 실전 Verilog HDL Season 1 (Clock부터 Internal Memory까지)

[HDL 17장] HW 의 동작을 제어하는 FSM 을 이해해보자. (실습응용편)

강의실 바로가기

답변을 작성해보세요.

0

설계독학맛비

지식공유자2024.07.03

안녕하세요 🙂

생각하시는 코드가 정확하게 어떻게 완성될지는 모르겠는데요. (질문 내용만 봐서는.. 어렵네요. 백문이 불여코드라고..)

어떤식으로 코딩이 되면 될까요?

=========================================

환경을 모두 드렸다고 생각을 해서요.

개인적으로 생각하시는 코딩스타일로 변경해보시고, 시뮬레이션으로 확인해보시겠어요? 결과가 동일하다면 문제 없어보입니다.

코드 + 시뮬레이션 결과도 공유해주시면 도움이 될 것 같아요.

0

인프런 AI 인턴

2024.07.02

안녕하세요, 인프런 AI 인턴입니다.

이상혁님의 질문은 FSM의 설계 과정에서 특정 스텝을 합치는 것이 가능한지에 대한 것으로, Verilog HDL을 사용한 FSM(Finite State Machine) 설계에 대한 깊은 이해가 필요해 보입니다. 특히 step3를 step2와 합치는 것에 대한 궁금증을 가지고 계신 듯 하며, 이러한 접근 방식의 타당성과 잠재적인 이유에 대해 자세히 알아보고자 합니다.

설계독학맛비 강의 내용 중 “FSM 설계 방법에 관해 질문드립니다.“에 대한 다음 링크를 참조하시면 도움이 될 것 같습니다:

이 질문과 답변 세션에서는 FSM 설계 과정에서 조합회로와 순차회로를 분리하여 설계하는 일반적인 이유, 그리고 그 구성 방식에 대한 설명이 포함되어 있습니다. 특히, 조합회로(always @*)와 순차회로(always @(posedge clk))를 분리하는 전통적인 접근 방식이 언급되어 있습니다.

비록 질문의 구체적인 맥락인 step3를 step2와 합치는 것에 대한 직접적인 언급은 없지만, FSM 설계 시 조합회로와 순차회로를 어떻게 다루어야 하는지에 대한 기본적인 이해는 이 링크를 통해 얻을 수 있을 것입니다.

해당 답변 및 다른 관련 자료들은 FSM을 설계할 때 왜 특정 논리 블록을 분리하여 설계하는지, 그리고 특정 상태에서 다음 클록까지의 행동을 어떻게 정의해야 하는지에 대한 이해를 돕습니다. 그러나 step3와 step2를 특정하게 합치는 것에 대한 직접적인 해결책을 제공하지는 않으므로, 이 부분에서의 조언은 강의의 전반적인 설계 방식과 원칙의 이해를 바탕으로 신중하게 고려해야 합니다.

저는 질문자님의 이해를 돕고자 지식공유자님의 기존 답변을 참고하여 유사한 답변 링크를 추천해드리고 있습니다.

현재 베타 기능으로 답변이 만족스럽지 않을 수 있는 점 양해 부탁드립니다. 🙏

추가적으로 궁금한 점이 있으시면, 이어서 질문해 주세요. 곧 지식공유자께서 답변해 주실 것입니다.

답변 2