-

질문 & 답변

카테고리

-

세부 분야

반도체

-

해결 여부

미해결

안녕하세요! 타이밍 관련 질문입니다

23.07.11 15:11 작성 조회수 452

1

axi_lite ip를 만들고 시뮬레이션을 보던 와중에 궁금증이 생겨 질문합니다.

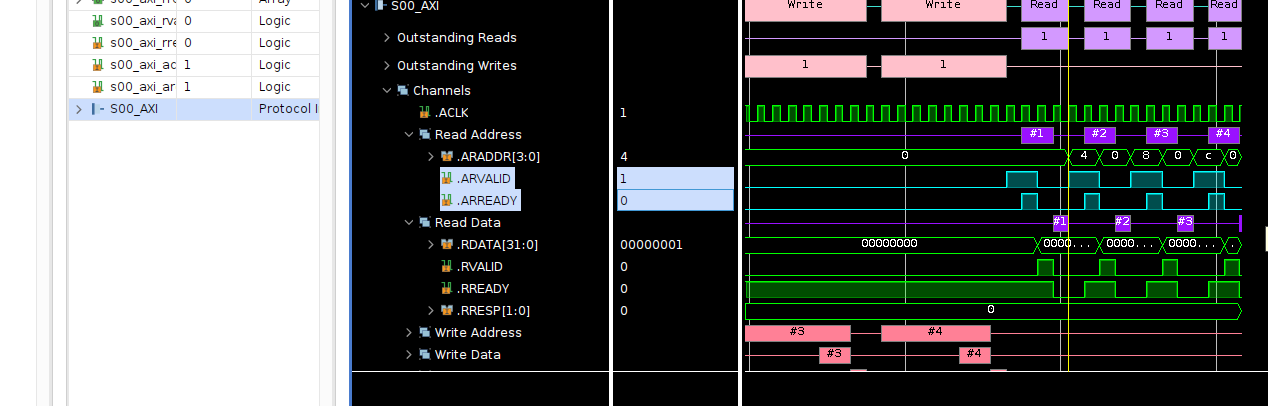

다른 채널의 신호들은 ready/valid handshake를 정확히 지켜서 r/v가 켜진 후 다음 clk edge 에서 신호가 업데이트 되는데 AR 채널만 다른 타이밍에 업데이트 되더라구요!

아직 코드를 자세히 리뷰해보지 않았는데 맛비님의 설명도 듣고싶습니다 감사합니다

설계독학맛비's 실전 FPGA를 이용한 HW 가속기 설계 (LED 제어부터 Fully Connected Layer 가속기 설계까지)

[FPGA 7장] HW IP 를 제어하기 위한 AXI4-Lite Interface 이해하기 - 코드리뷰편

강의실 바로가기

답변을 작성해보세요.

0

장시온학부생

질문자2023.07.11

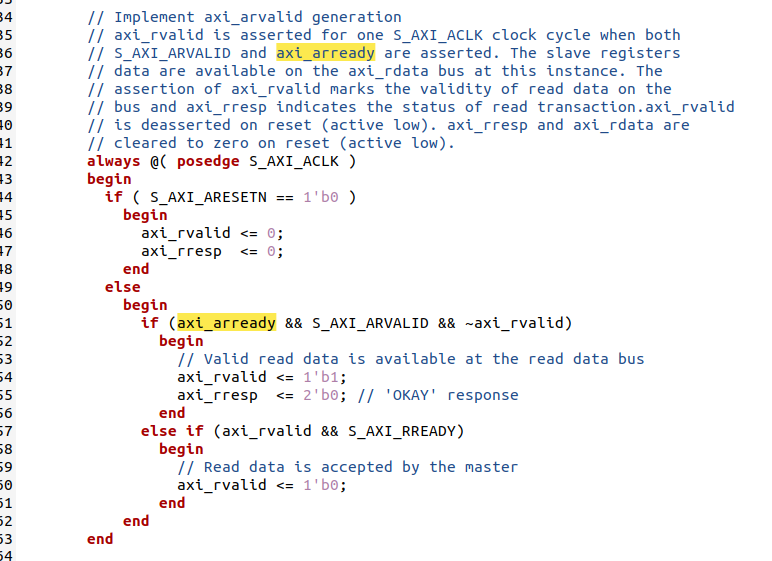

하하.. 리뷰를 먼저 다 해볼걸 그랬네요. 코드를 보니 제 생각이 맞는 것 같아요! arready, arvalid가 모두 1일 때 rvalid가 1로 올라가고, data read가 가능해지네요. 그게 위에서 말한 0 4 0 8 0 c 에서 '0'의 타이밍이 되겠군요!

하하.. 리뷰를 먼저 다 해볼걸 그랬네요. 코드를 보니 제 생각이 맞는 것 같아요! arready, arvalid가 모두 1일 때 rvalid가 1로 올라가고, data read가 가능해지네요. 그게 위에서 말한 0 4 0 8 0 c 에서 '0'의 타이밍이 되겠군요!

Read와 write는 ready valid 가 모두 1일때 동작이 일어나고, 내부적으로 AR은 ready,valid이 다른 의미로 사용되는 것으로 이해하겠습니다 :)

감사합니다!

0

장시온학부생

질문자2023.07.11

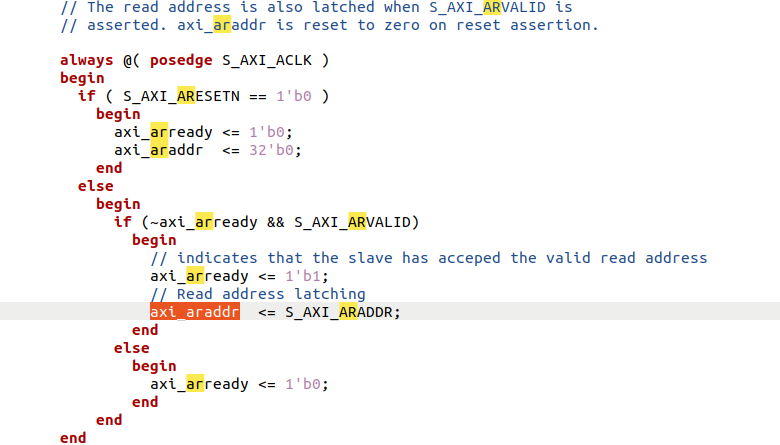

이 부분을 보니 이해가 가네요! 애초에 read address 자체는 input이고, 그 주소값을 axi_araddr 레지스터에 인가해주는 타이밍이 arready가 0, arvalid가 1일 때 이군요!

그 후에 다시 arready를 0으로 만들어줘서 address를 새롭게 받을 준비를 하고 ..

그래서 ARADDR에 0 4 0 8 0 c 이런 식으로 하나의 텀을 두고 타이밍이 맞춰지는 것 같은데, 연속으로 0 4 8 c .. 이렇게 값을 넣지 않는 이유가 있을까요?

제 추측으로는 Read data를 위한 타이밍을 만드는 것인가 싶기도 한데, 그렇다면 AXI lite 프로토콜에서는 이런 형식을 꼭 맞춰야 할 것 같은데 제 생각이 맞을까요?

설계독학맛비

지식공유자2023.07.12

안녕하세요 :)

깨달음? 이 있으신 것 같아서, 밑에 물음표만 답변드립니다.

=======

그래서 ARADDR에 0 4 0 8 0 c 이런 식으로 하나의 텀을 두고 타이밍이 맞춰지는 것 같은데, 연속으로 0 4 8 c .. 이렇게 값을 넣지 않는 이유가 있을까요?

넣지 않았다기 보다는, AXI4-Lite I/F 는 연속으로 System 상에서 넣기 어려운 I/F 입니다.

AXI4-Lite 에는 Burst 의 개념과 Multiple Outstanding Address 의 개념이 없습니다.

위 단어를 공부하시면 답이 되실꺼에요.

=======

제 추측으로는 Read data를 위한 타이밍을 만드는 것인가 싶기도 한데, 그렇다면 AXI lite 프로토콜에서는 이런 형식을 꼭 맞춰야 할 것 같은데 제 생각이 맞을까요?

AXI 의 Spec 문서가 규정하는 대로 구현되면 됩니다. (어찌보면 형식을 맞춘거죠)

해당 강의에서 다루기에는 내용이 방대해서.. (Verilog HDL 시즌2 가 있습니다.)

이거는 AXI 의 스펙문서를 보시고 공부하셔야 이해가 되실꺼에요.

즐공하세요 :)

답변 2