-

질문 & 답변

카테고리

-

세부 분야

반도체

-

해결 여부

미해결

WDATA latch / RESET state에 대한 질문 드립니다.

24.06.19 07:29 작성 조회수 67

1

=================

현업자인지라 업무때문에 답변이 늦을 수 있습니다. (길어도 만 3일 안에는 꼭 답변드리려고 노력중입니다 ㅠㅠ)

강의에서 다룬 내용들의 질문들을 부탁드립니다!! (설치과정, 강의내용을 듣고 이해가 안되었던 부분들, 강의의 오류 등등)

이런 질문은 부담스러워요.. (답변거부해도 양해 부탁드려요)

개인 과제, 강의에서 다루지 않은 내용들의 궁금증 해소, 영상과 다른 접근방법 후 디버깅 요청, 고민 상담 등..

글쓰기 에티튜드를 지켜주세요 (저 포함, 다른 수강생 분들이 함께보는 공간입니다.)

서로 예의를 지키며 존중하는 문화를 만들어가요.

질문글을 보고 내용을 이해할 수 있도록 남겨주시면 답변에 큰 도움이 될 것 같아요. (상세히 작성하면 더 좋아요! )

먼저 유사한 질문이 있었는지 검색해보세요.

잠깐! 인프런 서비스 운영 관련 문의는 1:1 문의하기를 이용해주세요.

==================

안녕하세요. 맛비님.

좋은 강의 감사합니다.

궁금한게 있습니다.

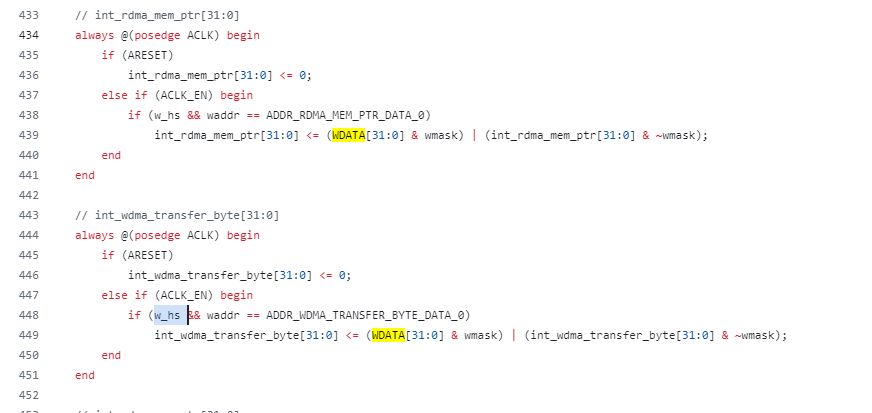

AWADDR의 경우 핸드쉐이크가 발생될 때 변경될 가능성이 있어서 래치를 한다라고 강의에서 들은 것 같은데요.

WDATA도 같은 이유로 변경이 될 수 있을 것이라 보는데 왜 AWADDR만 래치를 하는 건가요?

wstate와 rstate가 가지는 RESET 상태는 있으나 없으나 동작은 같을 것 같은데 왜 존재하는 것인가요?

감사합니다.

답변을 작성해보세요.

0

김상현

질문자2024.06.20

32장-2부 AXI4-Lite I/F - 실습편

12분 40초 쯤에 언급한 내용입니다. AWADDR과 WDATA 둘 다 input인 것 같은데 WDATA가 output이라는 말이 잘 이해가 안되네요.

AWADDR과 마찬가지로 WDATA도 핸드쉐이크 이후에 변경 가능성 때문에 래치를 하는게 맞지 않나라는 생각입니다.

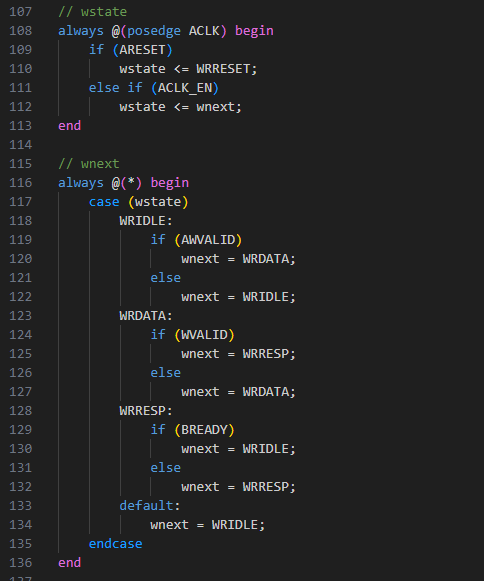

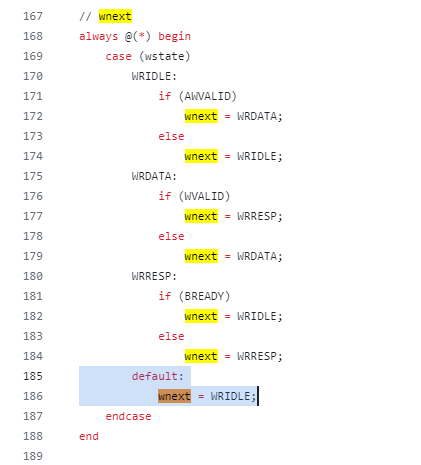

state RESET은 아래 그림을 말한겁니다.

저는 WRRESET의 상태가 왜 필요한지 잘 모르겠습니다.

저는 WRRESET의 상태가 왜 필요한지 잘 모르겠습니다.

확인 부탁 드립니다. 감사합니다.

설계독학맛비

지식공유자2024.06.20

안녕하세요 🙂

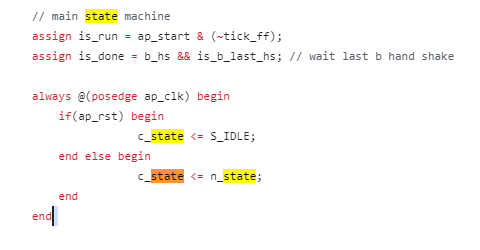

이전 답변은 무시해주시면 되겠습니다. (18,19,20 장은 가야 알 수 있는 AXI DMA 내용입니다)

AXI4-Lite 를 여쭤보신 거군요. (질문을 이제 이해했습니다)

WDATA도 같은 이유로 변경이 될 수 있을 것이라 보는데 왜 AWADDR만 래치를 하는 건가요?

w_hs 에 맞춰서 reg 에 write 하고 있습니다. 따라서 이미 하고 있다고 생각하시면 되겠습니다.

wstate와 rstate가 가지는 RESET 상태는 있으나 없으나 동작은 같을 것 같은데 왜 존재하는 것인가요?

말씀해주신 것이 맞습니다. 현재코드에서는 WRIDLE 로 돌리셔도 정상적으로 동작합니다.

다만 WRRESET 상태는 185, 186 번째 라인의 default 에 해당함으로, reset 다음 cycle 이후에 WRIDLE 로 돌아갑니다. 굳이 의미를 찾자면 reset 이후 다음 cycle 에 IDLE 하는 것이 차이겠네요. 다시 말씀드리지만 현재 실습코드에서는 빼셔도 됩니다. (설계자가 판단하면 되겠습니다)

즐공하세요 🙂

0

설계독학맛비

지식공유자2024.06.19

안녕하세요 🙂

"AWADDR의 경우 핸드쉐이크가 발생될 때 변경될 가능성이 있어서 래치를 한다" 혹시 강의에서 어디 부분인지 알 수 있을까요? (저도 사람이라 모든걸 기억하지는 못하네요 ㅠ)

AWADDR 은 WDMA 기준 output 이라서요. 변경될 가능성 보다는 timing 측면을 위해서 F/F out 으로 출력하기 위함이다 라고 하면 더 좋을 것 같아요.

래치 라는 표현을 쓴것은 모듈의 input 을 F/F 에 저장하는 행위이고요.

이유는 "변경될 가능성이 있어서" 입니다. 다른 이유로는 F/F 에 저장해놓고 쓰기 때문에 timing 측면에서도 유리하고요. 복합적인 이유가 있어요.

위와 같은 상황을 고려하고 답을 드리면

WDATA도 같은 이유로 변경이 될 수 있을 것이라 보는데 왜 AWADDR만 래치를 하는 건가요?

하셔도 됩니다. 하지만 WDATA 는 output 이라서.. reg out 을 하려고 했다라고 생각하시면 좋을 것 같아요.wstate와 rstate가 가지는 RESET 상태는 있으나 없으나 동작은 같을 것 같은데 왜 존재하는 것인가요?

어디 state 를 말씀하시는 건지 제가 캐치를 못했는데요. reset 이후에 IDLE 부터 시작하고 싶었습니다.

즐공하세요 🙂

답변 2