-

질문 & 답변

카테고리

-

세부 분야

반도체

-

해결 여부

미해결

20강

23.10.12 13:17 작성 23.10.12 14:03 수정 조회수 247

1

20강 BRAM 부분에서

1.

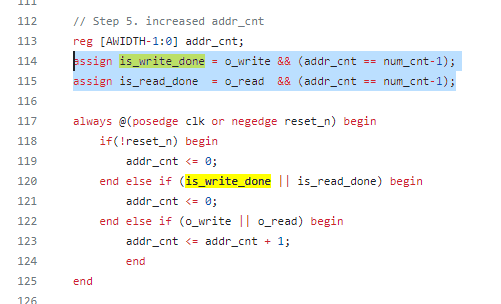

123줄에 addr_cnt +1 한 이유가 뭔가요?

114, 115줄에 assign이 done이 되는 것을 표현할 때 num_cnt-1 == addr_cnt +1 (addr_cnt 0~99에서 99번째일때를 나타냄) 에서 둘의 값을 같게 해서 (값을 99로 ) 라고 생각헸습니다.

그런데 num_cnt-1부분에서 num_cnt 부분이 99번까지 주소를 접근할 수 있는 코드를 찾지 못했습니다. 106줄에서 i_num_cnt가 0~99까지 순차적으로 접근이 자동적으로 되는 것인지 궁금합니다 아니면 제가 코드에서 빼먹은 부분이 있는지 한번 확인해주시면 감사합니다.

-> 다시 한번 찾아보니 always @(posedge)를 통해 반복되는 거 같다고 생각이 듭니다. 확인이 필요한데 맞나요? 간단한 문법인거 같은데 verilog hdl을 며칠전부터 시작하거라.. 하하..

143줄 o_read 1cycle delay를 시켰다는 것을 어떻게 알 수 있나요?

혹시 138 의 always @( posedge clk) 부분을 통해 알 수 있는 건가요? 만약 맞다면 always @ 를 안쓴다면 r_valid 신호가 유효한 값을 읽을 때 동시성으로 인해 동작을 못하는 것이라고 이해하면 되나요?

=================

현업자인지라 업무때문에 답변이 늦을 수 있습니다. (길어도 만 3일 안에는 꼭 답변드리려고 노력중입니다 ㅠㅠ)

강의에서 다룬 내용들의 질문들을 부탁드립니다!! (설치과정, 강의내용을 듣고 이해가 안되었던 부분들, 강의의 오류 등등)

이런 질문은 부담스러워요.. (답변거부해도 양해 부탁드려요)

개인 과제, 강의에서 다루지 않은 내용들의 궁금증 해소, 영상과 다른 접근방법 후 디버깅 요청, 고민 상담 등..

글쓰기 에티튜드를 지켜주세요 (저 포함, 다른 수강생 분들이 함께보는 공간입니다.)

서로 예의를 지키며 존중하는 문화를 만들어가요.

질문글을 보고 내용을 이해할 수 있도록 남겨주시면 답변에 큰 도움이 될 것 같아요. (상세히 작성하면 더 좋아요! )

먼저 유사한 질문이 있었는지 검색해보세요.

잠깐! 인프런 서비스 운영 관련 문의는 1:1 문의하기를 이용해주세요.

==================

설계독학맛비's 실전 Verilog HDL Season 1 (Clock부터 Internal Memory까지)

[HDL 20장] Internal Memory Interface 에 대해 이해해보자 (FPGA 의 BRAM 을 이해하기 - 실습편)

강의실 바로가기

답변을 작성해보세요.

0

설계독학맛비

지식공유자2023.10.13

안녕하세요 :)

123줄에 addr_cnt +1 한 이유가 뭔가요?

다음 address 를 접근하기 위함이었습니다. 질문자님이, counter 로 접근하는 것이 아닌 특정 조건으로 address 를 바꾸고 싶으시면 수정하시면 되겠습니다.

그런데 num_cnt-1부분에서 num_cnt 부분이 99번까지 주소를 접근할 수 있는 코드를 찾지 못했습니다. 106줄에서 i_num_cnt가 0~99까지 순차적으로 접근이 자동적으로 되는 것인지 궁금합니다 아니면 제가 코드에서 빼먹은 부분이 있는지 한번 확인해주시면 감사합니다.

114,115, 120 번째 줄에, address 초기화 부분이 있습니다.

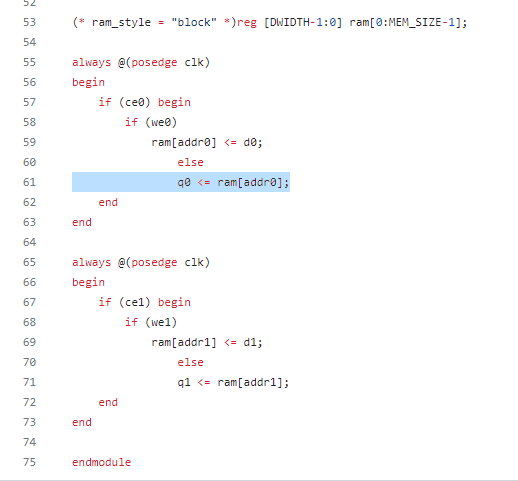

143줄 o_read 1cycle delay를 시켰다는 것을 어떻게 알 수 있나요?

혹시 138 의 always @( posedge clk) 부분을 통해 알 수 있는 건가요? 만약 맞다면 always @ 를 안쓴다면 r_valid 신호가 유효한 값을 읽을 때 동시성으로 인해 동작을 못하는 것이라고 이해하면 되나요?

true_dpbram.v 코드를 보시면, read 는 1 cycle delay 로 모델링 되어 있습니다. 거기에 맞추었다고 보시면 되겠습니다.

true_dpbram.v 코드를 보시면, read 는 1 cycle delay 로 모델링 되어 있습니다. 거기에 맞추었다고 보시면 되겠습니다.

즐공하세요 :)

답변 1