-

질문 & 답변

카테고리

-

세부 분야

반도체

-

해결 여부

미해결

Bitstream 질문입니다.

22.12.15 11:53 작성 조회수 1.98k

1

- 강의 내용외의 개인 질문은 받지 않아요 (개별 과제, 고민 상담 등..)

- 저 포함, 다른 수강생 분들이 함께보는 공간입니다. 보기좋게 남겨주시면 좋은 QnA 문화가 될 것 같아요. (글쓰기는 현업에서 중요한 능력입니다!)

- 학습 관련 질문을 남겨주세요. 상세히 작성하면 더 좋아요!

- 먼저 유사한 질문이 있었는지 검색해보세요.

- 서로 예의를 지키며 존중하는 문화를 만들어가요.

- 잠깐! 인프런 서비스 운영 관련 문의는 1:1 문의하기를 이용해주세요.

안녕하세요. ZC702로 학습 중입니다.

implation까지는 다 잘됩니다..

하지만 1장에서 bitstream에서 막혔습니다.

board가 달라서 생기는 문제인 것 같습니다..

이럴 때는 어떻게 해야할까요..?

도와주시면 감사하겠습니다!

로그는 아래와 같습니다.

ERROR: [DRC NSTD-1] Unspecified I/O Standard: 2 out of 12 logical ports use I/O standard (IOSTANDARD) value 'DEFAULT', instead of a user assigned specific value.

This may cause I/O contention or incompatibility with the board power or connectivity affecting performance, signal integrity

or in extreme cases cause damage to the device or the components to which it is connected. To correct this violation, specify all I/O standards.

This design will fail to generate a bitstream unless all logical ports have a user specified I/O standard value defined.

To allow bitstream creation with unspecified I/O standard values (not recommended), use this command: set_property SEVERITY {Warning} [get_drc_checks NSTD-1].

NOTE: When using the Vivado Runs infrastructure (e.g. launch_runs Tcl command),

add this command to a .tcl file and add that file as a pre-hook for write_bitstream step for the implementation run. Problem ports: led[2], and led[0].

ERROR: [DRC UCIO-1] Unconstrained Logical Port: 2 out of 12 logical ports have no user assigned specific location constraint (LOC).

This may cause I/O contention or incompatibility with the board power or connectivity affecting performance, signal integrity or in extreme cases cause damage

to the device or the components to which it is connected. To correct this violation, specify all pin locations.

This design will fail to generate a bitstream unless all logical ports have a user specified site LOC constraint defined.

To allow bitstream creation with unspecified pin locations (not recommended), use this command:

set_property SEVERITY {Warning} [get_drc_checks UCIO-1].

NOTE: When using the Vivado Runs infrastructure (e.g. launch_runs Tcl command),

add this command to a .tcl file and add that file as a pre-hook for write_bitstream step for the implementation run. Problem ports: led[2], and led[0].

WARNING: [DRC ZPS7-1] PS7 block required: The PS7 cell must be used in this Zynq design in order to enable correct default configuration.

INFO: [Vivado 12-3199] DRC finished with 2 Errors, 1 Warnings

INFO: [Vivado 12-3200] Please refer to the DRC report (report_drc) for more information.

ERROR: [Vivado 12-1345] Error(s) found during DRC. Bitgen not run.

INFO: [Common 17-83] Releasing license: Implementation

17 Infos, 1 Warnings, 0 Critical Warnings and 3 Errors encountered.

write_bitstream failed

ERROR: [Common 17-39] 'write_bitstream' failed due to earlier errors.

답변을 작성해보세요.

2

설계독학맛비

지식공유자2022.12.15

안녕하세요.

(개인의 능력차는 있겠지만) 먼저 강의 내용은 충분히 따라올 수 이다 판단됩니다.

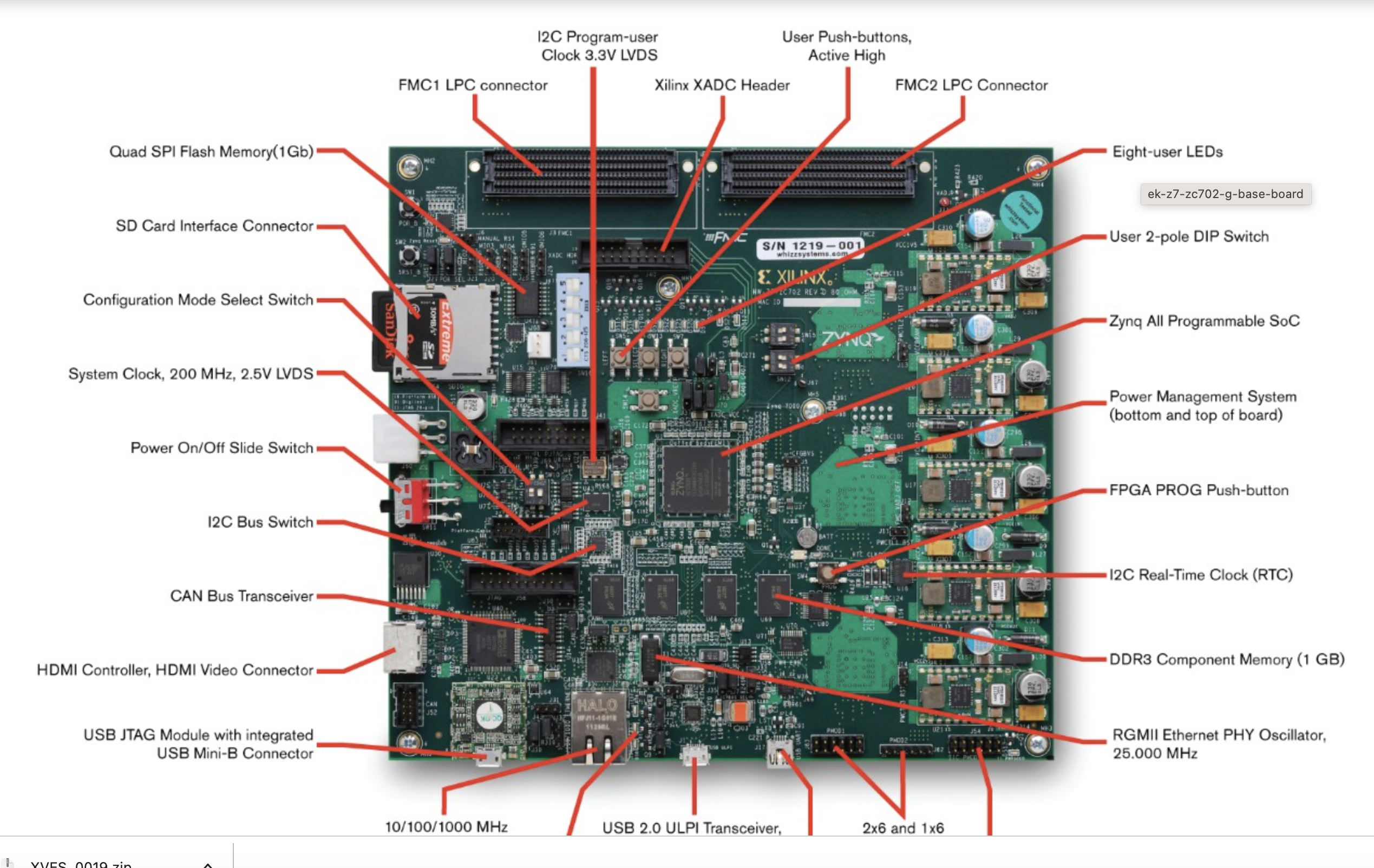

보드의 정보는 다음링크를 참고했습니다. https://www.xilinx.com/products/boards-and-kits/ek-z7-zc702-g.html#resources

이 보드가 아니라면, 다음 답변을 힌트삼아서 해결하시면 될 것 같아요.

적다보니.. 처음 써보신다면.. 어려울 수 있겠다... 싶긴 합니다. 보드가 다르면 답변 자체가 어려워지네요 ㅠ

=========================================

보드는 다르지만 영상을 동일하게 따라하셨다는 가정하에, 현상을 보아 짐작해보면 다음 내용이 문제가 될 것 같아요.

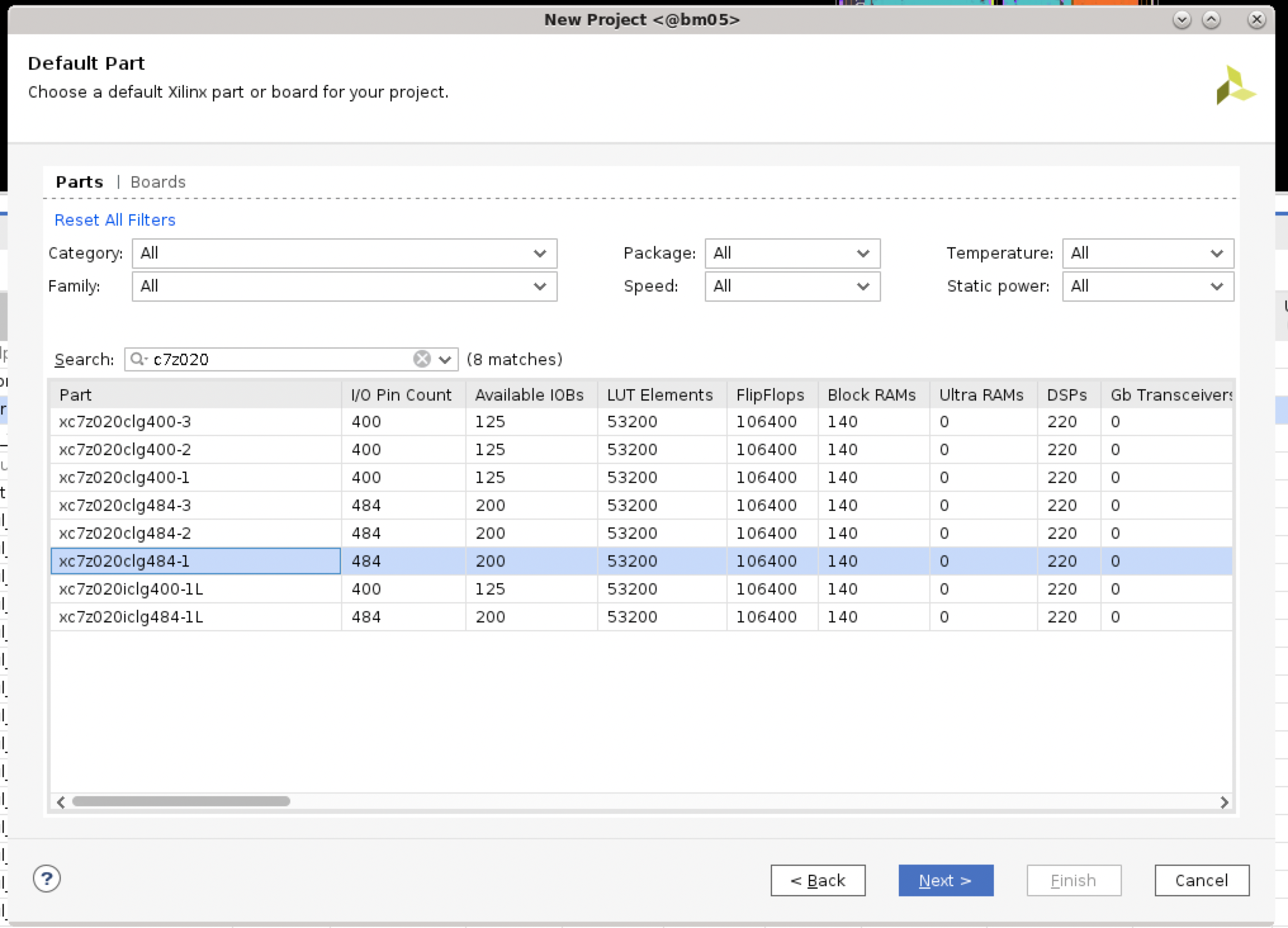

Part number 의 miss

ZC702 : XC7Z020-CLG484-1,

ZyboZ7-20 : XC7Z020-1CLG400C

여기서 프로젝트 만드실 때, 직접 질문자님의 보드에 맞는 part number 를 선택 해주세요. 아마 이걸 것 같습니다.

board 의 pin map 이 기술된 boardfile.xdc 안의 내용에서 miss 가 발생하였기 때문으로 예상합니다.

zybo Z7-20 같은 경우에는 board 에서 사용가능 peri 들과 FPGA Chip 의 pin 간의 pinmap 이 전부 기술되어 있는 Master.xdc 를 제공해 줍니다.

ZC702 용의 master.xdc 가 필요합니다.

https://github.com/develone/zynq-zc702-logic/blob/master/data/ps7_constraints.xdc

ZC702 보드 상에는 led 와 switch 가 존재하기 하네요. 이 부분의 pin map 과 fpga top 의 port 를 정확하게 연결해야합니다.

위의 xdc 파일 을 참고하시고, 회로도를 보시어 해결하셔야 할 것 같아요. 갖고 계신 보드의 rev 확인해보세요.

답변 1