-

질문 & 답변

카테고리

-

세부 분야

반도체

-

해결 여부

미해결

[15장] read cycle

22.12.08 19:56 작성 조회수 191

1

- 강의 내용외의 개인 질문은 받지 않아요 (개별 과제, 고민 상담 등..)

- 저 포함, 다른 수강생 분들이 함께보는 공간입니다. 보기좋게 남겨주시면 좋은 QnA 문화가 될 것 같아요. (글쓰기는 현업에서 중요한 능력입니다!)

- 학습 관련 질문을 남겨주세요. 상세히 작성하면 더 좋아요!

- 먼저 유사한 질문이 있었는지 검색해보세요.

- 서로 예의를 지키며 존중하는 문화를 만들어가요.

- 잠깐! 인프런 서비스 운영 관련 문의는 1:1 문의하기를 이용해주세요.

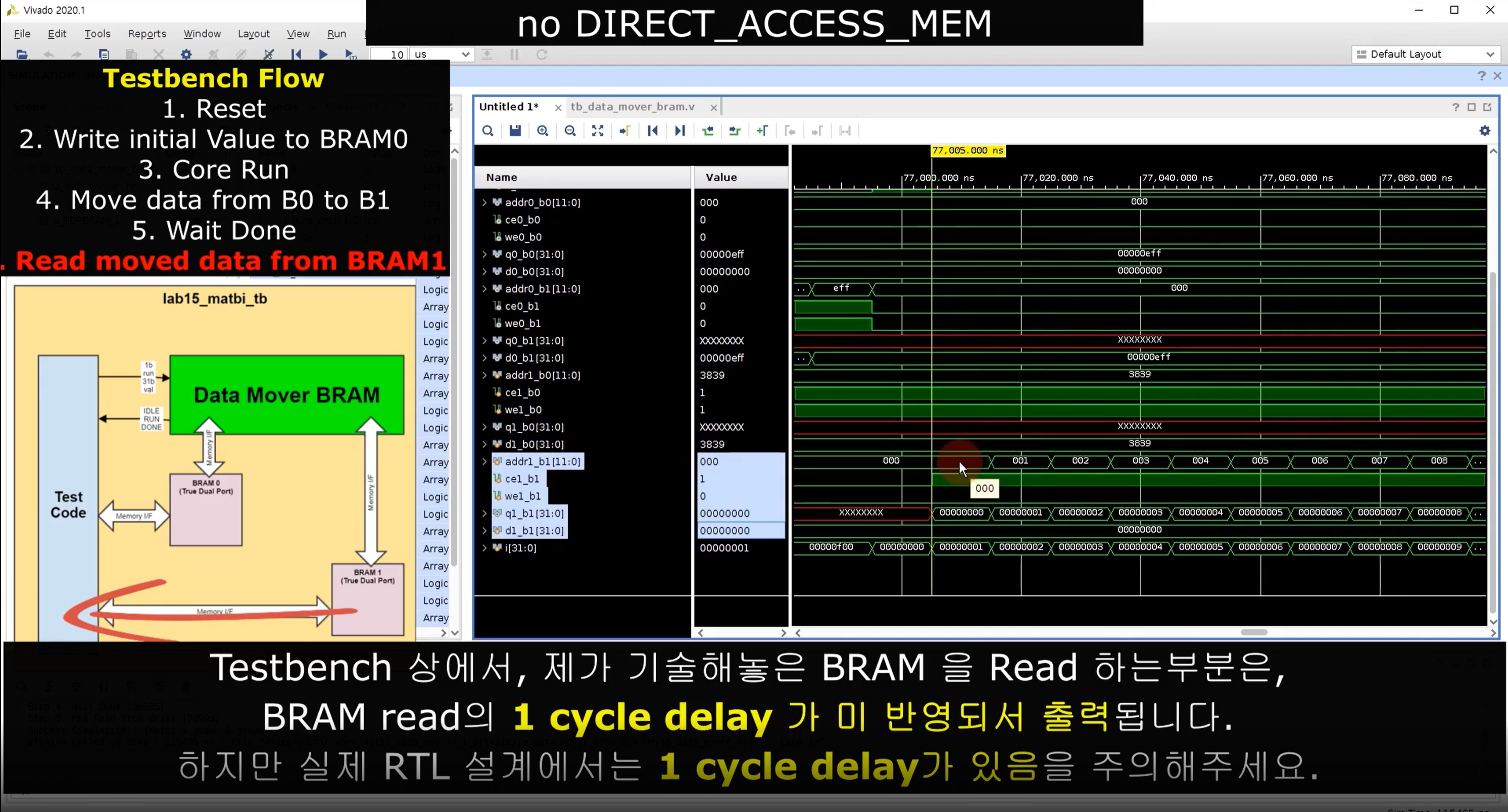

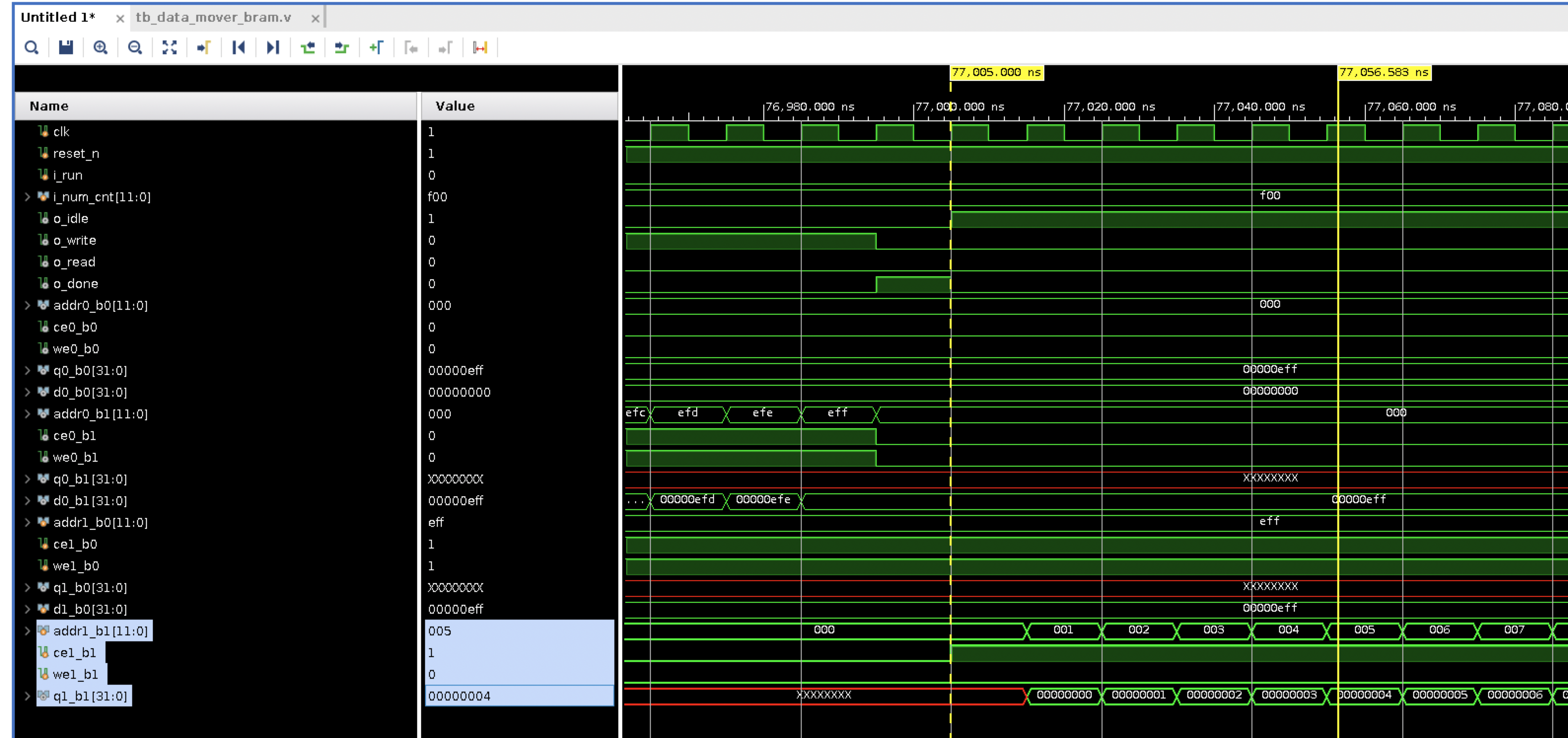

1cycle delay가 왜 미반영 되는지 모르겠어서 질문드려요.

1cycle delay가 왜 미반영 되는지 모르겠어서 질문드려요.

감사합니다.

답변을 작성해보세요.

0

설계독학맛비

지식공유자2022.12.08

안녕하세요 :)

좋은 질문 감사합니다.

결론은 제가 안일했습니다. 궁금해 하실 만 하고요. Sequential logic 인 BRAM 을 ctrl 할때, Clock 동기화의 waveform 을 보기위해선 non blocking 을 사용했어야 옳습니다. 값 확인에 몰두했네요. (아마.. 다른 곳들도 이런 부분들이 남아있을 겁니다. ㅠ)

더 깊게 물어보시면, blocking 문에 따른 시뮬레이터 내부 동작까지 알아야 더 자세한 설명이 가능할 것 같은데요.

이 부분은 제 능력밖이다 미리 말씀드립니다. :)

다음정도 수준의 답이 최선이네요.

==========

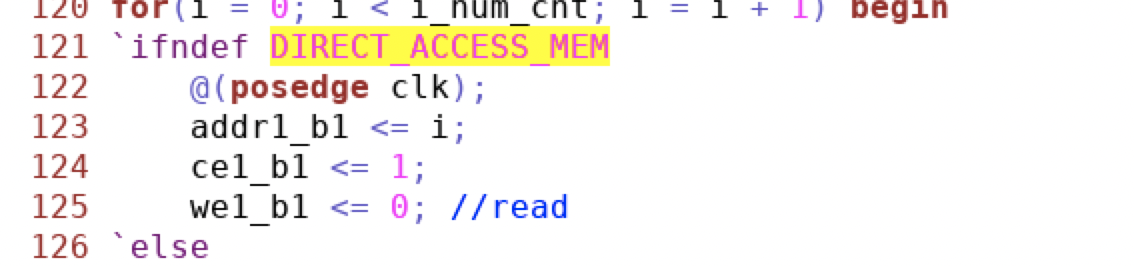

blocking assign (=) 과 non-blocking assign (<=) 의 차이로 보여집니다.

해당 Test bench 에 보시면 제가 blocking assign 으로 코딩을 해놨습니다.

이 부분을 다음처럼 non-blocking assign (<=) 으로 변경하시면, 원래의 알고계신 Clock 동기화된 BRAM 동작으로 확인하실 수 있습니다.

즐공하세요 :)

답변 1