-

질문 & 답변

카테고리

-

세부 분야

반도체

-

해결 여부

미해결

전체적인 디버깅 과정에 대해 질문 드립니다.

22.07.29 21:13 작성 조회수 153

1

simulation -> synthesis -> implement -> bitstream -> vitis

위 모든 과정을 거쳐야 비로소 board의 상태를 확인하고, 저의 코드가 맞았는지 확인할 수 있는데, 과정이 너무 긴것 같습니다.

최소 10분 이상은 걸리는 것 같아요.

또, 1. 시뮬레이션이 잘 나와도 board에서 결과가 잘 안나오는 경우도 많은 것 같습니다 ( 그냥 단순히 제 잘못 일까요? )

제가 맛비님처럼 엄청난 고수였다면, verilog 코드를 보고 오류를 한번에 찾아내서 다시 시뮬레이션 돌려도 시간 낭비가 별로 없겠지만, 제 수준에서는 이게 틀렸나? 저게 틀렸나? 하나 하나씩 코드를 고쳐가며 조금씩 진행하다보니, 다시 시뮬레이션을 돌리는 시간이 너무 오래걸립니다.

2. 이러한 상황에서 주실 수 있는 팁 혹은 맛비님의 검증 방법이 궁금합니다.

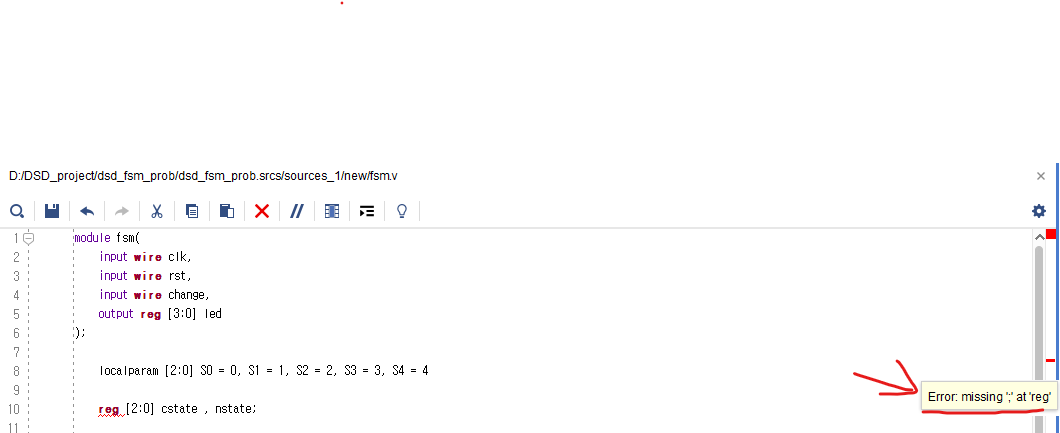

참고로 저는 위 사진처럼 vivado tool 내의 디버깅을 사용하는 중입니다. 3. 일반적으로 vivado tool 디버깅을 사용 하시나요?

오늘도 내일도 좋은 하루 되세요 맛비님.

답변을 작성해보세요.

0

설계독학맛비

지식공유자2022.07.29

안녕하세요 :)

충분한 검증 없이 보드상에 올리면, 디버깅에 많은 시간이 걸리게 됩니다. (당연한 이야기지만 진리)

1. 시뮬레이션이 잘 나와도 board에서 결과가 잘 안나오는 경우도 많은 것 같습니다 ( 그냥 단순히 제 잘못 일까요? )

이것이 해결하기 어려운 부분 중 하나인데, 많은 요인들이 뒤섞여서 발생합니다.

Simulation 에서 볼 수 있는 내부 회로 외의 다른 원인 (Mistake, CDC, oscillator, port noise etc..... ) 들 때문에 그럴 수 있습니다.

결론은 설계자의 잘못일 가능성이 크죠..

2. 이러한 상황에서 주실 수 있는 팁 혹은 맛비님의 검증 방법이 궁금합니다.

이 부분은 타인이 해결하기 어렵습니다... 만,

(회로 지식, 삽질, 노하우, 경험 etc 로 해결하셔야 합니다... 어떤 변수가 개입했는지 모르기 때문에 이론이 정립되어 있지 않음.)

많은 분들의 의견을 구하는 것도 좋은 방법입니다.

https://cafe.naver.com/plduser

3. 일반적으로 vivado tool 디버깅을 사용 하시나요?

Verilog HDL Season1 에서 전달드린 command line build 환경을 주로 사용합니다.

error 메세지 보고, 고치고 이런식으로요.

즐공하세요 :)

답변 1