Verilog ZYNQ Program 1 (Zynq mini 7020)

본 강의는 Xilinx ZYNQ 보드를 활용하는 내용입니다. 본 강의의 내용을 이해하면 Embedded_SW + User_Logic 을 이해하고 실무에 적용할 수 있는 스킬을 배우게 됩니다.

안녕하세요.

얼마전에 중지되었던

전자문서 (pdf 파일) 다운로드가 다시 가능해졌습니다.

인프런에서 강의를 구매하신 분들은

자료실에서 전자문서를 다운로드해서 활용하시길 바랍니다.감사합니다~!!

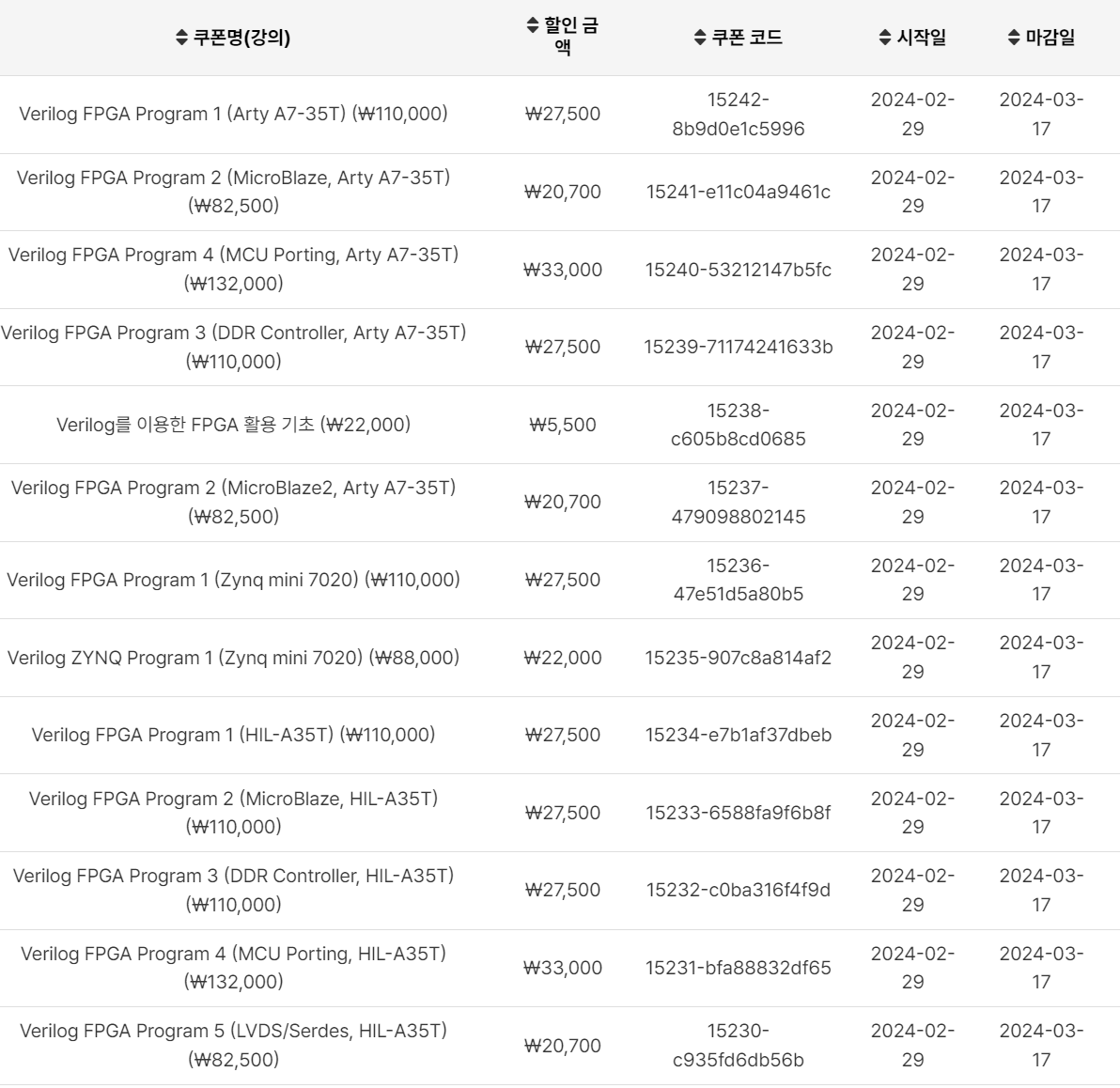

새학기를 맞이하여 강의 개별 구매 할인 이벤트를 진행합니다.

Verilog, FPGA를 배우고자 하시는 분들에게 좋은 기회가 되시길 바랍니다1. Verilog, FPGA 관련 강의 할인 이벤트

♣ 강의 25% 할인

♣ 기간 : 2024. 02. 29 ~ 2024. 03. 17

♣ 아래에 있는 할인쿠폰을 이용하여 인프런에서 구매2. HIL-A35 개발 보드 할인 이벤트

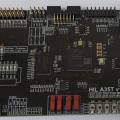

♣ 개발보드 15% 할인

♣ 기간 : 2024. 02. 29 ~ 2024. 03. 17

♣ 스마트스토어 : https://smartstore.naver.com/ihil감사합니다~!!

안녕하세요.

개발 보드 판매를 시작합니다.

아래 네이버 스마트스토어에서 구매하실 수 있습니다.

스마트스토어 링크 : https://smartstore.naver.com/ihil 개발보드 관련 자료는 아래 링크에서 다운로드할 수 있습니다.

개발보드 관련 자료는 아래 링크에서 다운로드할 수 있습니다.

매뉴얼과 테스트 프로그램(led, 버튼 동작)이 있습니다.

다운로드 링크 : http://naver.me/xJqtlt1TVerilog FPGA Program 1 (HIL-A35T)

Verilog FPGA Program 2 (MicroBlaze, HIL-A35T)

Verilog FPGA Program 3 (DDR Controller, HIL-A35T)

Verilog FPGA Program 4 (MCU Proting, HIL-A35T)

개발보드와 강의 통해 많은 도움이 되시길 바랍니다.

감사합니다 ~!!안녕하세요.

강의용 개발보드가 10월 말경에

네이버 스마트스토어를 통해 출시 예정입니다.개발보드에 맞게 기존의 강의도 새롭게 만들어서 오픈예정입니다.

강의가 개발보드에 따라 다양하게 구성됩니다.

HIL-A35T (자사 개발 보드, 출시 예정)

Verilog FPGA Program 1 (HIL-A35T)

Verilog FPGA Program 2 (MicroBlaze, HIL-A35T)

Verilog FPGA Program 3 (DDR Cotnroller, HIL-A35T)

Verilog FPGA Program 4 (MCU Porting, HIL-A35T)

Arty A7-35T (Digilent 개발 보드)

Verilog FPGA Program 1 (HIL-A35T)

Verilog FPGA Program 2 (MicroBlaze, HIL-A35T)

Verilog FPGA Program 2 (MicroBlaze2, HIL-A35T)

Verilog FPGA Program 3 (DDR Cotnroller, HIL-A35T)

Verilog FPGA Program 4 (MCU Porting, HIL-A35T)

Zynq mini 7020

Verilog FPGA Program 1 (Zynq mini 7020)

Verilog ZYNQ Program 1 (Zynq mini 7020)

Arty a7-35T, Zynq mini 7020 강의를 구매하신 분들에게는

HIL-A35T 강의를 초특가로 구매할 수 있도록 할 예정입니다.

그동안 개발보드로 인해 어려움이 있으신 분들에게

많은 도움이 될 수 있도록 노력하겠습니다.1차로 개발보드 수량은 50여개가 진행됩니다.

혹 필요하신 분들은 미리 연락주시면 감사하겠습니다.

가격은 18만원(부가세 별도) 정도 예상합니다.

(연락처 : alex@ihil.co.kr, 010-6243-0395)감사합니다~!!

강의가 업데이트 되었습니다.

강의명 : FPGA MicroBlaze 구현

업데이트 내용 : 4장, 5장 내용 새롭게 업데이트 됨.

강의를 구매하신 분은 자료실에서 다운받으시길 바랍니다.

추후 "FPGA MicroBlaze 구현" 강의는 계속해서 전체 내용이 업데이트 예정입니다.

감사합니다 ~!!

강의가 업데이트 되었습니다.

Verilog를 이용한 FPGA 활용 (v2.1)

NRZL Decoder 구현 내용(ch11)이 추가되었습니다.

FIFO 구현, 사용에 대한 중요한 내용입니다.

실무에 많은 도움이 될 것으로 기대합니다.

Verilog를 이용한 FPGA 활용 for Zynq (v1.2)

NRZL Decoder 구현 내용(ch14)이 추가되었습니다.

FIFO 구현, 사용에 대한 중요한 내용입니다.

실무에 많은 도움이 될 것으로 기대합니다.

강의를 구매하신 분들은 자료실에서 무료로 다운로드 받으시면 됩니다.

강의 통해 많은 도움 되시길 바랍니다.감사합니다.