인프런 커뮤니티 질문&답변

[Lab12] 시뮬레이션 결과([0:31]mem [0:511])에 질문있습니다.

작성

·

284

1

안녕하세요 맛비님!

Lab12 simulation 결과에 대해 궁금한점이 있습니다.

시뮬레이션 결과에서 BRAM의 [31:0] mem[0:511]을 보면 mem[0] 부터 mem[31]까지만 값이 보이고, 이후 mem[32]부터는 값이 보이지 않습니다. 즉 32bit 데이터 32개만 보입니다.

BIT크기의 문제인가 싶어서 8bit로 수정한 뒤 시뮬레이션을 돌린결과 128개만 보입니다.

두 경우 모두 bitwidth × memdepth = 1024로 동일한데, axi vip를 사용한 시뮬레이션의 경우 버퍼, 메모리등의 데이터를 보여주는데 개수의 한계가 존재하는건가요?

mem[0]부터 mem[511]까지 다 확인하고 싶은데 axi vip 테스트벤치의 코드를 수정하면 가능할까요? 가능하다면 어느 부분을 수정해야하나요!

답변 1

0

안녕하세요 :)

강의에서 다루지 못한 내용은 정확하게 답변드리기 어려운점 이해 부탁드립니다.

(제가 모든 것을 알고 있지 않아요 ㅠ 저도 같은 사람인지라 필요하면 찾아서 봅니다.)

코드를 수정하실 필요는 없을 것 같아요. 툴 문제로 예상됩니다.

시뮬레이션 툴 문서 링크입니다.

https://docs.xilinx.com/r/en-US/ug900-vivado-logic-simulation/Overview

==========================

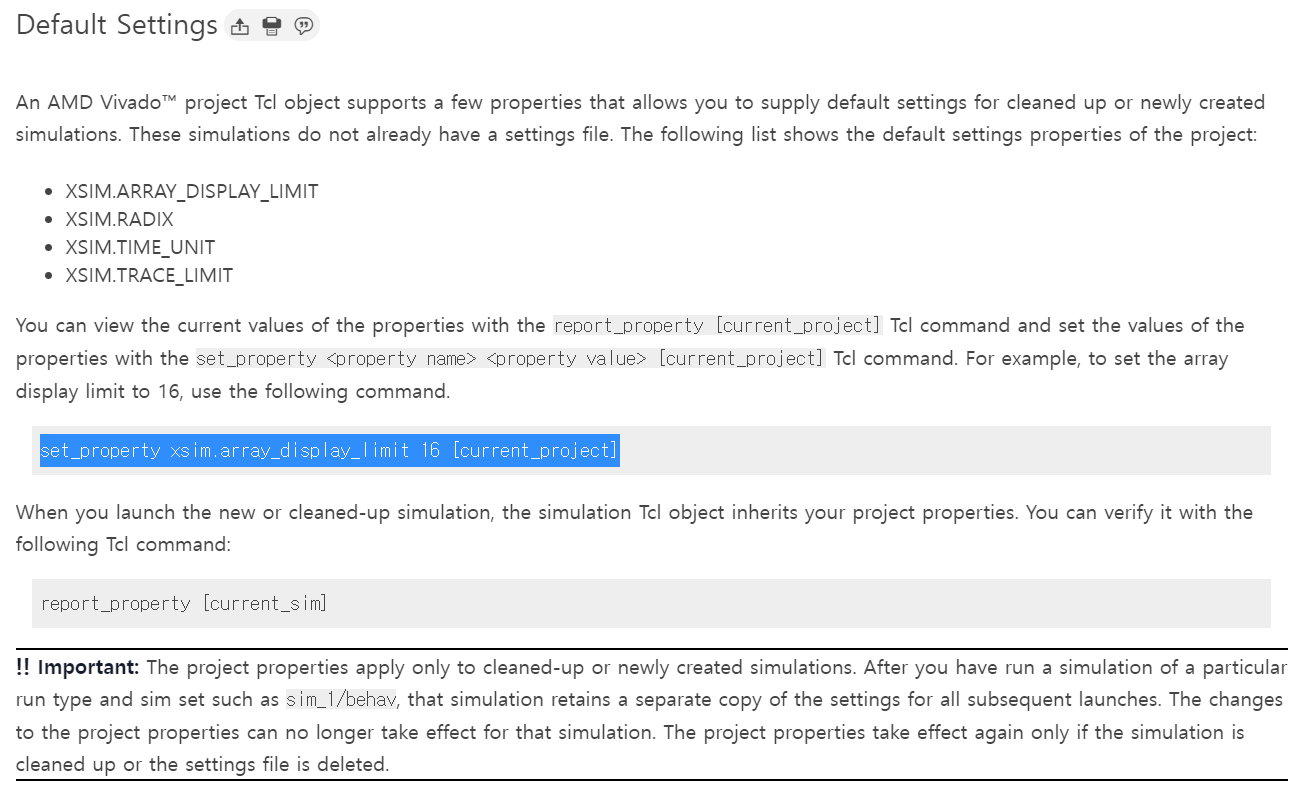

문서를 보다 보니, 현 상태에서 예상되는 이슈는 이것이 아닐까 생각이 드는데요.

확인 부탁드릴께요.

set_property xsim.array_display_limit 16 [current_project]https://docs.xilinx.com/r/en-US/ug900-vivado-logic-simulation/Default-Settings

==================

추가로 시뮬레이션 툴 이슈를 해결하시기 어려우시면,

Testbench 상에서, file dump 를 통해서 메모리 값을 확인하는 방법도 있습니다.

즐공하세요 :)