인프런 커뮤니티 질문&답변

HDL 11장 COUNTER의 관하여 질문이 있습니다.

작성

·

259

3

안녕하세요??

안녕하세요??

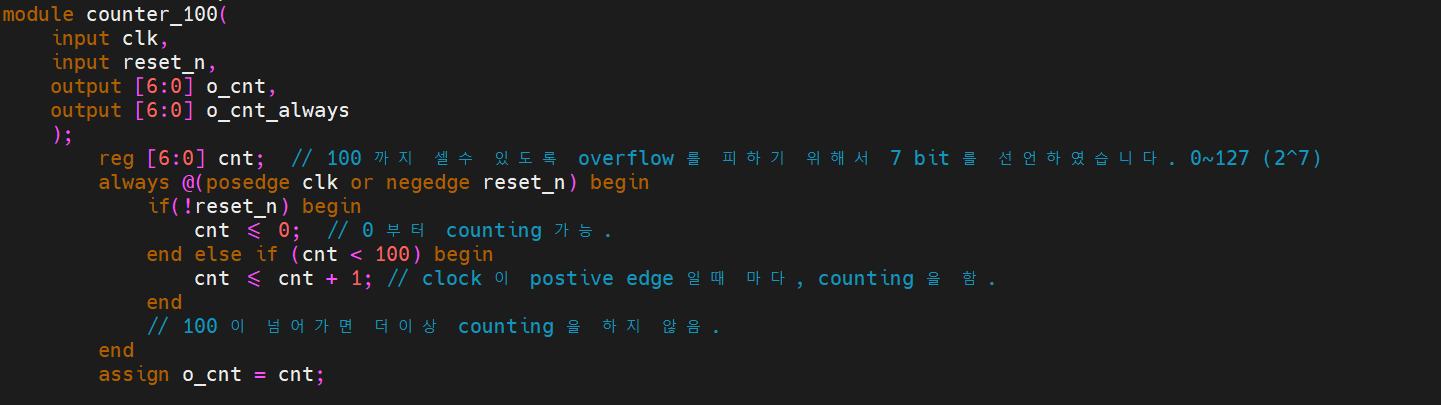

output [6:0] o_cnt; 이 부분을 따로 밑에서 assign o_cnt = cnt; 로 선언해주지 않고 output reg[6:0] o_cnt로 선언하여 밑에 적어 놓은 코드와 같이 변경을 해보았습니다.

module counter_100(

input clk, reset_n,

output reg [6:0] o_cnt

);

always@(posedge clk or negedge reset_n) begin

if(!reset_n) begin

o_cnt<= 0;

end else if (o_cnt <100 ) begin

o_cnt <= o_cnt + 1;

end

endmodule

이런 식으로 설계를 해도 되는 건지 궁금하여 여쭤봅니다.

감사합니다!.