인프런 커뮤니티 질문&답변

BRAM layency

작성

·

536

1

맛비님 안녕하세요 ! BRAM Ctrl 부분을 복습 도중 질문 사항이 생겨 글남기게 되었습니다.

강의와 다르게 비바도에서 직접 bram ip를 불러와서 테스트 벤치를 작성해보려고 했습니다.

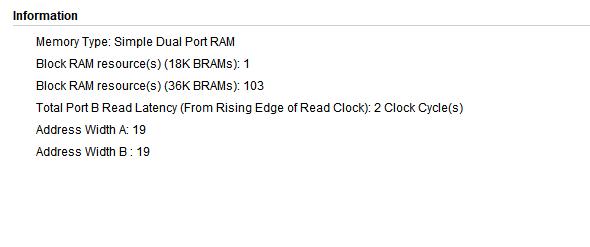

이때 Total Port B Read Latency가 2 clock cycle 이라고 나와있습니다.

이 경우에 제가 PORT A에서 DATA를 받아 메모리에 쓰고 B에서 OUTPUT를 통해 출력을 읽는데 2 Clock에 latency가 걸린다고 이해하면 되는지 궁금합니다.

(이것의 기준이 PORT A, B 의 clk가 같을때 얘기인지 궁금합니다.)

답변 1

0

안녕하세요 :)

정확한 답이 아닐 수 있음을 말씀드리고 적습니다.

문서가 정확할 것 같은데요.

https://docs.xilinx.com/v/u/en-US/pg058-blk-mem-gen (이거는 참고 링크 : https://support.xilinx.com/s/question/0D52E00006iHpRTSA0/how-to-work-withcontrol-bram-latency?language=en_US)

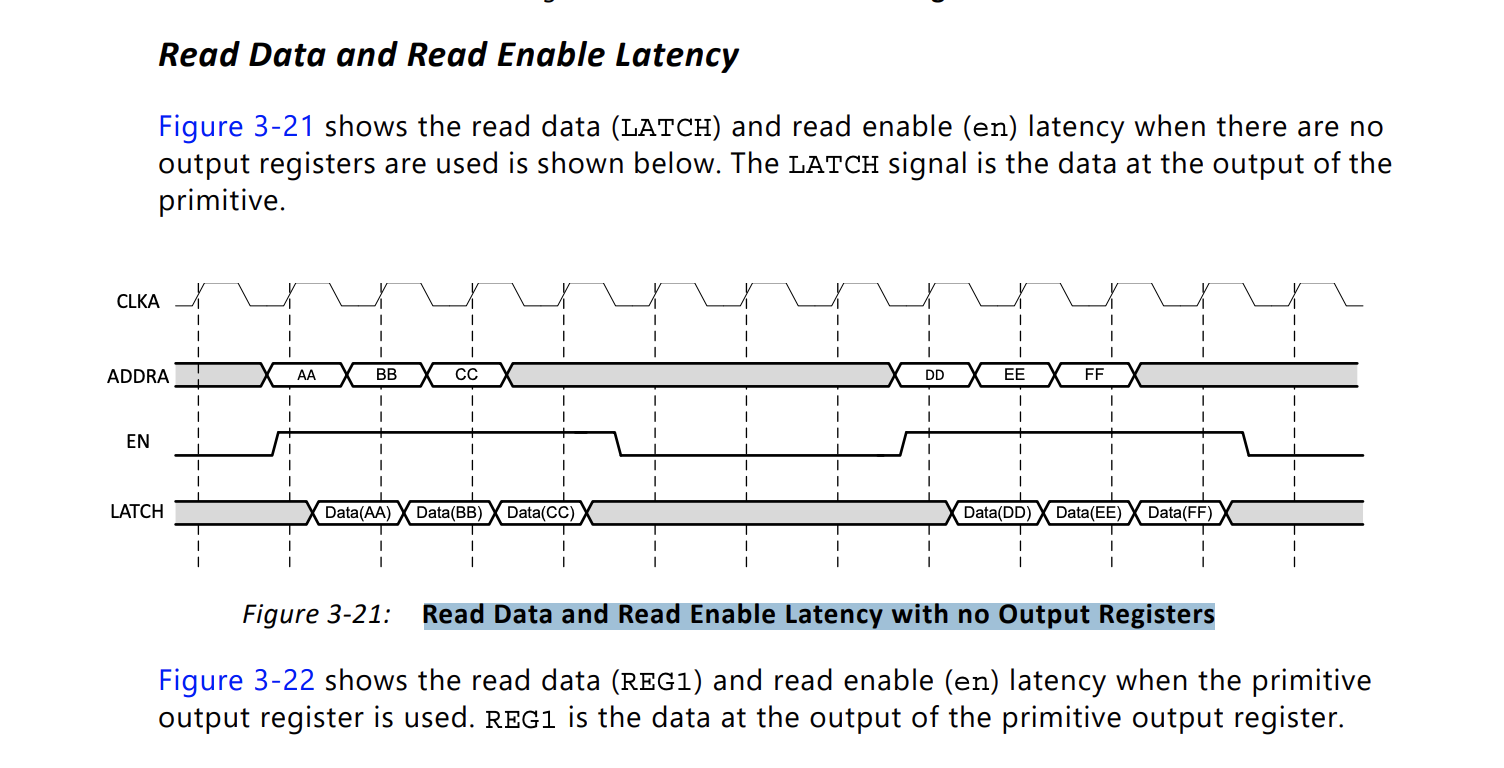

일반적으로 read latency 는 1cycle 뒤에 유효한 값이 나옵니다.

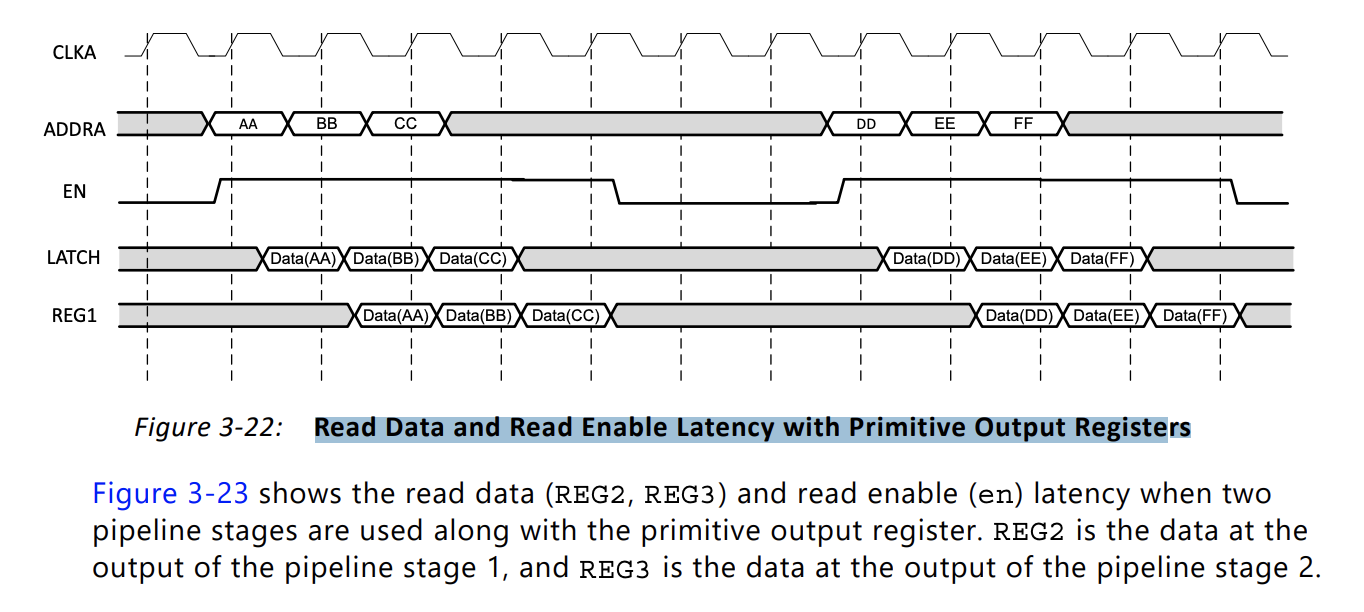

제 생각에 저 2 cycle 은 registered output 이 있는 경우. 즉 다음과 같은 Diagram 이지 않을까 예상합니다. REG1 의 출력.

제 생각에 저 2 cycle 은 registered output 이 있는 경우. 즉 다음과 같은 Diagram 이지 않을까 예상합니다. REG1 의 출력.

=======================

=======================

적어주신 내용은 BRAM 에 two port 에서 유효한 Data 를 쓰고 읽을 때의 latency 가 추가되어야 할 것 같아요.

이 경우에 제가 PORT A에서 DATA를 받아 메모리에 쓰고 B에서 OUTPUT를 통해 출력을 읽는데 2 Clock에 latency가 걸린다고 이해하면 되는지 궁금합니다.

이거는 유효한 Data (Port A 에 Write 한 Data 를 Port B 에서 Read 한다는 가정) 측면에서는 3 cycle 일 수 있겠다 생각이 드네요. Write 하는데 1 cycle + Read 2 cycle. 단순히 유효한 Data 가 아니라 막무가내? 로 읽고 싶다면 2 cycle 이 맞을 것 같아요.

즐공하세요 :)