인프런 커뮤니티 질문&답변

작성자 없음

작성자 정보가 삭제된 글입니다.

Timing constraints 관련 질문

해결된 질문

작성

·

882

·

수정됨

1

안녕하세요 맛비님

강의를 수강중 궁금함이 생겨서 질문 남겨드립니다.

[1번 질문]

chapter 5강을 수강하던 도중 timing constraint가 생겨 해당 critical path에 ff를 추가하여 문제를 해결하셨습니다.

제가 수정 전과 후 코드를 둘 다 implementation 수행하여 utilization report를 확인해 본 결과 다음과 같이 나온 것은 확인하였습니다.

<With timing constraints>

LUT : 1184

LUTRAM : 60

FF : 1054

BRAM : 8

<Without timing constraints>

LUT : 1185

LUTRAM : 60

FF : 1123

BRAM : 8

위와 같은 결과를 보고 어떻게 해석해야할지 모르겠습니다. ㅜㅜ

예를들어 추가한 플립플롭이 LUT 1개를 사용하고 해당 부분에 register가 69(1123-1054)개사용되는건지.. 아니면 다른 고려해야할 사항이 있는지 궁금합니다.

[2번 질문]

timing constraints 해결 전 후 퍼포먼스 차이가 거의 없고, latency만 1 증가 했을 뿐 throughput은 동일하다고 말씀하셨습니다.

퍼포먼스 차이가 거의 없다는 말이 [1번 질문] 에서와 같이 하드웨어 자원 사용량이나 power 소비부분에서 크게 차이가 없다는 말인지,

혹은 vitis 상에서 보드와 연결해 빌드를 하였을 때 소요되는 시간이나 clock수의 차이가 얼마 안난다는 말인지 구체적으로 모르겠습니다 ㅜㅜ

추가로 latency와 throughput은 이론적으로 잘 이해가 되었습니다. 다만 눈으로 확인할 수 있는 방법이 있는지 궁금합니다 !

[3번 질문]

제가 timing constraints가 발생한 버전과, 이를 해결한 버전 모두를 generate bitstream하여 VITIS상에서 보드에 올려 빌드해 보았습니다.

실행 전에 가설로는 timing constraints가 발생한 버전에서는 VITIS에서 구동이 되지 않을거라 생각했는데, 예상과 달리 결과값까지 잘 출력되었습니다.

여기서 의문점이 생긴 것이 FPGA보드상에서 timing constraints가 존재하는 모듈이 왜 잘 돌아가는지, 해결하지 않을 경우 나중에 어떤 단계에서 무슨 문제가 발생하는지 궁금합니다.

[4번 질문]

BRAM의 data width = 32bit로 설정하셨는데 특별한 이유가 있는지 궁금합니다. 혹시 axi4_lite가 32bit로 제한 또는 제안되기 때문인가요?

또한 실습에서 사용하신 dual port bram의 width 최대 사이즈가 몇인지 어떻게 확인할 수 있을까요!

제가 찾아본 바로는

여기서는 72 bit인 것 같고..

여기서는 72 bit인 것 같고..

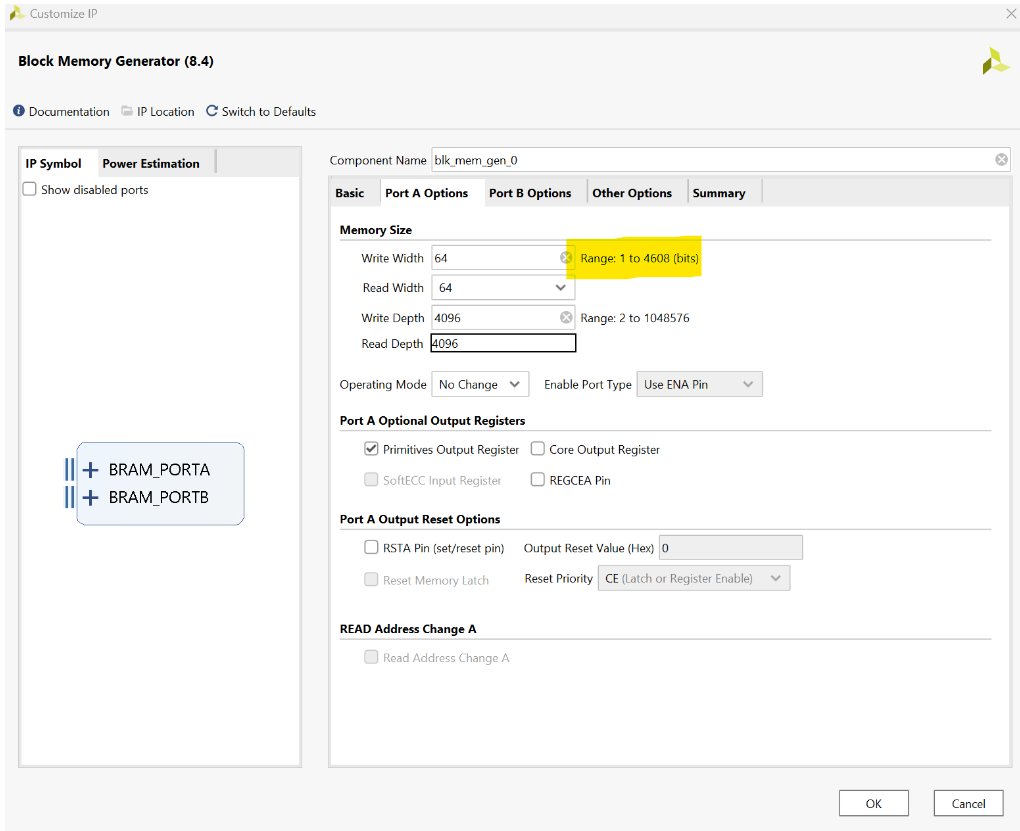

여기서는 range가 최대 4608이라고 나와있어서 뭐가 뭔지 도통 헷갈립니다..ㅠㅠ

여기서는 range가 최대 4608이라고 나와있어서 뭐가 뭔지 도통 헷갈립니다..ㅠㅠ

[마지막 질문]

마지막으로 input의 갯수를 4096개로 설정하신 이유가 궁금합니다 !

또한 output도 4096개를 만드는게 여러 딥러닝 모델에서 채택하고 있기 때문인가요 ?

항상 꼼곰하고 좋은 강의 올려주셔서 감사합니다 !

답변 1

0

안녕하세요 :)

각설하고 답변드리겠습니다.

[1번 답변]

chapter 5강을 수강하던 도중 timing constraint가 생겨 해당 critical path에 ff를 추가하여 문제를 해결하셨습니다.

혹시 제 영상에서 어느 부분 (몇분정도) 인지 알려주실 수 있을까요? (강의내용이 너무 많아져서 기억력이.. ㅠ.ㅠ)

5강부터 timing 이슈가 될 부분이 나왔을까..?; 싶어서요.

F/F 추가로 인한, Util 사용량은, 동일 옵션 으로 코드만 수정하여 implementation 하셨다면, 따져봐야 할 것 같은데요.

왜 Util 이 다른가? 의 답변은 같은 .v 코드라도 Vivado 버전에 따라 Implementation 환경이 달라질 수 있기에, (로직 추가로 인한 util 증가의 경향치는 유사하겠지만) 정확하게는 답변을 못달겠습니다.

[2번 답변]

이 질문은 5강 외에도 전체 개념에 포함이 되어서, 설명이 가능할 것 같은데요.

latency 와 throughput 을 알고계신다고 하니, 답변드리겠습니다.

로직의 전체 Performance 를 결정하는 것은 throughput 입니다. latency 는 초기 output 이 나오는 시점을 결정하고요. F/F 을 data path 에 추가하면, 1 cycle 뒤에 output 이 나오죠. latency 가 1증가하였다. 하지만 throughput 이 변하는 건 아닙니다.

정리하면, throughput 을 performance 로 생각하시면 되겠습니다.

[3번 답변]

timing constraint 가, 문맥상 Timing violation 으로 해석이 되는데요.

이 두개가 다른의미 이기 때문에, Timing violation 이라고 생각하고 답변드리겠습니다.

제가 알기로는 Timing violation 이 발생하여도 동작할 수 있습니다. (두둥..)

timing violation 이 발생한 path 가 전체 동작에 영향을 주지 않는경우

Tool 의 보수적인 정책으로, Timing violation 값이 전체 clock frequency 대비 크지 않은 경우

이정도로 정리가 될 것 같아요.

제 답변은 잘 돌아가도 Timing violation 이 발생한 Bitstream 을 사용하지 말자 입니다.

어떤 문제가 일어나냐..? 언제 발생할지 모를 오동작이겠죠. 제품이라면 시한폭탄을 만드셨다 생각하시면 되겠습니다.

[4번 질문]

AXI4-Lite 의 Data bit width 와 같게 하려고, 32 bit 을 사용했습니다.

primitive cell 의 최대 size 가 72 bit 이라고 해여도, primitive cell 을 확장하여 연결할 수 있죠.

dual port bram의 width 최대 사이즈 -> FPGA 가 가능한 bram 의 resource와. Timing Violation 이 발생하지 않는 범위의 width 사용이 가능하다. (직접 해보셔야 알 수 있어요)

dual port bram의 width 최대 사이즈 -> FPGA 가 가능한 bram 의 resource와. Timing Violation 이 발생하지 않는 범위의 width 사용이 가능하다. (직접 해보셔야 알 수 있어요)

[마지막 질문]

네 맞습니다.

즐공하세요 :)

저는 방법만 알려드릴뿐, 직접 해보시기를 권해드립니다.

우리는 그렇게 약하지 않아요. :)

A1. 제 생각은 이미 설명드렸고, 이 부분은 정확한 이유는 모르겠습니다. 확실한건 비교해서 보시면 될 것 같아요. :)

A4.1

AXI4-Lite has a fixed data bus width and all transactions are the same width as the data bus. The data bus width must be, either 32-bits or 64-bits. ARM expects that: the majority of components use a 32-bit interface.

숫자의 질문은 스펙문서 참고 부탁드립니다. chatGPT 가 된 느낌, 노력의 문제라고 봅니다. :)

https://developer.arm.com/documentation/ihi0022/e/AMBA-AXI4-Lite-Interface-Specification/AMBA-AXI4-Lite/Definition-of-AXI4-Lite/Bus-width?lang=en

A4.2 맞습니다. (primitive cell 을 여러개 사용하면 되니까요)

A4.3 GUI 상에서 4096 이상 미지원이면 GUI 상에서는 안되는겁니다. 우리에게는 GUI 가 아닌, Verilog HDL 이 있습니다. 만들어서 쓰면 된다는 이야기 입니다. MAX 값은 직접 해보셔요. Zybo 말고 더 좋은 FPGA 에서 제가 4096 이상은 써본적이 있는 것 같긴합니다. (대략 기억은 잘.. 나질 않습니다.)

A4.4 AXI 의 Max Data bit width 를 사용하시는게 좋아보입니다. (최고의 Performance 를 고려한다면, 대신 area 증가함) AMBA 문서를 참고 부탁드립니다.

추가로 이거는 알려드려야할 것 같아서, 위의 이야기는 ideal 한 이야기고요.

Zybo 에서 사용하는 FPGA Chip set 의 AXI Max bit width 은 64 bit 입니다. Verilog HDL Season2 에서 이와같은 이유로 64bit 으로 설계하고 있어요. 현업에서 Bandwidth 를 많이 필요로 하는 경우 128, 256, 512b 등등 크게 씁니다. bit width 변경하는건.. 그렇게 어려운 문제는 아니라고 봐요.

즐공하세요 :)