인프런 커뮤니티 질문&답변

작성자 없음

작성자 정보가 삭제된 글입니다.

Vitis run -> memory read 오류

해결된 질문

작성

·

539

1

안녕하세요 좋은 강의 잘 보고 있습니다.

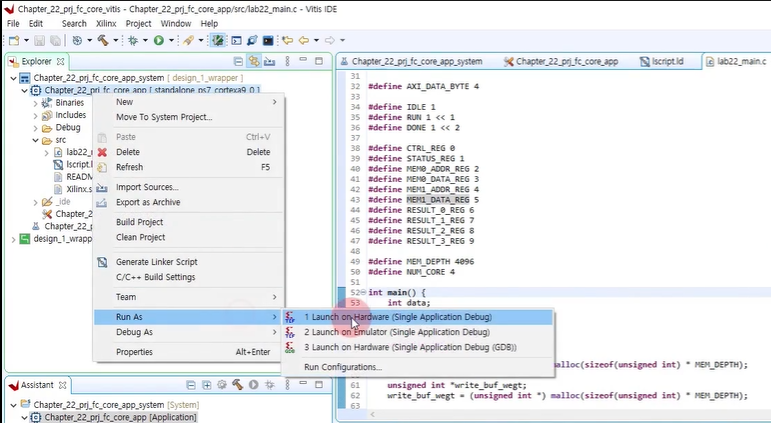

다름이 아니라 [FPGA 22장] 프로젝트 Fully Connected Layer 설계 - 실습편을 진행하던 도중

아래 사진과 같이 vitis 상에서 에러가 발생하여 질문 드립니다.

해당 과정을 수행하면

해당 과정을 수행하면

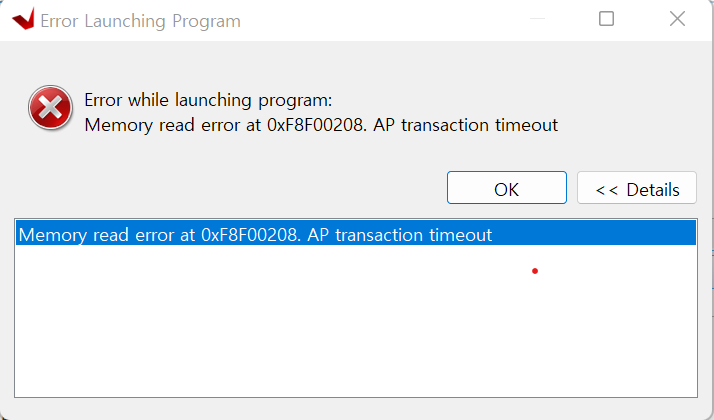

위와 같은 에러가 나오는데 구글링을 해보아도 마땅한 해결방안을 찾지 못하겠습니다.

제가 사용하는 보드가 pynq-z2 보드인데 zybo 보드와 호완 가능한 것으로 알고 있습니다.

혹시 보드가 달라서 생기는 문제라면 개인적으로 해결해보겠습니다.

즐거운 연휴 보내세요.

감사합니다.

답변 1

0

안녕하세요 :)

알고계신대로 pynq-z2 라면 zybo z7 20 과 완벽하게 동일한 chip 을 사용하기 때문에 문제가 없으리라 판단됩니다.

UART 로 LED 깜박이기만 클리어 하셨다면 발생하신 문제는 Zybo 에서도 발생하였을 것 같아요.

22장에서 이 Error 를 보셨다면, 이전의 장들은 어떻게 해결하셨는지가.. 용하네요.

===========================

SW 컴파일이 잘되어서, bitstream 이 올라가고 실행한 이후에 저 메세지가 발생할까요?

정확한 원인은 모르겠지만, 유추를 해보자면 SW 코드와 HW 간의 address miss 가 의심이 됩니다.

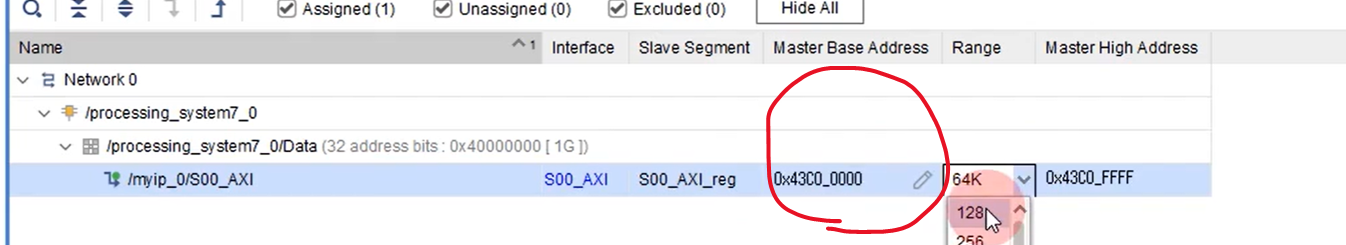

일예입니다. (base addr 를 질문자님과 제가 다를 수 있어요)

HW 상의 baseaddr

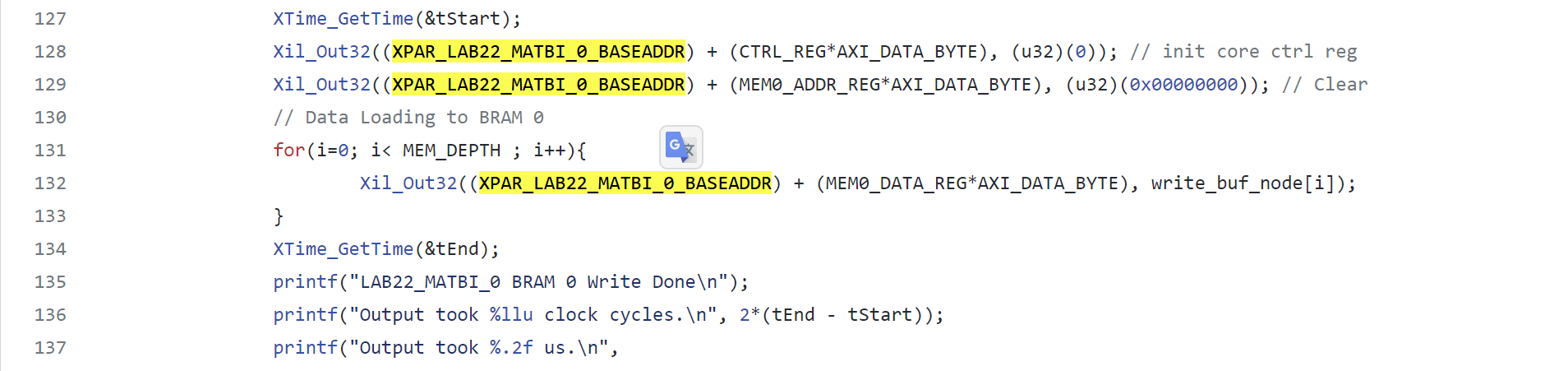

SW 상의 baseaddr

XPAR_LAB22_MATBI_0_BASEADDR 의 define 의 baseaddr

HW == SW 가 일치해야 할 것 같습니다.

확인 부탁드릴께요.