인프런 커뮤니티 질문&답변

fpga led제어 질문사항[강의 29분 01초 부분 ]

해결된 질문

작성

·

515

1

맛비님께,

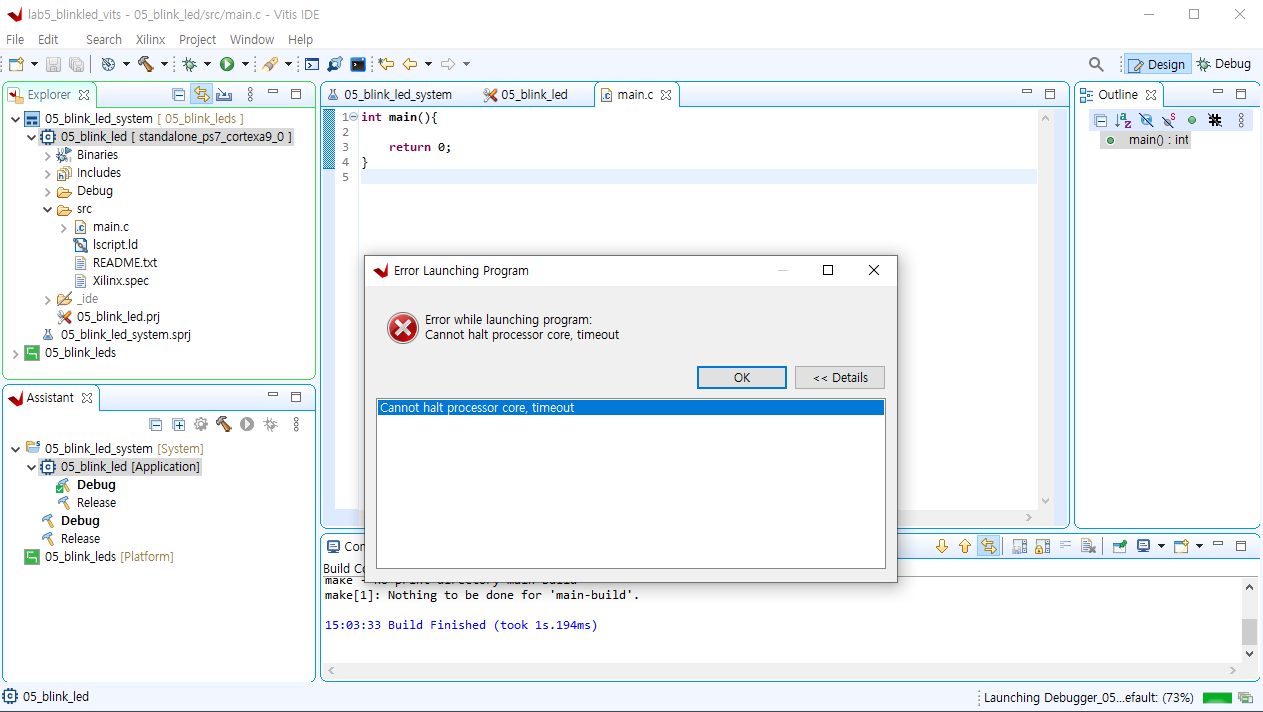

안녕하세요 fpga부분에서 vitis부분에서 PS부분에 dummy code를 올릴 때 아래와 같은 error로그가 나와서 질문드립니다!

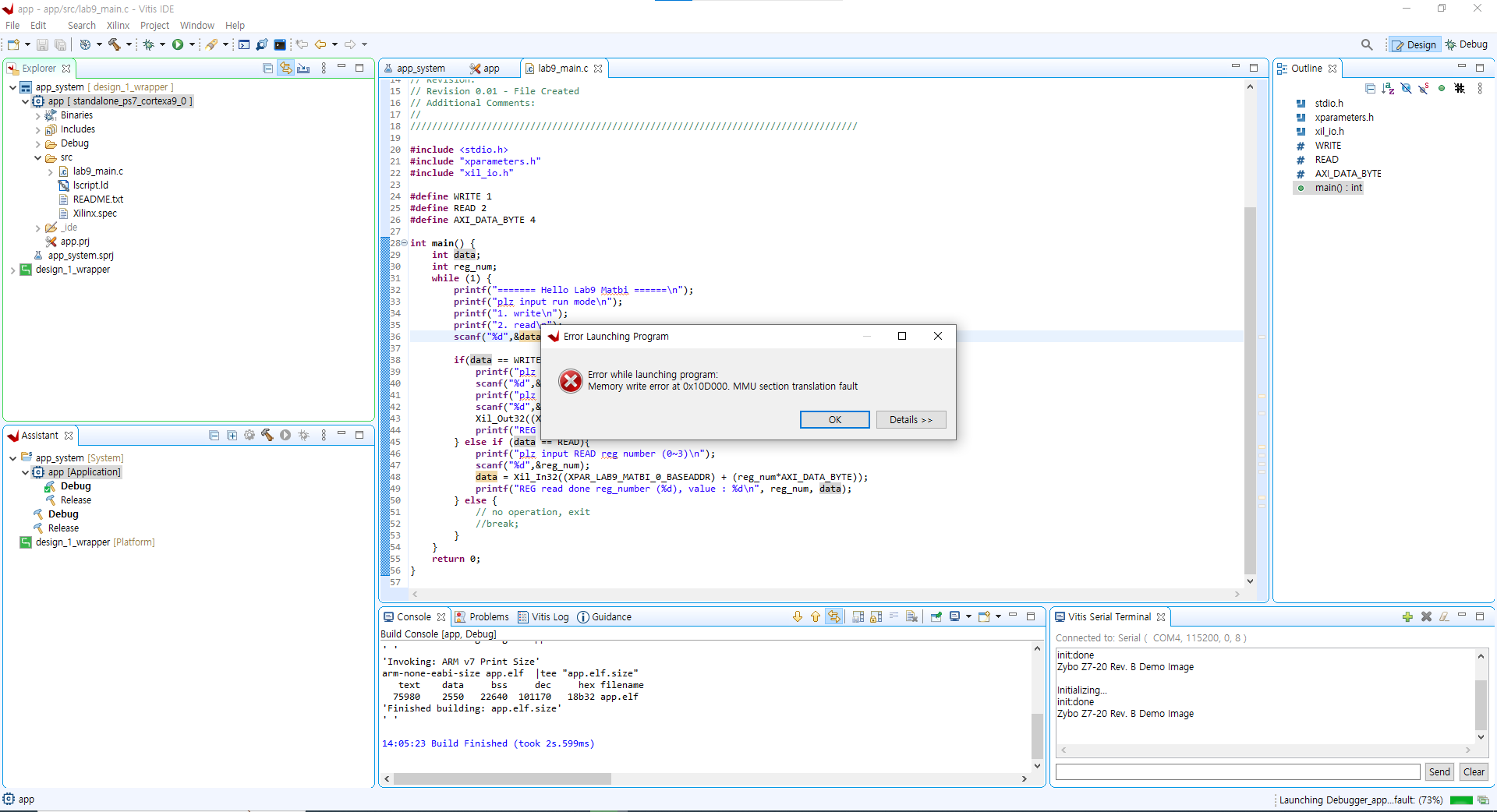

위 error log를 고려해보았지만 ip wrapping을 할때 axi를 activation하지도 않았는데 위 error로그가 나오는데 있어 문제가 발생하여 질문드립니다.

답변 2

0

신성곤

질문자

동일한 zybo z7-20 입니다! 현재 axi lite led _ blink 실습에도 동일한 에러가 뜹니다 !

에러가 공유해주신 source code에서도 떠서 board 문제인 것인가 생각했는데, 처음 led제어할때는 문제가 없었어서

디버깅이 잘 안되고 있습니다!

0

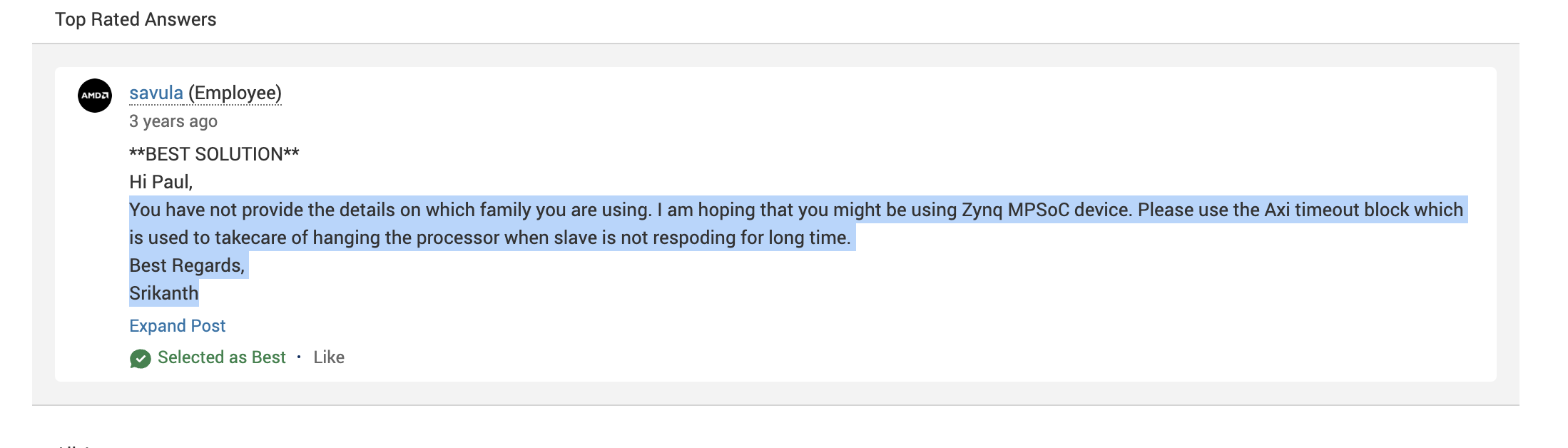

올려주신 링크에 이런말이 Best 로 올라가 있더라고요.

올려주신 링크에 이런말이 Best 로 올라가 있더라고요.

물리적으로는,

실행시, 보드가 pc 에 usb 로 연결이 잘 되었을까요?

그리고 강의 1장 잘 되신 건 맞는걸까요?

============================

주중에 해결이 안되시면, 제가 주말에 해보려고 하는데요.

사용하신 Vitis Tool 버전 남겨주시겠어요?