인프런 커뮤니티 질문&답변

axi4-lite -> axi4

작성

·

465

0

안녕하세요 맛비님.

강의를 복습하며 과제로 내주신

axi4-lite를 axi4로 upgrade하는 작업을 수행중에 있습니다.

질문은, lab10. fsm_counter with axi4_lite와 같이

메모리가 아닌 ip와 연결된 모듈도 axi4를 사용할 수 있는지?

아니면 axi4는 burst transaction 특성 때문에 메모리와만 연결할 수 있는지?

lab10_rev. fsm_counter with axi4로도 변형이 가능한 것인지?

입니다. (모두 같은 질문입니다.)

이 부분에 대해 판단이 어려워, 아주 간단히 개념적으로 여부를 여쭙고 싶어 글 드립니다.

행복한 추석 되시고, 추석 끝나신 편안한 시간에 답변 주시면 감사하겠습니다.

좋은 추석 되셨기를 빕니다. :) 복 많이 받으세요. 감사합니다.

(추가)

axi4_lite와 달리 axi4에서는 slv_reg0가 없어서,

관련된 개념을 이해를 하려고 노력하다보니,

혹시 개념적으로 다른건가 싶어서 생각이 들었습니다!

https://support.xilinx.com/s/article/1053914?language=en_US

답변 1

0

안녕하세요 :)

질문은, lab10. fsm_counter with axi4_lite와 같이

메모리가 아닌 ip와 연결된 모듈도 axi4를 사용할 수 있는지?

axi4 에 맞게 고치셔야죠? axi4_lite, axi4 는 다른 Port list를 가집니다.

바로 연결하시려면 convert 모듈이 필요할 것 같아요.

아니면 axi4는 burst transaction 특성 때문에 메모리와만 연결할 수 있는지?

lab10_rev. fsm_counter with axi4로도 변형이 가능한 것인지?

입니다. (모두 같은 질문입니다.)

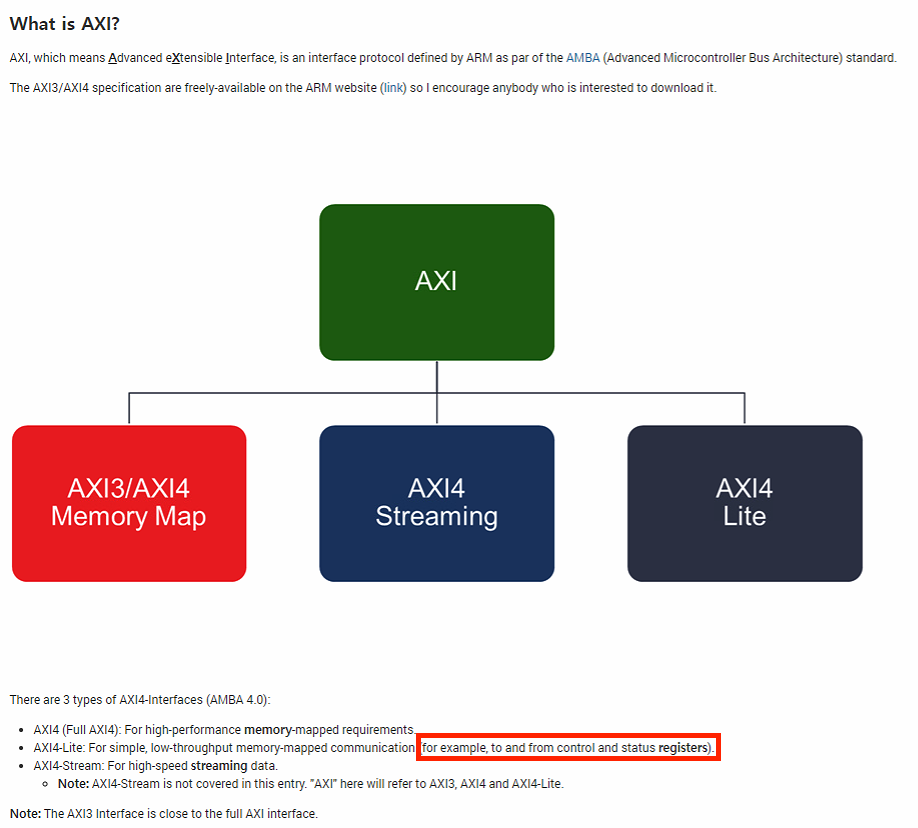

AMBA I/F 입니다. 목적에 맞게 사용하면 됩니다. AXI 를 공부하시면 답이 되실꺼에요.

당연히 변형 가능합니다. 응용의 문제입니다.

axi4_lite와 달리 axi4에서는 slv_reg0가 없어서,

관련된 개념을 이해를 하려고 노력하다보니,

혹시 개념적으로 다른건가 싶어서 생각이 들었습니다!

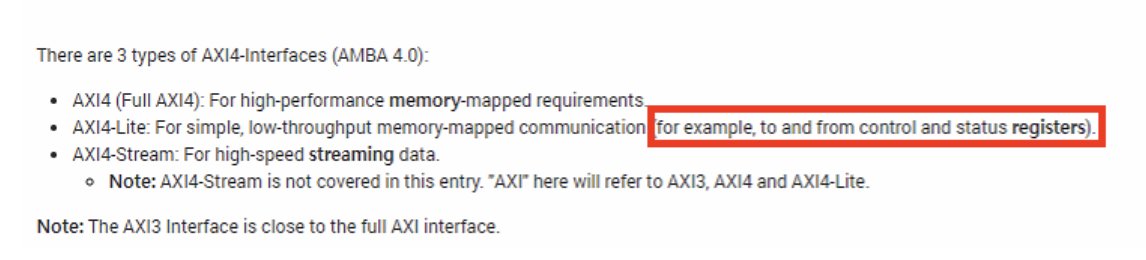

AMBA 입니다. 설계자가 AXI4 로 data 를 저장하는 주체가 F/F 이라면 reg 에 저장 할 수 있습니다.

다만, reg 라는 저장 공간 자체가 비싼 (Verilog HDL 에서 메모리 이론 부분 참고) 것이기 때문에, 고속 I/F 를 사용하기에는 적합하지 않죠. 고속은 곧 많은 양을 의미할테니까요.

캡쳐해주신 그림처럼, 아래 용도로 쓰자는 일반적인 룰이고요. 그렇다고해서 AXI4 라고해서 reg 사용하지 못하느냐는 아닙니다. data 를 주고 받기위한 I/F Bus Protocol 입니다. 주고받는 목적지는 설계자가 정할 수 있는 영역입니다.

즐공하세요 :)

즐공하세요 :)