인프런 커뮤니티 질문&답변

FPGA 9장 - AXI4_lite 테스트 관련 질문 있습니다.

작성

·

334

1

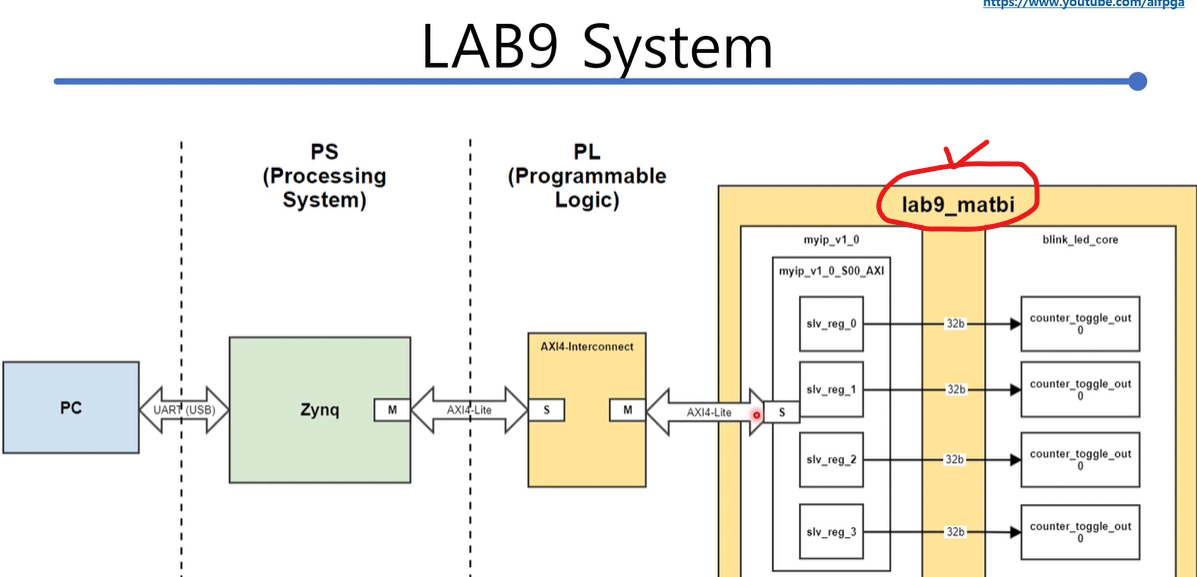

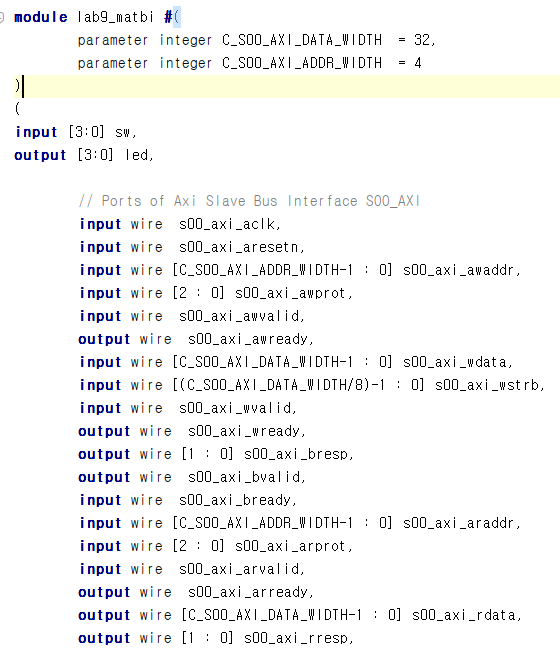

FPGA 9장 - AXI4_lite를 이용한 LED 점등 단원 입니다.

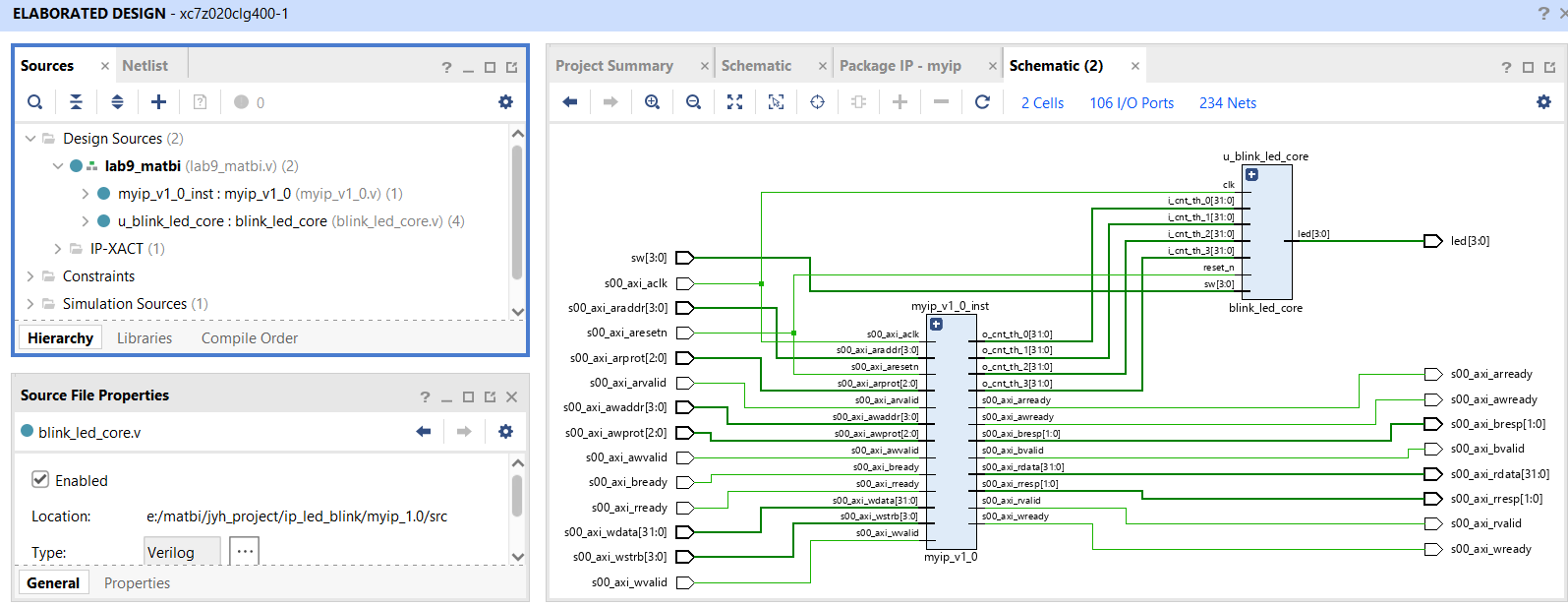

충분한 검증을 거친 후 보드에 올려보기 위해

위의 전체 시스템을 테스트 해보기 위한 테스트 벤치 파일을 만들어 보고자 했습니다.

그러나, 위와 같이 AXI4_lite와 관련된 모든 input을 생성해주긴 어렵다고 판단하였습니다.

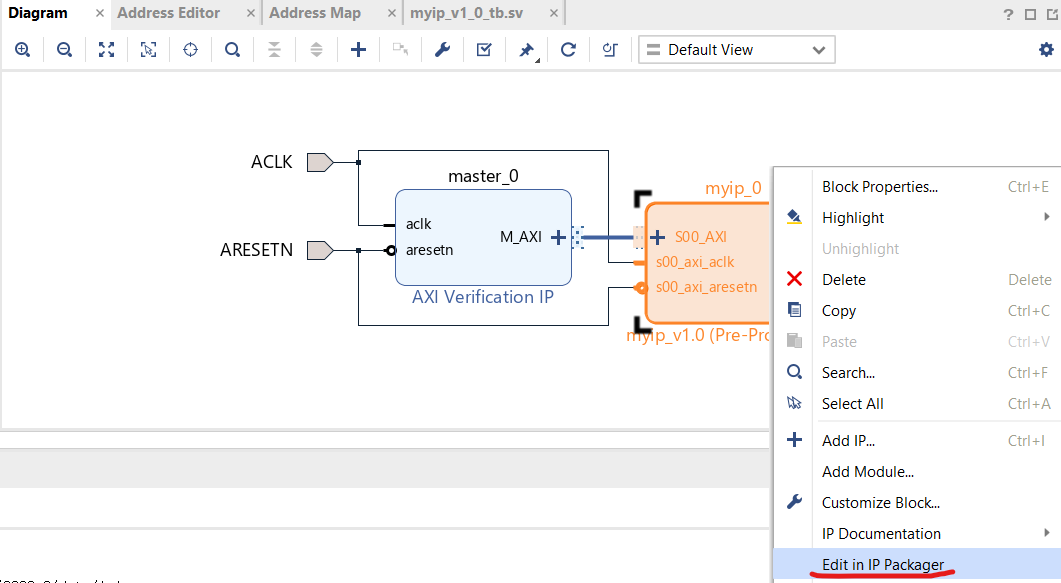

다른 단원의 강의를 찾아 보던중, FPGA 12장에서 VIP를 사용하여 '나만의 ip에 대한' AXI4_lite를 테스트 하는 방법을 보았습니다.

1. VIP를 이용하여 제가 만든 lab9_matbi의 ip를 테스트 하는 방법이 맞는 방법인가요?

맞다는 가정하에 프로젝트를 진행 해보았습니다.

1. VIP 만들고 edit ip packager

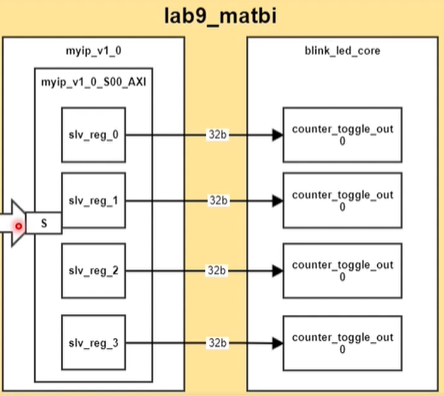

2. 파일들 추가한 후 schematic 확인

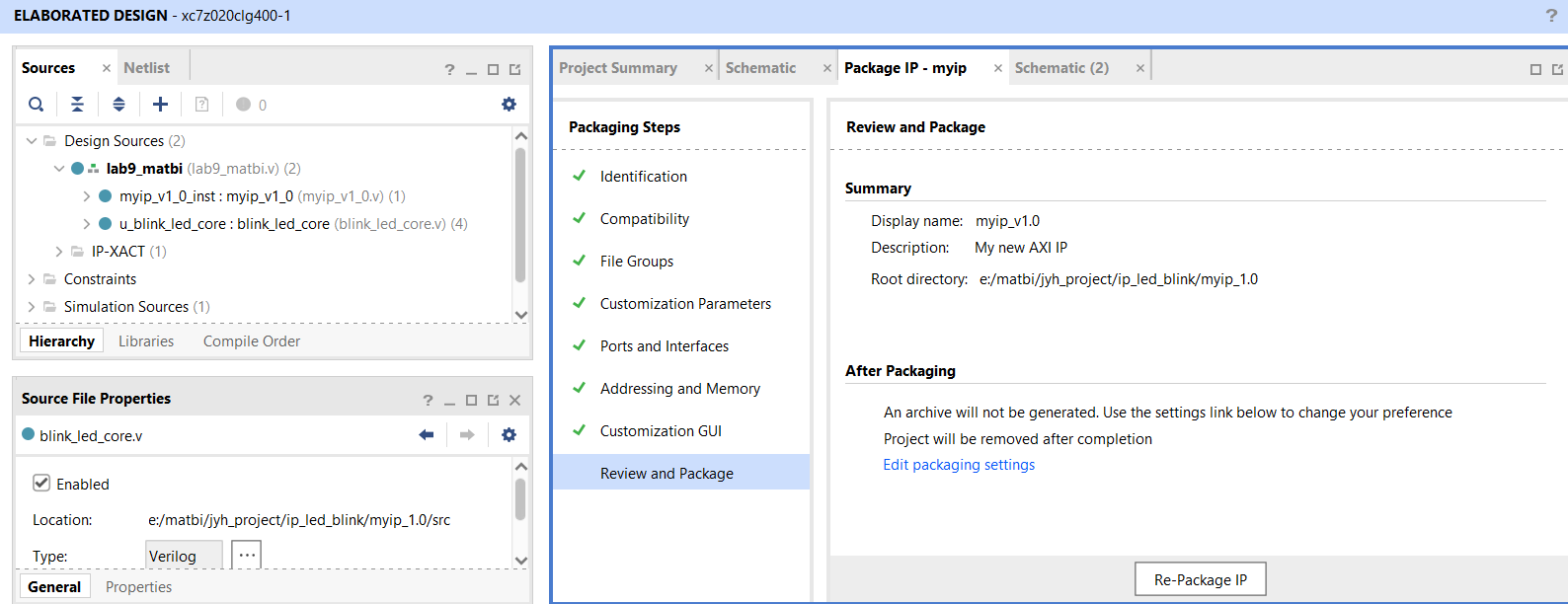

3. 업데이트 후 re-package

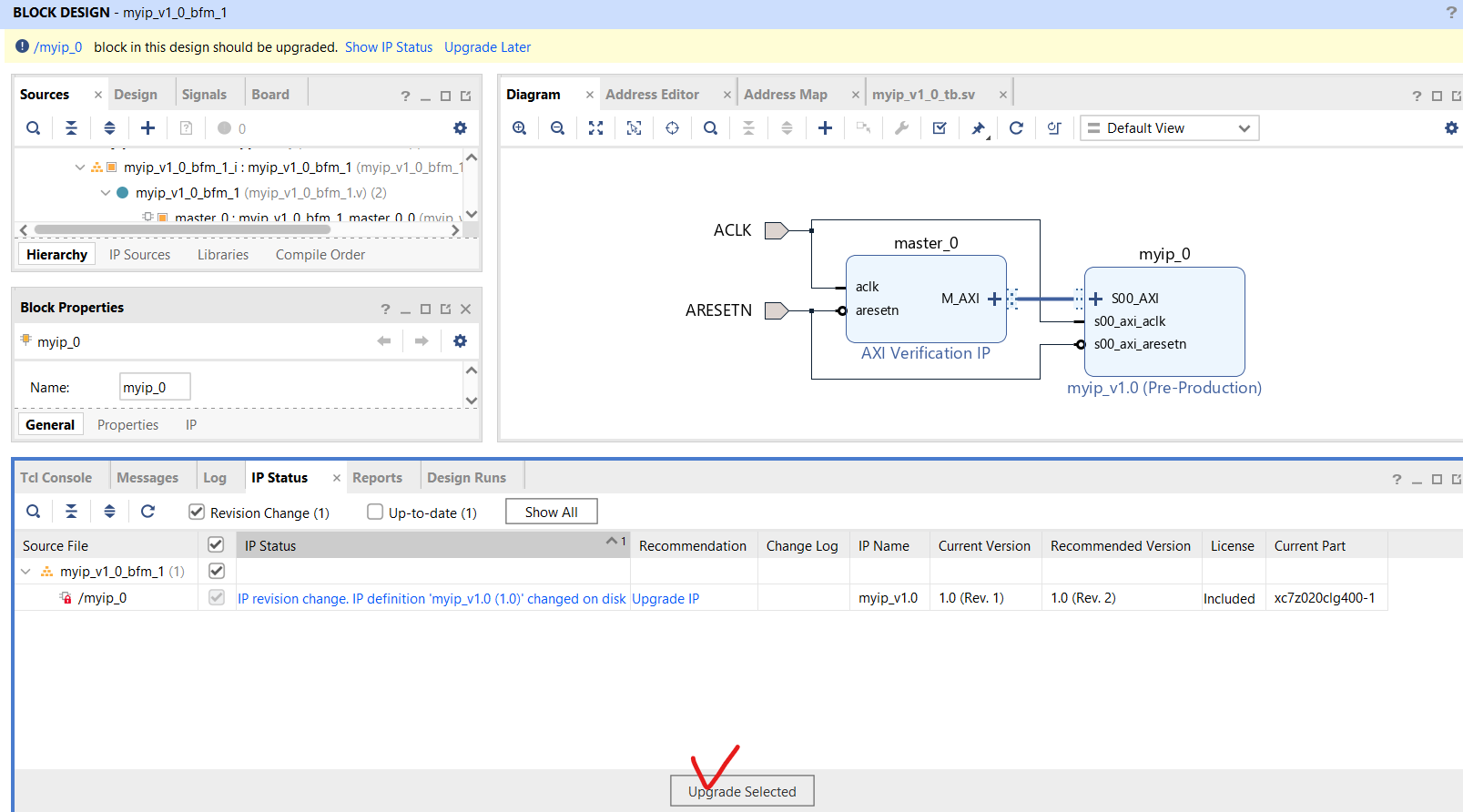

4. 원래 프로젝트로 돌아와서 upgrade ip

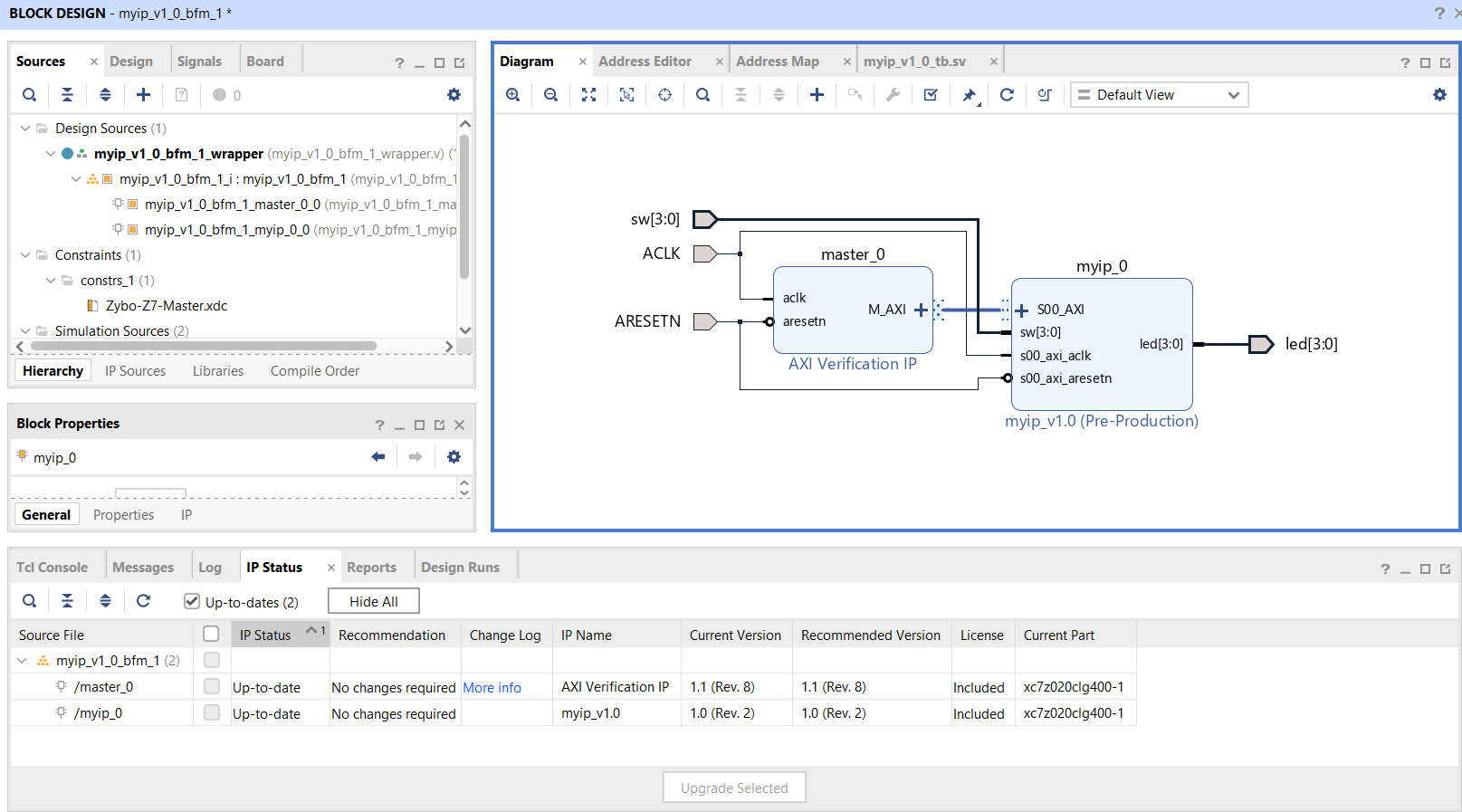

5. 생성된 block diagram 확인 ( sw, led의 연결선은 제가 추가하였습니다 )

이후, 생성된 tb.sv 파일에서 스위치(sw)입력, AXI4_lite를 이용하여 reg1,2,3,4에 write 해줄 값을 system verilog로 적어줘야 하는것 같아서 여기까지만 진행 하였습니다.

2. 제가 진행한 방법이 맞는지, 이후 sv 파일을 수정하면 되는것인지 궁금합니다.

혹시 아니라면, 단순하게

3. AXI4_lite를 제외하고, 위의 lab9_matbi 모듈에 대한 테스트 벤치만 만들어서 확인하는게 일반적인지 궁금합니다.

크게 아는건 없는데 너무 긴 질문을 드려서 죄송합니다.

정말 더워지는 날씨지만 몸 건강히 잘 지내시길 바랍니다 맛비님!