인프런 커뮤니티 질문&답변

합성된 이후, 원하는 신호에 대해 ILA처럼 Probe를 하는 방법

작성

·

1.8K

1

안녕하세요. 강의 너무 재미있고 도움되게 듣고 있습니다.

13강 bram과 관련된 부분에 대해 복습중입니다.

한가지만 짧게 여쭙고 싶습니다. (혹시 답변이 가능하지 않은 범위라면, 괜찮습니다.)

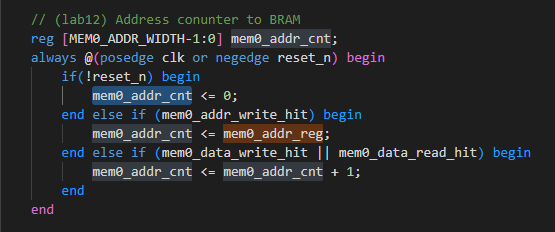

BRAM에 들어가는 Addr을 관찰하고 싶어서

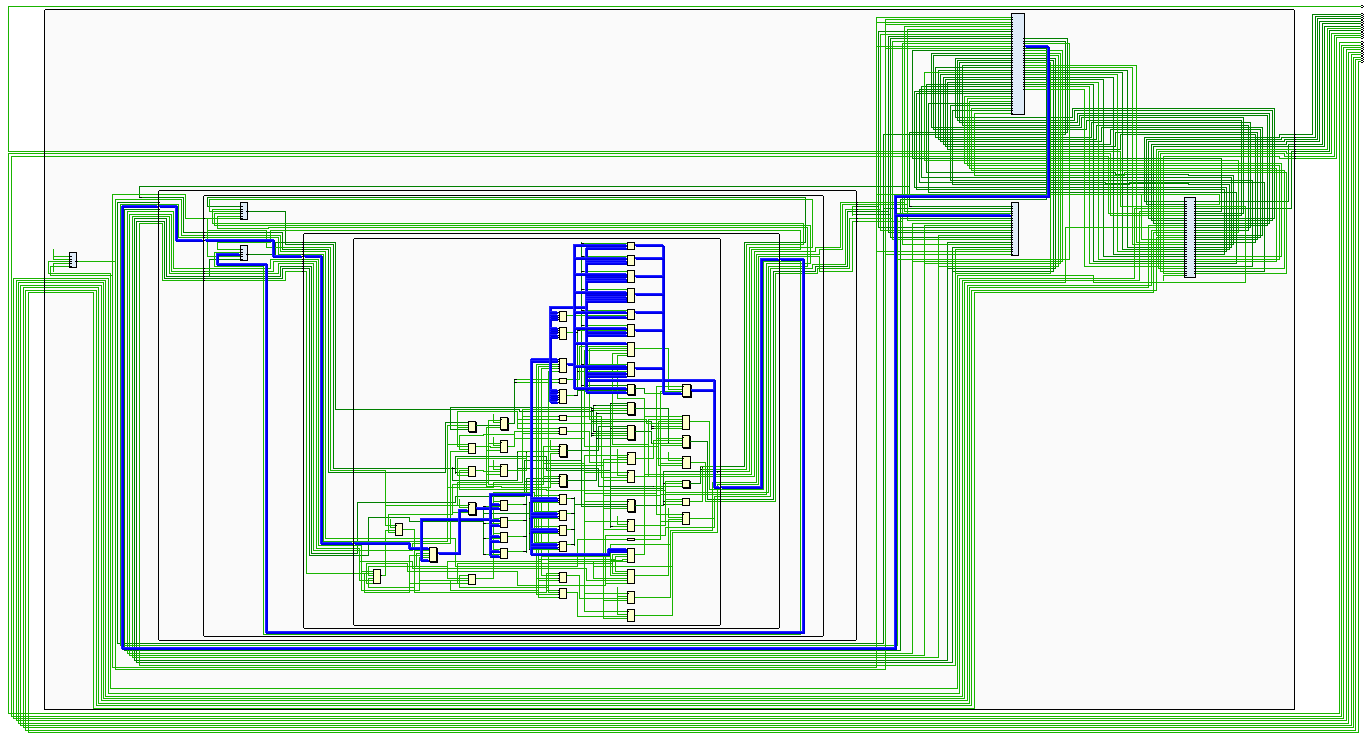

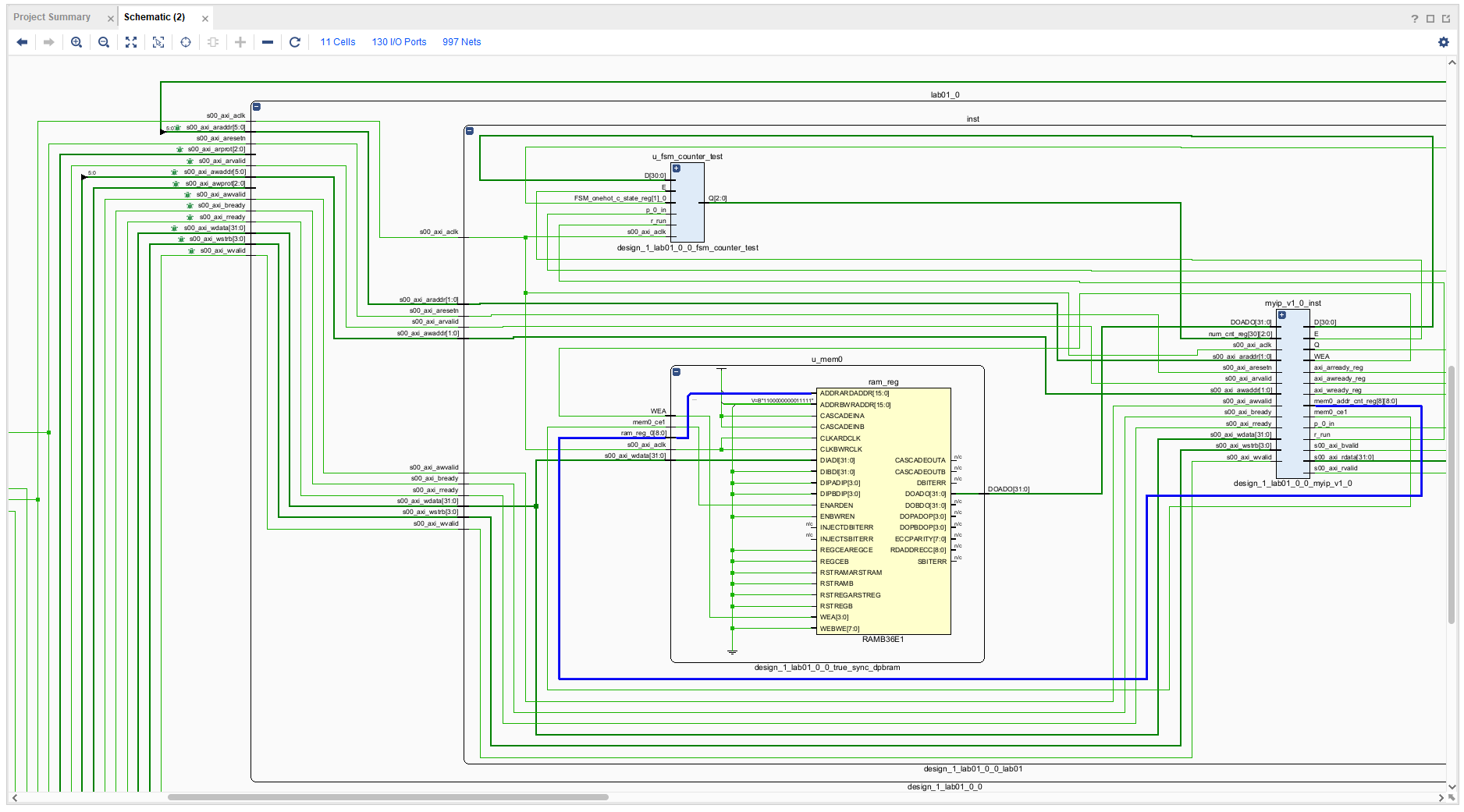

HW코드 및 Vivado Schematic을 분석해서, ADDRARDADDR이 그 Signal임은 발견하였는데

해당 Primitive Cell의 Signal에 [1]Waveform을 보거나 [2]Printf 로그를 찍을 수 있는 방법이 있을까요?

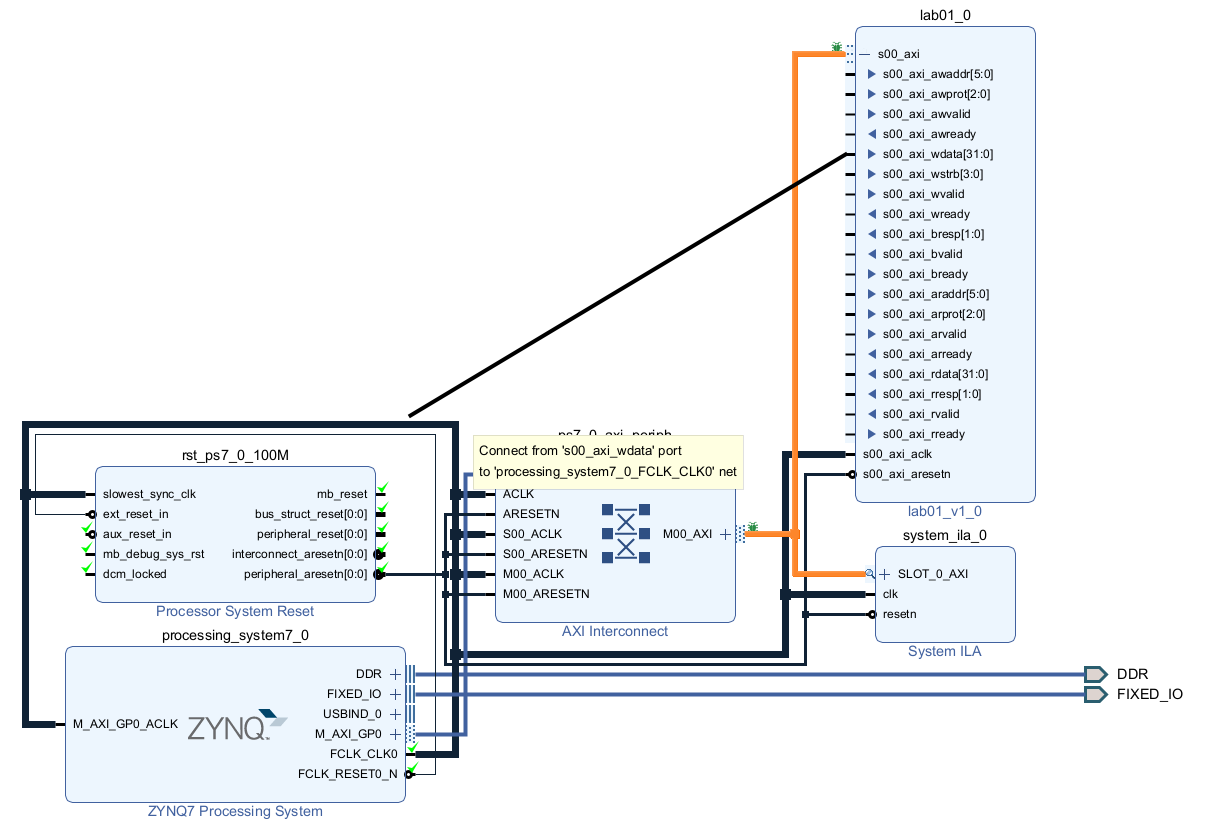

(axi_wdata와 같은 신호에 ila를 더 붙혀보는 방법은 실패하였고, c를 통한 접근도 실패하였습니다.)

복습의 범위를 넘어 연구의 범위로 넘어가고 있어서, 키워드 정도만 도와주실 수 있다면 스스로 더 연구해보겠습니다. ㅠㅠ!!

제가 궁금한 것은, 0c주소로 보낸 데이터가, 결국 bram(RAMB36E1)의 어떤 address에서 저장되는가? 입니다. 계속 반복해서 0c주소로 데이터를 보내고 있는데, 그게 카운터(mem_addr_cnt) 등을 통해서 어떤 주소로 어떻게 Control 되는지가 이해되지 않아서 보고 싶어서 그렇습니다. [+0c주소가 data register라고 register map에 있는 부분에 대해서는 인지하고 있습니다만, 그 다음의 경로가 추적이 되지 않아서 그렇습니다.]

#define XPAR_LAB01_0_BASEADDR 0x40000000

#define XPAR_LAB01_0_HIGHADDR 0x40000FFF

답변 1

1

안녕하세요 :)

ILA 모듈을 사용하시면 됩니다.

gui 상이 아닌 instantiation 을 직접하셔서 사용하시면 돼요.

다음 링크 참고 부탁드립니다.

https://docs.xilinx.com/v/u/en-US/pg172-ila

https://docs.xilinx.com/r/en-US/ug908-vivado-programming-debugging/ILA

즐공하세요 :)