인프런 커뮤니티 질문&답변

BRAM의 1cycle delay

해결된 질문

작성

·

564

답변 1

설계독학맛비

지식공유자

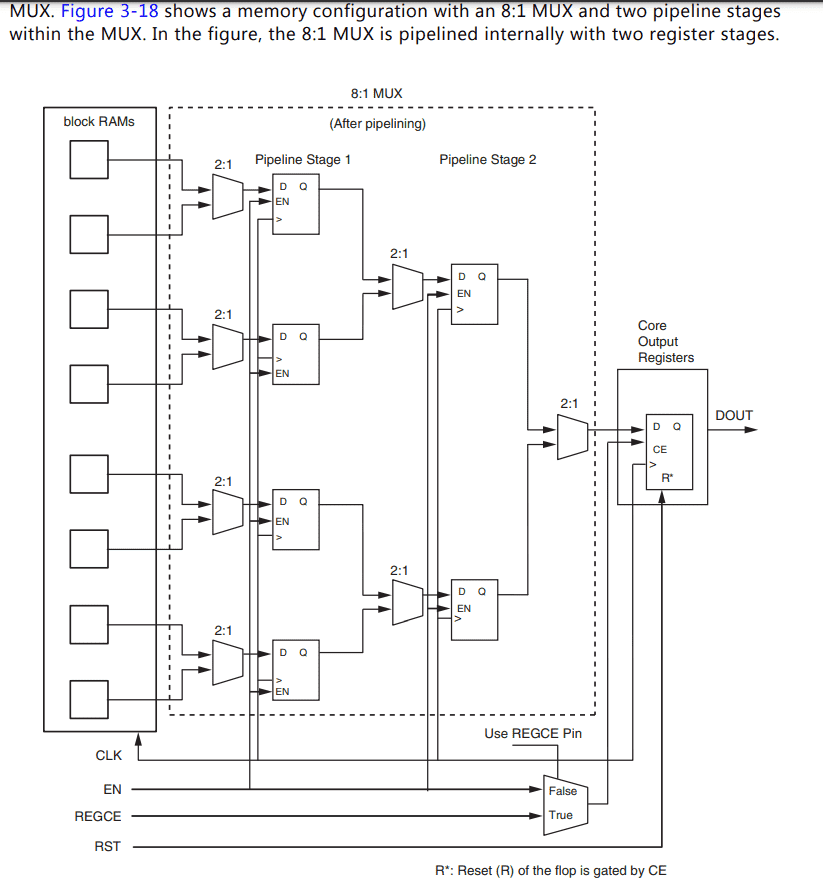

BRAM 을 생성할때, Primitive cell (Read latency 1) 에 추가로 F/F 을 사용해서 Latency 를 키워서 생성가능합니다. 이는 혹시 BRAM I/F 상에서 Timing Violation 이 발생하면 추가 latency 를 사용하여 생성가능합니다. (다음 그림은 큰 size 의 primitive bram 보다 큰 BRAM 을 사용할때, 중간에 mux 가 붙게 됩니다. 이때, Timing Violation 의 발생원인이 됨으로, F/F 을 추가하여 latency 를 늘리게 됩니다.)

또한 BRAM 모듈 생성시 Latency 부분을 수정할 수 있습니다. (몇 Cycle 로 할지)

참고문서 : https://www.xilinx.com/support/documentation/ip_documentation/blk_mem_gen/v8_3/pg058-blk-mem-gen.pdf

대신 latency 를 늘리신 만큼, BRAM Controller 모듈에 늘린 latency 를 제어하기 위한 부분은 설계자가 추가해 줘야겠죠?!

즐공하세요 :)

강의에서 메모리 종류별 비교 표를 보여주시면서 Latency가 1cycle로 짧은 편이다고 말씀하셨던게 생각나서 여쭤봤는데 더 상세하게 보여주셔서 감사합니다

덕분에 잘 이해했어요 :)