Essential lecture for non-memory design engineers!

Gain FPGA knowledge and experience designing HW accelerators.

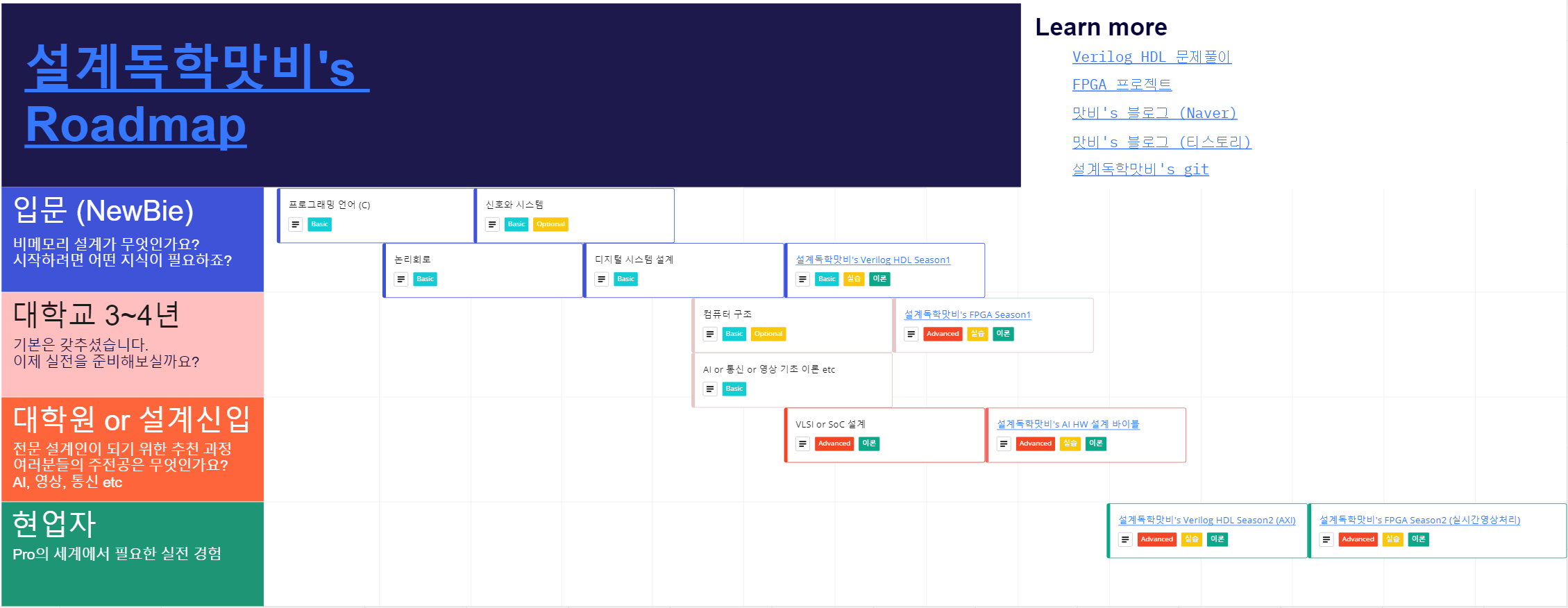

For those of you who dream of becoming a non-memory design expert

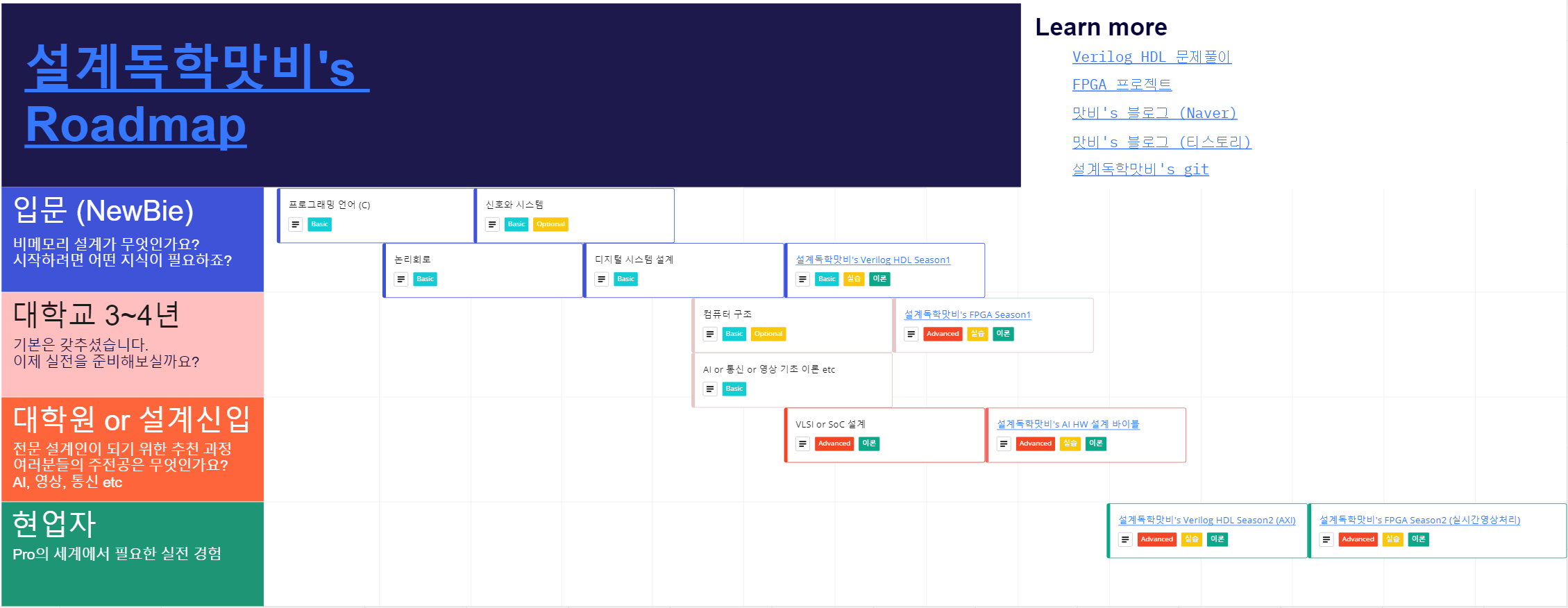

Check out the Matbi Universe roadmap. (Click on the image to go to the detailed roadmap page.)

hello!

This is a taste of self-study design .

This is the second lecture following Velilog HDL Season 1 !

If you have not completed the pre-course lectures, please pause your application for this lecture.

Please read the required documents below and, if you agree with them, apply for the course.

(As of 12/30/21) Likes: 730, Dislikes: 2, Views : 47,386.

* This video is currently private on YouTube and can only be accessed through Inflearn .

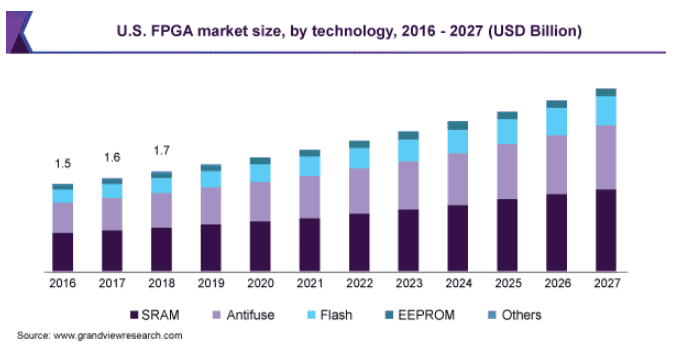

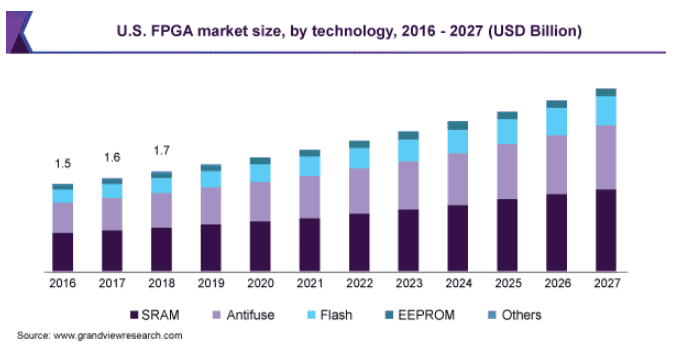

We need to learn FPGA.

The FPGA Market is growing.

As you learn the FPGAs the market demands, your value will also increase.

You're currently earning a salary in the top 1% of your industry , but there are opportunities to earn even more.

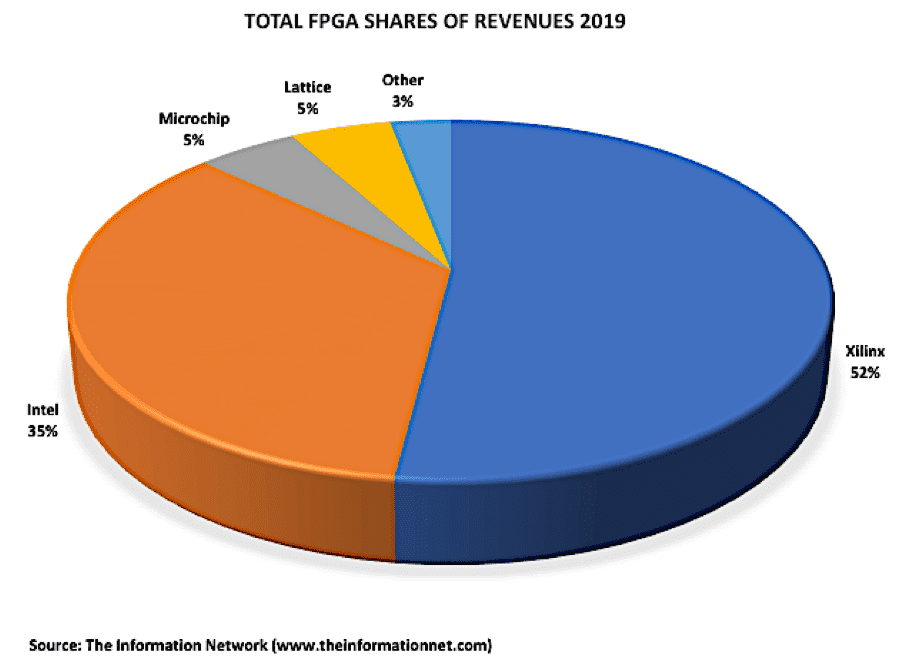

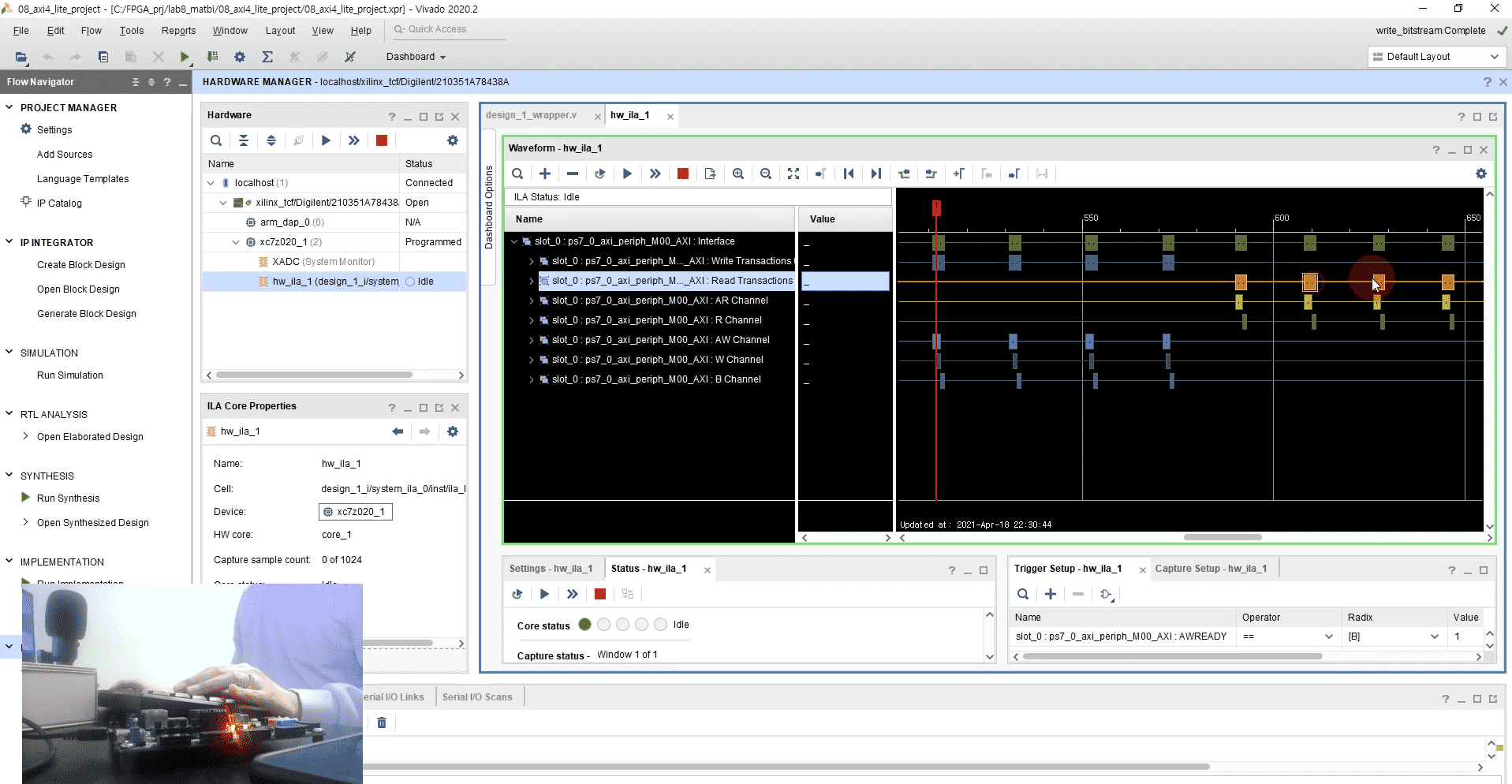

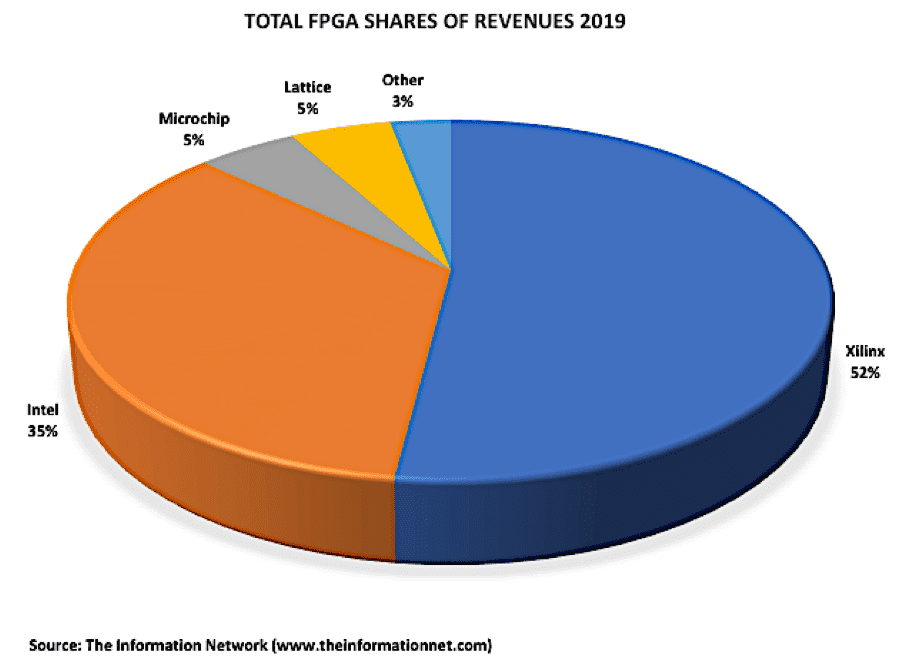

This lecture uses Xilinx FPGAs.

We need to learn about Xilinx's FPGAs .

The FPGA market share of Xilinx (AMD) vs Altera (Intel) speaks for itself.

The following graph is a statistical graph from 2019, and this gap is widening further.

- It currently has the highest market share, and it is expected that Xilinx will maintain the top market share for at least 10 years.

- Every company I've worked for uses Xilinx FPGAs.

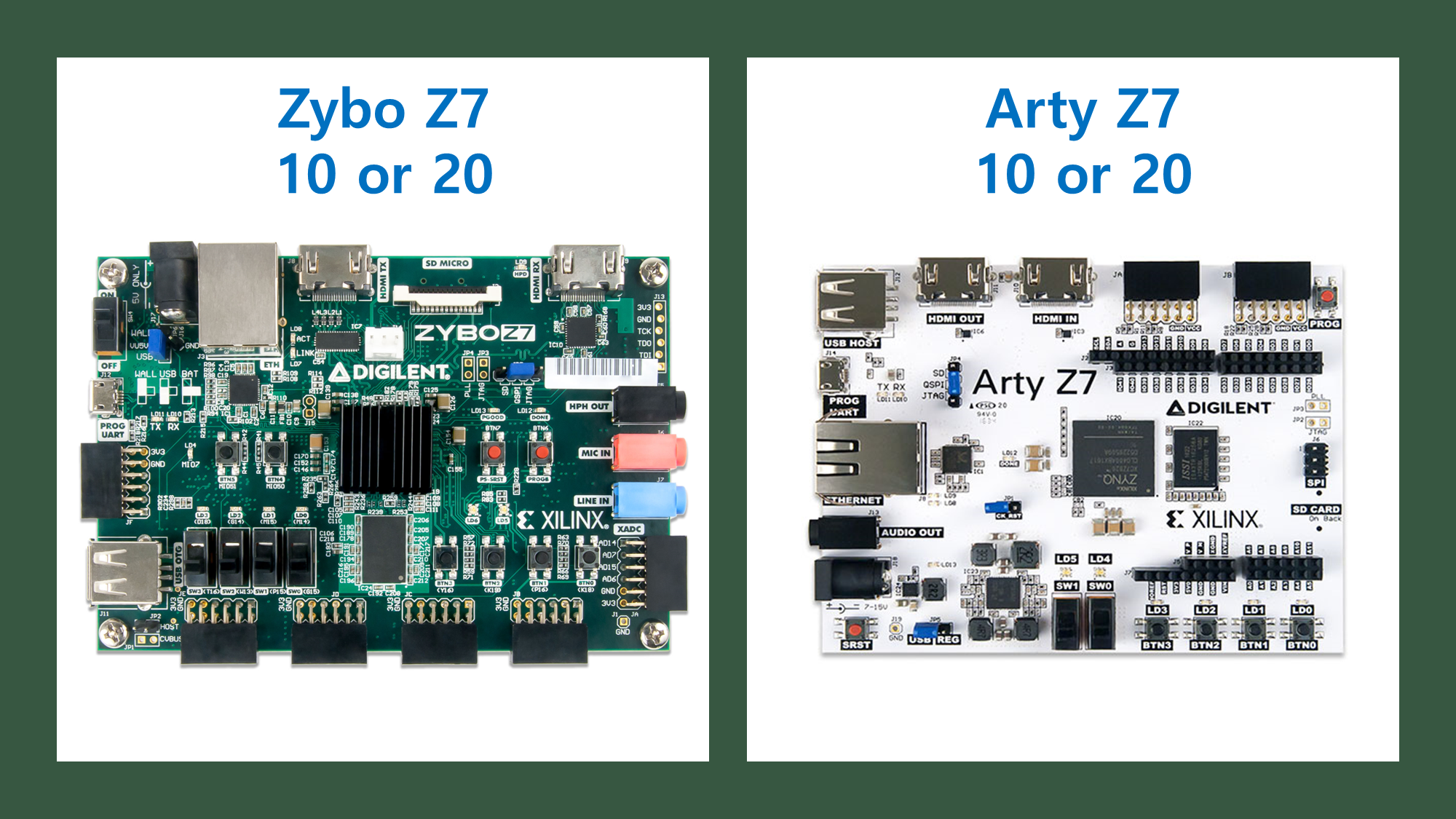

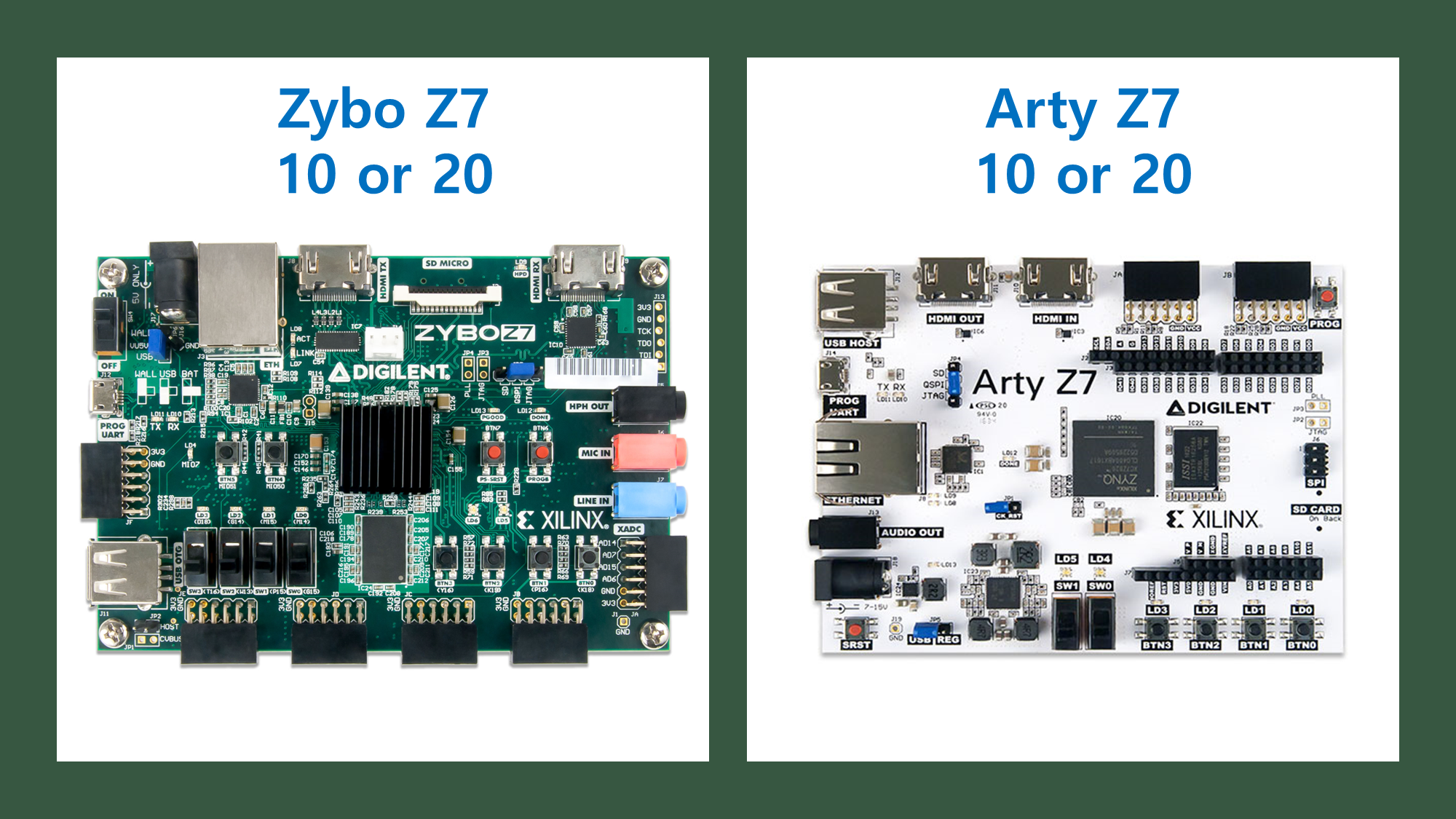

Here's why we chose Zybo/Arty Z7 for FPGA beginners:

- You can use both Arm (PS) / PL. → You can understand the inside of the FPGA System.

- This board is verified by Xilinx . → This is not a personal board. You can trust it.

- Many people use it. → Get help from engineers around the world.

- There are many examples. → You can study more after this lecture.

- There is HDMI in/out for video processing. → There is no reason to purchase an additional camera.

If you complete this course

First , you are ready to try out all the FPGA Boards.

Xilinx FPGA product lines number well over 1,000.

However, if you take this course, you will gain basic knowledge that can be used with any FPGA from Xilinx.

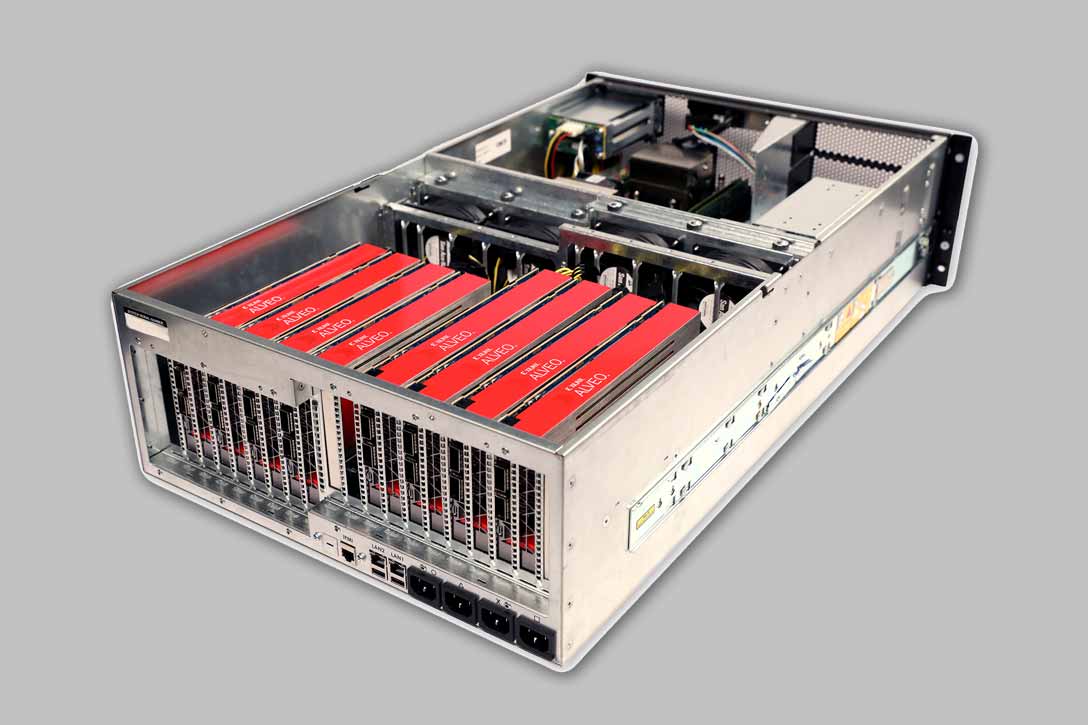

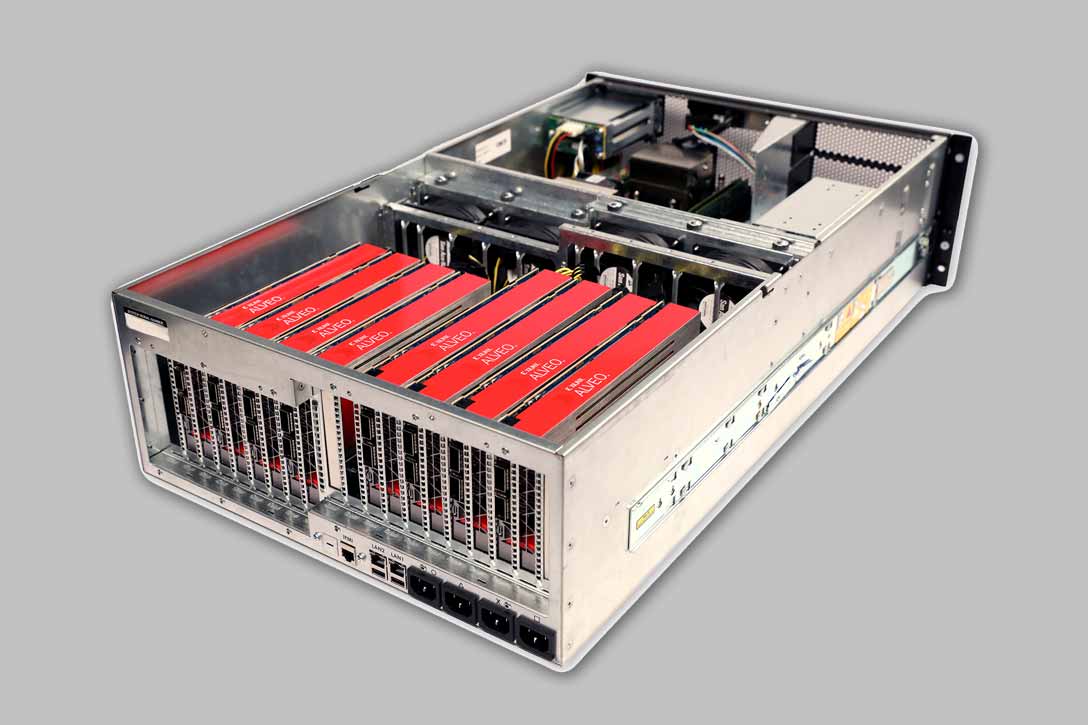

I started out with the Zybo board, and now I'm using the Alveo Card, Xilinx's flagship FPGA for servers, and AWS's f1 instance. FPGAs are used not only in embedded but also in the server market.

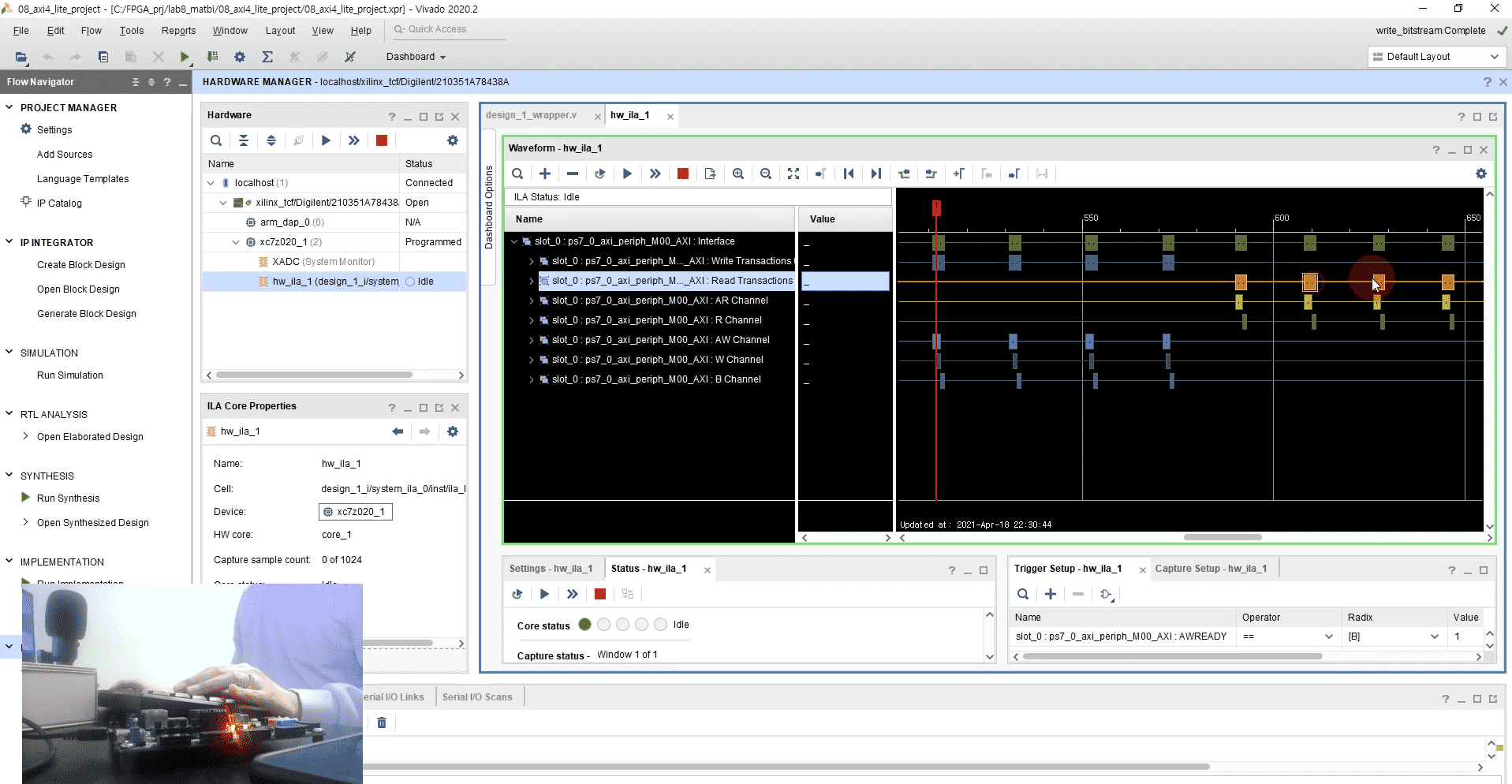

Second , you can understand the design of HW accelerators using Verilog HDL and FPGA.

You can design the Core you want to accelerate.

FPGA is a chip created for hardware acceleration.

This covers the process of designing and verifying the Core that you want to accelerate.

See you at work 🖐

Thank you so much for reading.

If you've read this far, you don't have to take my class.

I am confident that you will become excellent design engineers.

The choice is yours.

We look forward to seeing you in action.

Thank you, Matbi Dream.

🎁 We offer discount coupons to students and job seekers! 🥰

This was created to help ease the burden on those who do not yet have an income.

Please understand so that more people can benefit. Application link (click)

![[AUTOSAR] Complete AUTOSAR basic concepts for new employeesCourse Thumbnail](https://cdn.inflearn.com/public/courses/335114/cover/00356529-b9f9-4cc8-9b6b-9bddfd8d730d/335114.png?w=420)