Verilog FPGA Program 1 (Zynq mini 7020)

In this course, students will learn how to implement Verilog using the Zynq board.

This course is prepared for Basic Learners.

What you will learn!

Verilog coding

Utilizing ZYNQ Board

How to use Vivado, Vitis

Create a Test Bench and Verify Simulation

Download to board and check results

The core of implementing + practicing using the Zynq board.

📢 Please note before taking the class.

- This lecture is a text lecture in the form of an electronic document (PDF). (Approximately 110,000 characters) All source files explained in the lecture are provided to those who take the lecture. The lecture source code can be downloaded from Section 0 [Material Sharing Link].

Verilog implementation using Zynq board

✅ Code implementation ✅ Simulation verification using Text Bench ✅ Board verification

Before coding, we analyze the entire system and provide know-how on how to code efficiently. We explain in an easy-to-understand manner based on many techniques and know-how experienced in the field for the past 20 years. Also, the source codes included in the lecture are not codes for study, but codes used in practice. All those who attend the lecture will be provided with the entire source code used in the lecture.

The first half of the lecture will cover the following two topics:

- Install Vivado 2022.1

- Download the code implemented on the Zynq board and check the results

In the latter part of the lecture, we will verify the results downloaded to the board through coding and simulation verification for each topic.

- LED control using counter

- SPI Contoller Implementation

- UART Controller Implementation

- I2C Contoller Implementation

- Uses Xilinx IP (Clock Generator, Memory Generator)

- NRZL Decoder Implementation

- Implementation of FMC (Flexible Memory Controller) Interface

FPGA Utilization with Verilog for ZYNQ - Lecture Preview

FPGA Utilization with Verilog for ZYNQ - Lecture Preview

Detailed Curriculum

- outline

- HW configuration

- SW Installation

- Download ZynQ Board

- Basic Template Configuration

- Create a project

- Create Block Design

- Download in Debug Mode

- Add source code

- Bitstream Generation

- Run and download Vitis

- Download using FSBL (First Stage Bootloader)

- Create a FSBL project

- Create Boot Image

- Download the board and check the results

- Download using FSBL, Application SW

- Create a FSBL project

- Create an Application Project

- Create Boot Image

- Download the board and check the results

- LED control using counter

- Create a project

- Project screen configuration

- Add source code

- Text Editor Settings

- Code implementation

- XDC implementation

- Generate Bitstream

- Check the results

- Simulation

- Add simulation source file

- Implementing the tb_led_counter.v code

- Simulation in progress

- Simulation Results

- About the code

- Implementable code, non-implementable code

- The basic unit of code is Clock.

- All code is processed in parallel.

- ternary operator

- Use Register

- FSM (Finite State Machine)

- Spi Master Implementation

- Specs

- Code implementation

- Port Definition

- State Definition

- Code implementation

- Timing Diagram

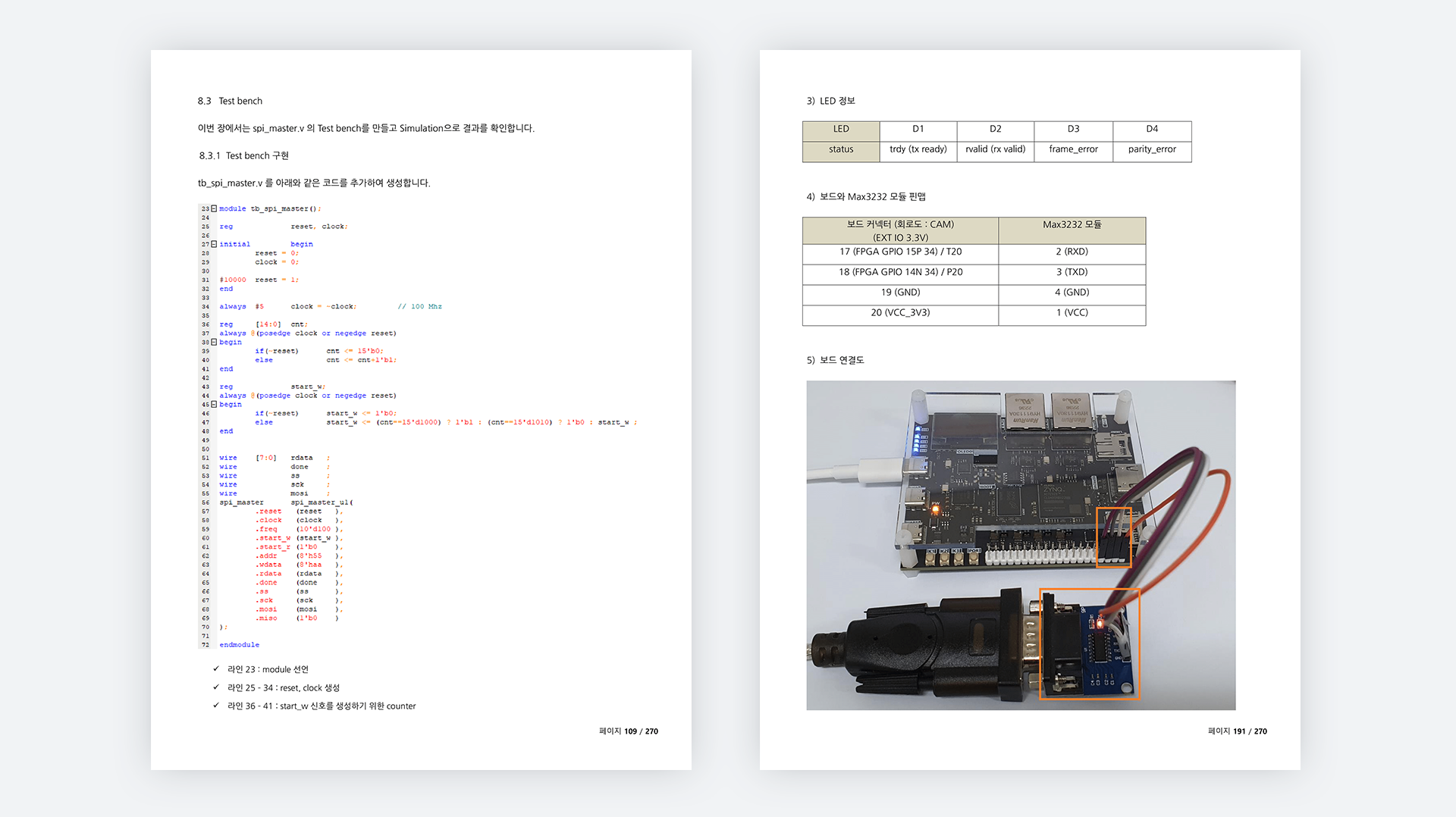

- Simulation

- Test bench implementation

- Check simulation results

- Spi Slave Implementation

- Specs

- Code implementation

- Port Definition

- State Definition

- Code implementation

- Simulation

- Test bench implementation

- Check simulation results

- Implementing Spi Communication

- Remove button noise

- Button circuit

- Code implementation

- Simulation

- SPI Task Implementation

- Port Definition

- Remove button noise

- State Definition

- Code implementation

- Simulation

- Test bench implementation

- Check simulation results

- Implementing UsetTop module

- Add xdc file

- Generate Bitstream

- Download the board and check the results

- Remove button noise

- Using Xilinx IP

- Create a Clock

- Memory Creation

- Block Memory Generator

- Memory Test

- Single Port RAM

- Simple Dual Port RAM

- Other memory

- UART Controller Implementation

- Uart Tx implementation

- Code implementation

- simulation

- Uart Rx implementation

- Create FIFO

- Code implementation

- simulation

- Uart Controller Implementation

- LoopBack implementation

- composition

- Code implementation

- simulation

- Implementing the UserTop module

- xdc generation

- Generate Bitstream, XSA files

- Check the results

- Uart Tx implementation

- I2C Controller Implementation

- I2C Controller Specification

- Start, Stop Condition

- 8bits data transfer

- Slave ID

- I2C Write Data Structure

- I2C Read Data Structure

- I2C Master Implementation

- i2c_master write signal analysis

- i2c_master read signal analysis

- Implementing i2c_master code

- i2c_master simulation

- Check the results

- i2c_master8x8 implementation

- i2c_master8x8 simulation

- I2C Slave Implementation

- I2C Slave Signal Analysis

- i2c_slave8x8 code implementation

- i2c_reg8x8 implementation

- i2c_slave8x8, i2c_reg8x8 simulation

- I2C TASK

- Implementing i2c_task code

- Implementing the UserTop module

- Add xdc file

- Generate Bitstream, XSA files

- Download the board and check the results

- I2C Controller Specification

- NRZL Decoder Implementation

- System Overview

- Code implementation

- Create clock

- Create FIFO

- data_counter implementation

- noise_reduction implementation

- data_encoder implementation

- nrzlDecTop implementation

- Implementing the UserTop module

- xdc implementation

- Create Bitstream, XSA files, and check results

- conclusion

- FMC Interface Implementation

- FMC Timing

- Code implementation

- fmc_model.v

- simulation fmc_model

- fmc_interface.v

- sys_host.v

- spram_32x8192

- simulation fmc_interface

- fmc_top.v

- UserTop.v

- UserTop.xdc

- Bitstream Generation

- Troubleshooting Timing Errors

- Download the board and check the results

- conclusion

- Revision History

- Basic Template Configuration

Q&A 💬

Q. Who is the target audience for this lecture?

This course is for those who want to learn Verilog and FPGA. This course has reorganized the content so that "FPGA Utilization with Verilog" can be implemented on the Zynq board, and all source codes use materials verified on the Zynq mini 7020 (7010) board.

Q. Is there anything I need to prepare to attend the lecture?

All the contents of the lecture can be practiced on the Zynq mini 7020 (7010) board. If you prepare the Zynq mini 7020 (7010) board, it will be very helpful because you can implement the code yourself and check the results.

Q. What program tools do you use?

I am using Vivado 2022.1 version. There is a section in the lecture about installing tools, so please install them according to the lecture.

Q. Where can I buy the Zynq mini board?

You can purchase it through domestic shopping malls or AliExpress.

Accumulated with 25 years of experience

We share our know-how on utilizing Verilog.

I have been working as a developer for over 20 years in large and small companies and currently run a small business. I have developed an ISP (Image Signal Processing) ASIC for CCTV and many products using FPGA such as OLED inspection equipment and DAQ (Data Acquisition System). In addition to FPGA, I have a lot of experience in FW development (STM32, PIC32, AVR, ATMEGA, etc.), circuit design, and Windows Program.

💾 Please check the lecture environment.

- For the practice environment, we use Windows OS, Vivado 2022.1.

- This lecture is a text lecture in electronic document (PDF) format. (Approximately 110,000 characters)

Recommended for

these people!

Who is this course right for?

For those who want to learn FPGA

For those who want to learn Verilog

For those who want to learn Zynq

Need to know before starting?

C language

Verilog Language (Basics)

Hello

This is ihil

Students

1,443

Reviews

50

Rating

4.8

Courses

17

저는 지난 20여년 동안 대기업, 중소기업에서 개발자로 일해왔고

현재는 작은 기업의 대표로 있습니다.

주요 경력사항은

Verilog HDL을 이용한 FPGA 설계

CCTV용 ISP ASIC 개발 (약 10년)

OLED Display 검사장비 개발 (약 3년)

FPGA를 이용한 장비 개발

MCU FW

STM32

PIC32

AVR, ATMEGA

DSP (TI)

Windows Application Program

Visual Studio MFC, C++

입니다.

Curriculum

All

381 lectures

are provided.