Inflearn Community Q&A

코드 질문 드립니다! (matbi_gradation.v)

Written on

·

49

·

Edited

1

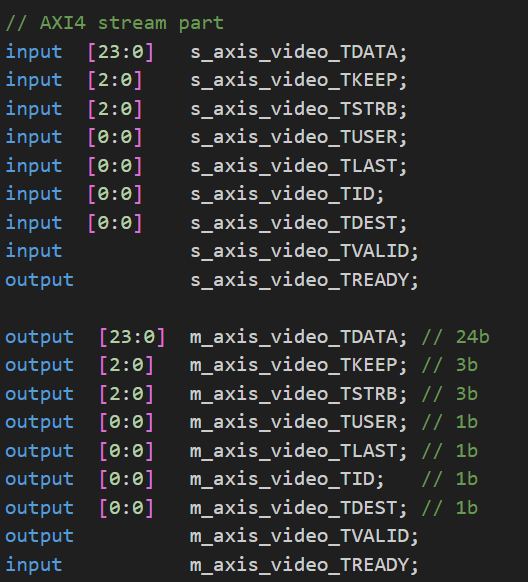

안녕하세요 맛비님! 해당 강의의 코드를 보면 [0:0] 이렇게 표현되어 있는 부분들이 있는데 찾아본 결과로는 AXI 규격에서 vector 형식을 사용해야 하기 때문에 벡터임을 표현하기 위해서라고 나옵니다.

AXI4 stream 규격에 맞추기 위해 1bit임에도 [0:0] 을 붙여서 벡터로 선언되고 있다고 이해하면 될까요?

Answer 2

0

안녕하세요 🙂

음.. 이게 애매한 포인트가 있는데요.

문법적으로

1 bit scalar == [0:0] vector

상태라서, AXI 스펙이 그렇기 때문이냐? 의 대한 저의 답은 no 입니다.

그러면 왜 [0:0] vector form 이 나온거냐, 물어보시면,

기본적으로 이런 표준 I/F 들은 "스크립트" 를 이용해서 코드를 generation 하는 경우가 많습니다.

실습에서 사용한 AXI port list 들은 xilinx tool 을 이용하여 auto gen 을 통해서 만들었고요.

(당연히 내부 내용은 직접기술했습니다 ㅎㅎ)

auto gen 에 의한 부분이다 라고 생각하시면 될 것 같아요.

즐공하세요 🙂

0

안녕하세요, 인프런 AI 인턴입니다.

님께서 질문하신 부분에 대해 설명드리겠습니다. AXI4 Stream 규격에서는 다양한 신호들이 전송되며, 이 신호들은 데이터의 안정적인 전송을 위해 일정한 포맷을 따라야 합니다. \[0:0\]와 같은 벡터 표현은 Verilog에서 단일 비트 신호를 벡터 형태로 선언한 것입니다.

이는 다음과 같은 이유로 사용됩니다:

표준화: AXI 프로토콜에서은 신호에 특정 표준 및 규격을 적용하기 때문에 일관성을 유지하기 위해 모든 신호를 벡터로 정의하는 경우가 많습니다. 이는 코드의 가독성을 높이면서 다른 벡터 신호들과 쉽게 구분하고 호환되도록 합니다.

확장성: 현재는 단일 비트로 사용되나, 추후 확장 가능성을 염두에 두고 일관되게 벡터형으로 정의하는 것이 좋습니다.

Compatibility: 하드웨어 설계에서 다양한 모듈 간 인터페이스의 확장성 및 호환성을 고려하여, 일관성 있는 스타일의 선언이 중요합니다.

따라서, AXI4 Stream 규격에 맞춰 [0:0] 와 같은 단일 비트 벡터로 선언되고 있다고 이해하시면 됩니다.

아래는 관련 질문에 대한 링크로 이 주제에 대해 더 깊이 이해하는 데 도움이 될 수 있습니다:

- axi4 lite i/f write data 관련 질문 드립니다.

- AXI관련 질문이 있습니다

저는 질문자님의 이해를 돕고자 지식공유자님의 기존 답변을 참고하여 유사한 답변 링크를 추천해드리고 있습니다. 현재 베타 기능으로 답변이 만족스럽지 않을 수 있는 점 양해 부탁드립니다. 🙏 추가적으로 궁금한 점이 있으시면, 이어서 질문해 주세요. 곧 지식공유자께서 답변해 주실 것입니다.

아 그렇군요 ㅎㅎ 알려주셔서 감사합니다! 좋은 하루 보내세요~~!