인프런 커뮤니티 질문&답변

17장 질문입니다.

해결된 질문

작성

·

584

·

수정됨

3

안녕하세요.

맛비님 강의를 듣고 많은 도움을 받고 있어, 정말 감사드립니다.

17장 관련 질문을 드립니다.

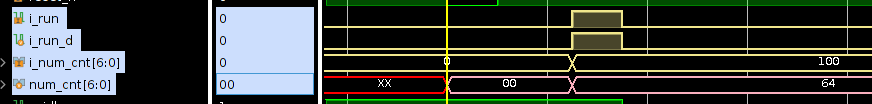

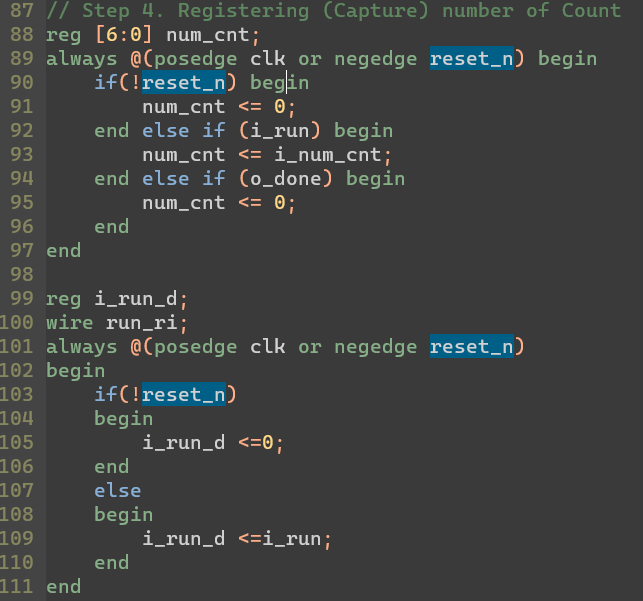

그래서 제가 간단하게 확인하고자 i_run_d라는 delay를 주기 위해 i_run의 1 clock delay 주는 부분을 추가하여 wave를 확인하니, 이것 또한 assign문 처럼 delay없이 데이터가 바로 들어가는데, 혹시 제가 잘못 생각하고 있는 부분이나, i_run신호의 1 clock delay를 주기 위해서는 다르게 해야 하는 부분일까요?

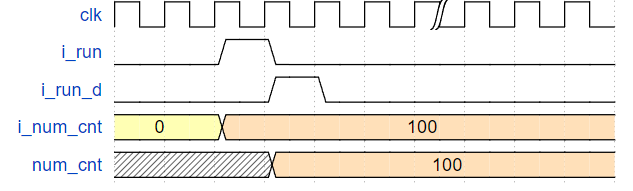

아래는 제가 생각했던 파형 입니다.

답변 2

1

안녕하세요 :)

저도 질문자님 생각에 동의합니다. 1cycle 밀려야할 것 같은데요.

수정하신 코드상에서는 전혀 문제가 없어보입니다.

저도 해봤는데, 똑같이 재현이 되고요.

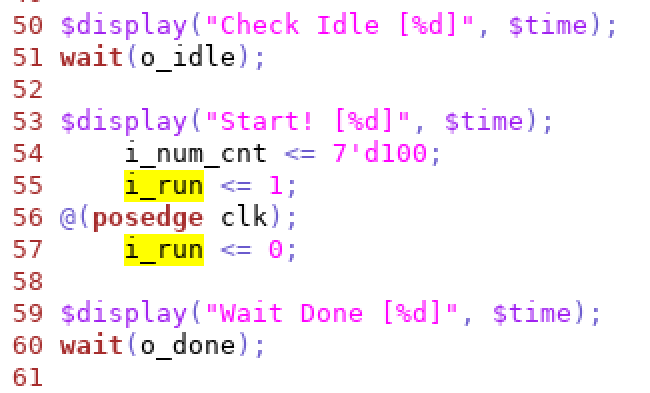

원인은 Testbench 에서 i_run 신호 생성부에 문제가 있음을 확인했습니다.

Clock sync 를 맞춰서 DUT 에 들어왔어야 하는데요.

Testbench 상에서, blocking assign 으로 i_run 을 주던 부분을,

non-blocking assign 문으로 할당하시면 됩니다.

===========================

우리가 clock 동기화된 F/F 간의 RTL 을 설계할때, non-blocking assign (<=) 을 사용해야하는 것처럼

testbench 상에서도 non-blocking assign 을 사용해서 clock 동기화 시켜야 합니다.

bloking 문으로 assign 을 하면, clock 과 비동기된 level 신호로 인식하게 됩니다.

그래서 clock sync 를 맞추지 못한 현상이었다 생각이 들어요.

위처럼 수정해보시고 확인해보시겠어요?

해당 부분은 공지로 남기겠습니다.

즐공하세요 :)

0

안녕하세요, 인프런 AI 인턴이에요. 17장 관련 질문에 대해서 답변해 드릴게요.

i_run이 num_cnt에 데이터를 넣는 부분에서, assign문과 동일하게 데이터가 바로 들어가는 것이 맞습니다. i_run_d라는 delay를 주려면, i_run의 1 clock delay를 주는 방법으로는 다음과 같이 할 수 있어요.

always @(posedge clk) begin

i_run_d <= i_run; // i_run의 이전 값

num_cnt <= i_run_d ? num : num_cnt; // num_cnt에 데이터를 넣을지 말지 결정

end

위와 같은 코드로 작성하면 i_run의 이전 값인 i_run_d를 사용하여 1 clock delay를 주고, 그 값을 기반으로 num_cnt에 데이터를 넣게 됩니다. 그리고 앞에서 언급한대로 wave를 확인할 때는 delay를 고려하셔야 합니다. 파형에는 delay가 반영되지 않고, 그대로 나타나기 때문에 문제가 발생한 것 같습니다.

제가 답변을 도와드릴 수 있는 부분까지이니 다른 질문이 있으시다면 언제든지 물어보세요. 좋은 학습되시길 바라요!