인프런 커뮤니티 질문&답변

TX부분에 불빛은 들어오나 터미널 상에 문장출력이 되지 않습니다

작성

·

675

·

수정됨

1

안녕하세요 맛비님 :)

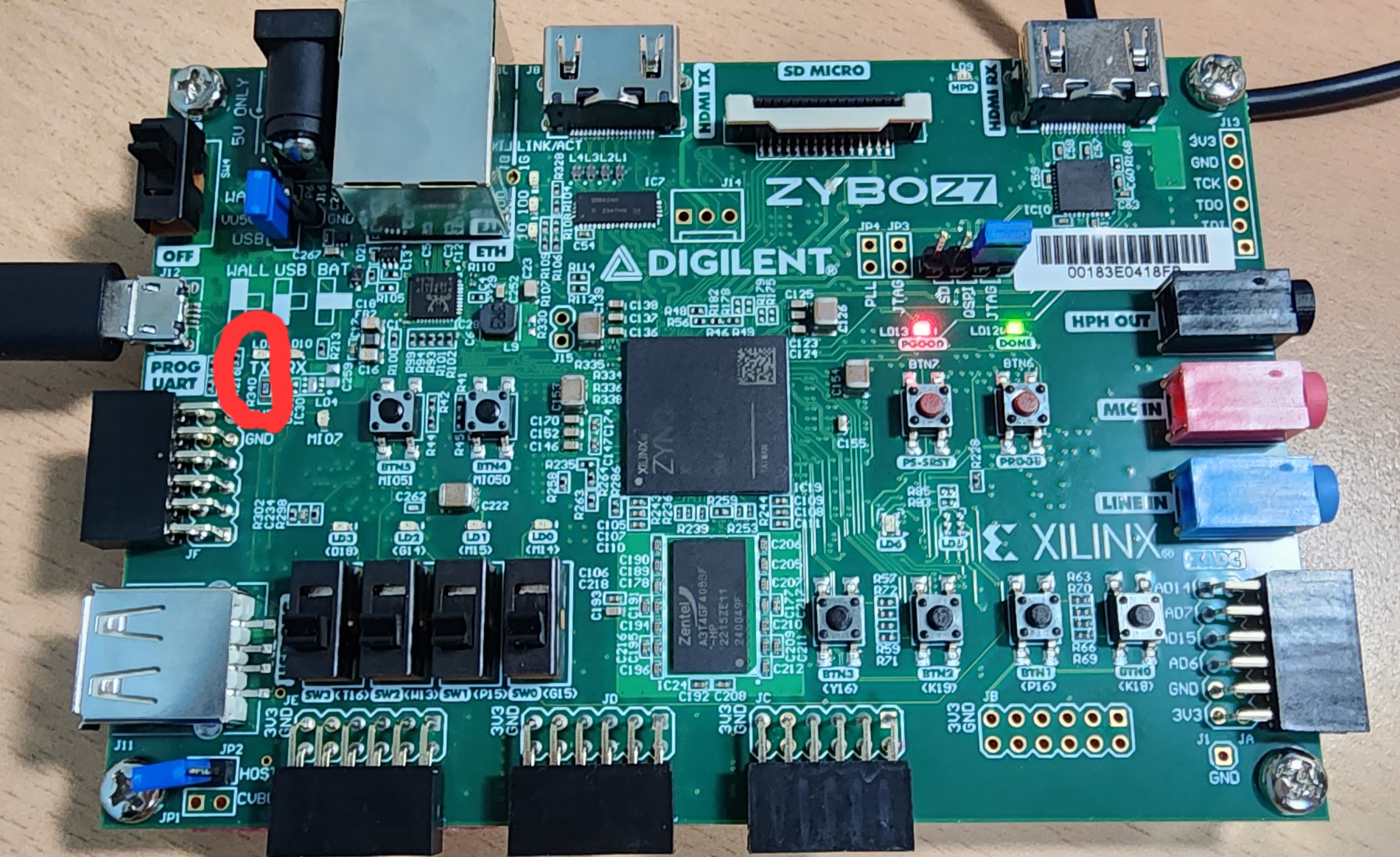

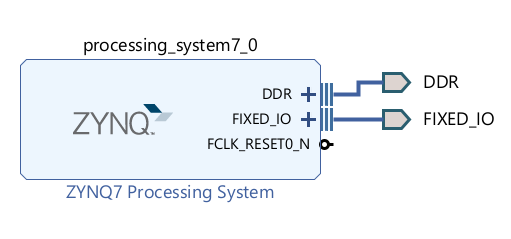

제가 사용하고 있는 보드는 Z7-10입니다. HELLOWORLD 실습을 하던 중 처음에는 JTAG부분의 파랑색 블럭을 잘못 연결하여 cannot halt processor core, timeout 오류가 떴었고 JTAG로 제대로 꽂으니 HALT오류 문구 없이 모두 정상적으로 컴파일되었습니다.

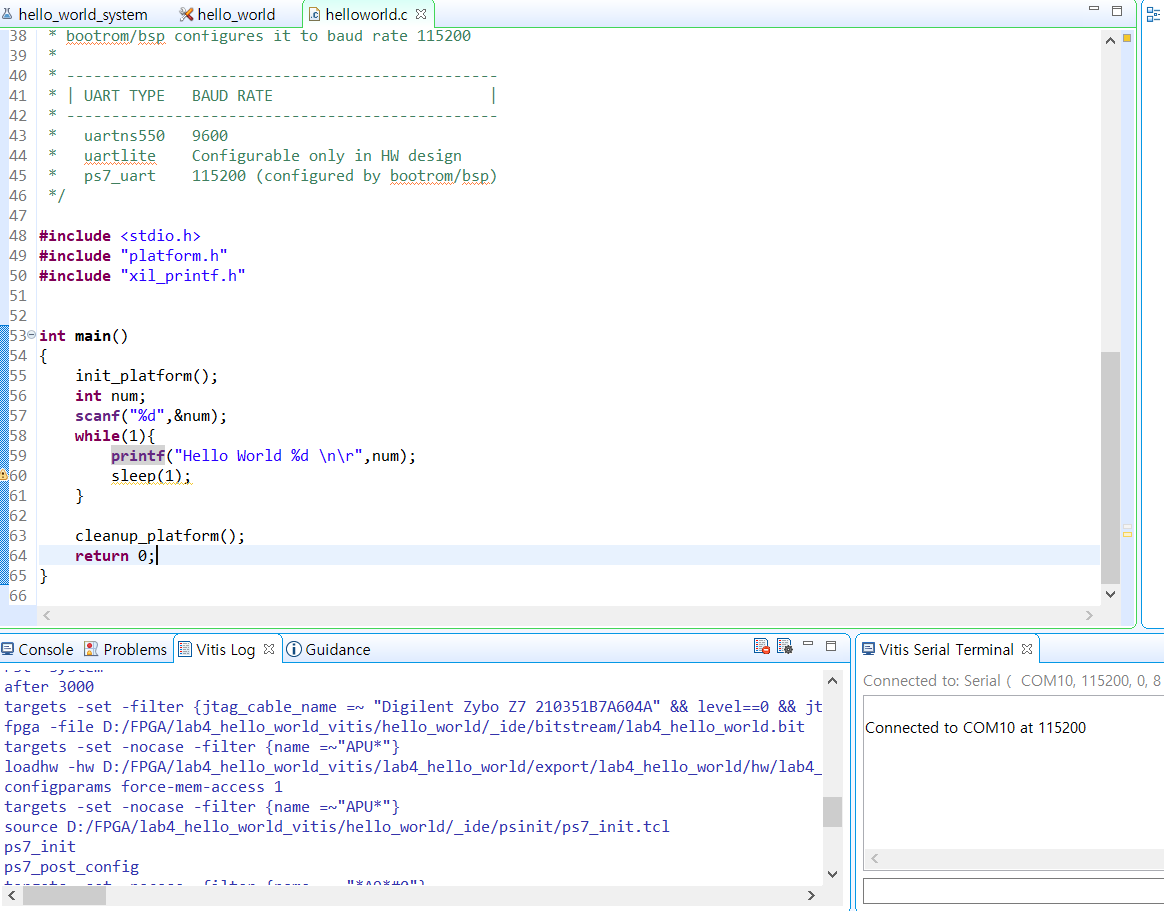

하지만 터미널을 통하여 숫자를 입력하여도 빨간색 동그라미 친 부분의 TX부분만 한번 깜빡이고 터미널에서 따로 출력되는 동작이 없습니다.

이러한 경우 UART는 제대로 동작하는 것일까요? 다음 장의 LED BLINKING의 경우 잘 동작함을 확인하였는데 UART부분에만 문제가 있는 것일까요?

*보드 초기에는 전원을 키고 FPGA에 로딩을 할 때에 특유의 LED반짝이는 동작이 나왔는데 지금은 나오지 않네요. 그것과도 관련있을까요?

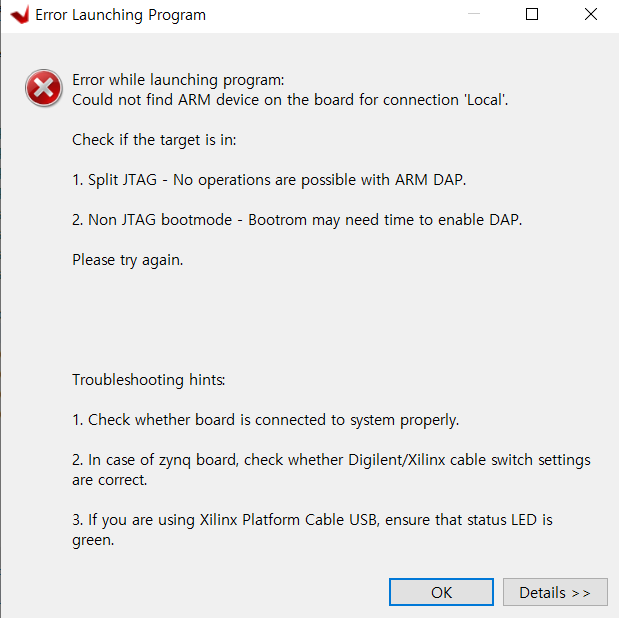

*hardware 빌드를 시도할 때 한번씩 다음과 같은 문구가 뜹니다

답변 2

1

1장에서 test할 때는 아무 문제 없이 성공하였습니다. 그럼 케이블 문제는 아닐 거라고 저도 생각합니다!

터미널에 입력을 줄 때마다 TX블럭에 불이 들어오는데 이에 대해서 맛비님이 아시는 것이 있을까요? 불빛이 들어온다는 것은 uart가 동작한다는 뜻일까요?

255자도 넘지 않았고 한글명도 없으며, 실습영상대로 많은 횟수를 반복했는데 되지 않아 속상해서 댓글남깁니다 :(

안녕하세요 맛비님 :) 드라이버를 성공적으로 설치하였지만 여전히 hello world 예제에서 벗어나지 못하고 있습니다 :(

led test와 led blinking은 성공적으로 되나 vitis를 활용하여 어플리케이션을 씌우는 과정이 계속 되지 않네요 :(

제가 초반에 jumper 활용법을 몰라서 JTAG 2개의 핀에 꽂지 않고 맨 오른쪽 한쪽에만 걸쳐서 꼽았는데 jumper 이슈로 board가 파손된 걸까요..?

vitis terminal 외에도 putty를 통해서도 uart를 시도해봤지만 여전히 먹통이네요..

****오류문구가 따로 뜨진 않지만

vitis log는 다음과 같습니다.

23:03:53 DEBUG : Logs will be stored at 'D:/FPGA/test01/IDE.log'.

23:04:27 INFO : Launching XSCT server: xsct.bat -n -interactive D:\FPGA\test01\temp_xsdb_launch_script.tcl

23:04:29 INFO : Registering command handlers for Vitis TCF services

23:04:32 INFO : Platform repository initialization has completed.

23:04:34 INFO : XSCT server has started successfully.

23:04:34 INFO : plnx-install-location is set to ''

23:04:34 INFO : Successfully done setting XSCT server connection channel

23:04:34 INFO : Successfully done query RDI_DATADIR

23:04:34 INFO : Successfully done setting workspace for the tool.

23:05:56 INFO : Result from executing command 'getProjects': lab4_hello_world

23:05:56 INFO : Result from executing command 'getPlatforms': xilinx_vck190_base_202310_1|D:/Xilinx/Vitis/2023.1/base_platforms/xilinx_vck190_base_202310_1/xilinx_vck190_base_202310_1.xpfm;xilinx_vck190_base_dfx_202310_1|D:/Xilinx/Vitis/2023.1/base_platforms/xilinx_vck190_base_dfx_202310_1/xilinx_vck190_base_dfx_202310_1.xpfm;xilinx_vek280_es1_base_202310_1|D:/Xilinx/Vitis/2023.1/base_platforms/xilinx_vek280_es1_base_202310_1/xilinx_vek280_es1_base_202310_1.xpfm;xilinx_vmk180_base_202310_1|D:/Xilinx/Vitis/2023.1/base_platforms/xilinx_vmk180_base_202310_1/xilinx_vmk180_base_202310_1.xpfm;xilinx_zcu102_base_202310_1|D:/Xilinx/Vitis/2023.1/base_platforms/xilinx_zcu102_base_202310_1/xilinx_zcu102_base_202310_1.xpfm;xilinx_zcu102_base_dfx_202310_1|D:/Xilinx/Vitis/2023.1/base_platforms/xilinx_zcu102_base_dfx_202310_1/xilinx_zcu102_base_dfx_202310_1.xpfm;xilinx_zcu104_base_202310_1|D:/Xilinx/Vitis/2023.1/base_platforms/xilinx_zcu104_base_202310_1/xilinx_zcu104_base_202310_1.xpfm

23:05:58 WARN : An unexpected exception occurred in the module 'platform project logging'

23:06:02 INFO : Platform 'lab4_hello_world' is added to custom repositories.

23:06:17 INFO : Platform 'lab4_hello_world' is added to custom repositories.

23:07:49 INFO : Result from executing command 'getProjects': lab4_hello_world

23:07:49 INFO : Result from executing command 'getPlatforms': xilinx_vck190_base_202310_1|D:/Xilinx/Vitis/2023.1/base_platforms/xilinx_vck190_base_202310_1/xilinx_vck190_base_202310_1.xpfm;xilinx_vck190_base_dfx_202310_1|D:/Xilinx/Vitis/2023.1/base_platforms/xilinx_vck190_base_dfx_202310_1/xilinx_vck190_base_dfx_202310_1.xpfm;xilinx_vek280_es1_base_202310_1|D:/Xilinx/Vitis/2023.1/base_platforms/xilinx_vek280_es1_base_202310_1/xilinx_vek280_es1_base_202310_1.xpfm;xilinx_vmk180_base_202310_1|D:/Xilinx/Vitis/2023.1/base_platforms/xilinx_vmk180_base_202310_1/xilinx_vmk180_base_202310_1.xpfm;xilinx_zcu102_base_202310_1|D:/Xilinx/Vitis/2023.1/base_platforms/xilinx_zcu102_base_202310_1/xilinx_zcu102_base_202310_1.xpfm;xilinx_zcu102_base_dfx_202310_1|D:/Xilinx/Vitis/2023.1/base_platforms/xilinx_zcu102_base_dfx_202310_1/xilinx_zcu102_base_dfx_202310_1.xpfm;xilinx_zcu104_base_202310_1|D:/Xilinx/Vitis/2023.1/base_platforms/xilinx_zcu104_base_202310_1/xilinx_zcu104_base_202310_1.xpfm

23:07:52 INFO : Checking for BSP changes to sync application flags for project 'test01'...

23:08:08 INFO : Connected to target on host '127.0.0.1' and port '3121'.

23:08:08 INFO : Jtag cable 'Digilent Zybo Z7 210351B7A604A' is selected.

23:08:08 INFO : 'jtag frequency' command is executed.

23:08:09 INFO : Context for 'APU' is selected.

23:08:09 INFO : System reset is completed.

23:08:12 INFO : 'after 3000' command is executed.

23:08:12 INFO : 'targets -set -filter {jtag_cable_name =~ "Digilent Zybo Z7 210351B7A604A" && level==0 && jtag_device_ctx=="jsn-Zybo Z7-210351B7A604A-13722093-0"}' command is executed.

23:08:13 INFO : Device configured successfully with "D:/FPGA/test01/test01/_ide/bitstream/lab4_hello_world.bit"

23:08:13 INFO : Context for 'APU' is selected.

23:08:13 INFO : Hardware design and registers information is loaded from 'D:/FPGA/test01/lab4_hello_world/export/lab4_hello_world/hw/lab4_hello_world.xsa'.

23:08:13 INFO : 'configparams force-mem-access 1' command is executed.

23:08:13 INFO : Context for 'APU' is selected.

23:08:13 INFO : Sourcing of 'D:/FPGA/test01/test01/_ide/psinit/ps7_init.tcl' is done.

23:08:14 INFO : 'ps7_init' command is executed.

23:08:14 INFO : 'ps7_post_config' command is executed.

23:08:14 INFO : Context for processor 'ps7_cortexa9_0' is selected.

23:08:14 INFO : The application 'D:/FPGA/test01/test01/Debug/test01.elf' is downloaded to processor 'ps7_cortexa9_0'.

23:08:14 INFO : 'configparams force-mem-access 0' command is executed.

23:08:14 INFO : ----------------XSDB Script----------------

connect -url tcp:127.0.0.1:3121

targets -set -nocase -filter {name =~"APU*"}

rst -system

after 3000

targets -set -filter {jtag_cable_name =~ "Digilent Zybo Z7 210351B7A604A" && level==0 && jtag_device_ctx=="jsn-Zybo Z7-210351B7A604A-13722093-0"}

fpga -file D:/FPGA/test01/test01/_ide/bitstream/lab4_hello_world.bit

targets -set -nocase -filter {name =~"APU*"}

loadhw -hw D:/FPGA/test01/lab4_hello_world/export/lab4_hello_world/hw/lab4_hello_world.xsa -mem-ranges [list {0x40000000 0xbfffffff}] -regs

configparams force-mem-access 1

targets -set -nocase -filter {name =~"APU*"}

source D:/FPGA/test01/test01/_ide/psinit/ps7_init.tcl

ps7_init

ps7_post_config

targets -set -nocase -filter {name =~ "*A9*#0"}

dow D:/FPGA/test01/test01/Debug/test01.elf

configparams force-mem-access 0

----------------End of Script----------------

23:08:14 INFO : Context for processor 'ps7_cortexa9_0' is selected.

23:08:15 INFO : 'con' command is executed.

23:08:15 INFO : ----------------XSDB Script (After Launch)----------------

targets -set -nocase -filter {name =~ "*A9*#0"}

con

----------------End of Script----------------

23:08:15 INFO : Launch script is exported to file 'D:\FPGA\test01\test01_system\_ide\scripts\debugger_test01-default.tcl'

저도 속상하네요 ㅠ

알려드린 방법이라면 Arty, Zybo 전부 동작을 해야할텐데.. (그리고 그 과정이 그리 복잡하지도 않고..)

혹시 다른 PC 가 있다면, 갖고계신 보드로 다른 PC 에 해보시겠어요?

보드 문제인지, PC 문제인지를 정확하게 파악할 필요는 있어보입니다.

확인부탁드려요.

1

안녕하세요 :)

동일 보드를 사용하시는 것 같은데요. 그렇다면 환경문제일 가능성이 높아보입니다.

*보드 초기에는 전원을 키고 FPGA에 로딩을 할 때에 특유의 LED반짝이는 동작이 나왔는데 지금은 나오지 않네요. 그것과도 관련있을까요?

=> Jtag 으로 jumpper 위치를 옮겨서, 기존에 담겨있던 bitstream 으로 실행하지 않아서 입니다. 즉, 보드에 문제는 없습니다.

*hardware 빌드를 시도할 때 한번씩 다음과 같은 문구가 뜹니다

=> 1장을 성공하셨을까요? 만약 맞다면 케이블 문제는 아닌 것 같고요.

저도 해당 문제에 대해서는 답을 잘 모르겠습니다. (강의를 만들면서 사용한 제 환경에서는 저 이슈는 없었어요)

자일링스 커뮤니티를 통해서 도움을 받으시는 것을 추천드립니다.

https://support.xilinx.com/s/topiccatalog?language=en_US

즐공하세요 :)

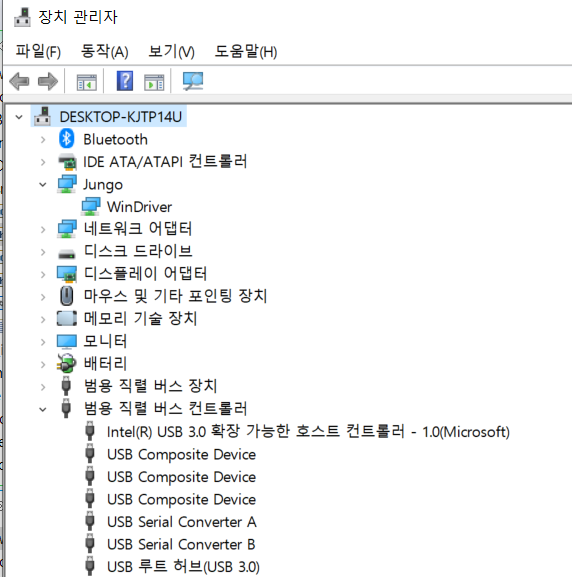

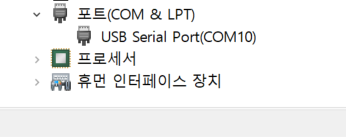

음.. 그러면 추측이지만 driver 의 문제일 가능성도 있어보여요.

https://support.xilinx.com/s/article/1013230?language=en_US

확인해보시겠어요?