인프런 커뮤니티 질문&답변

[HDL 38장-2부] AxLock, clog2

작성

·

534

1

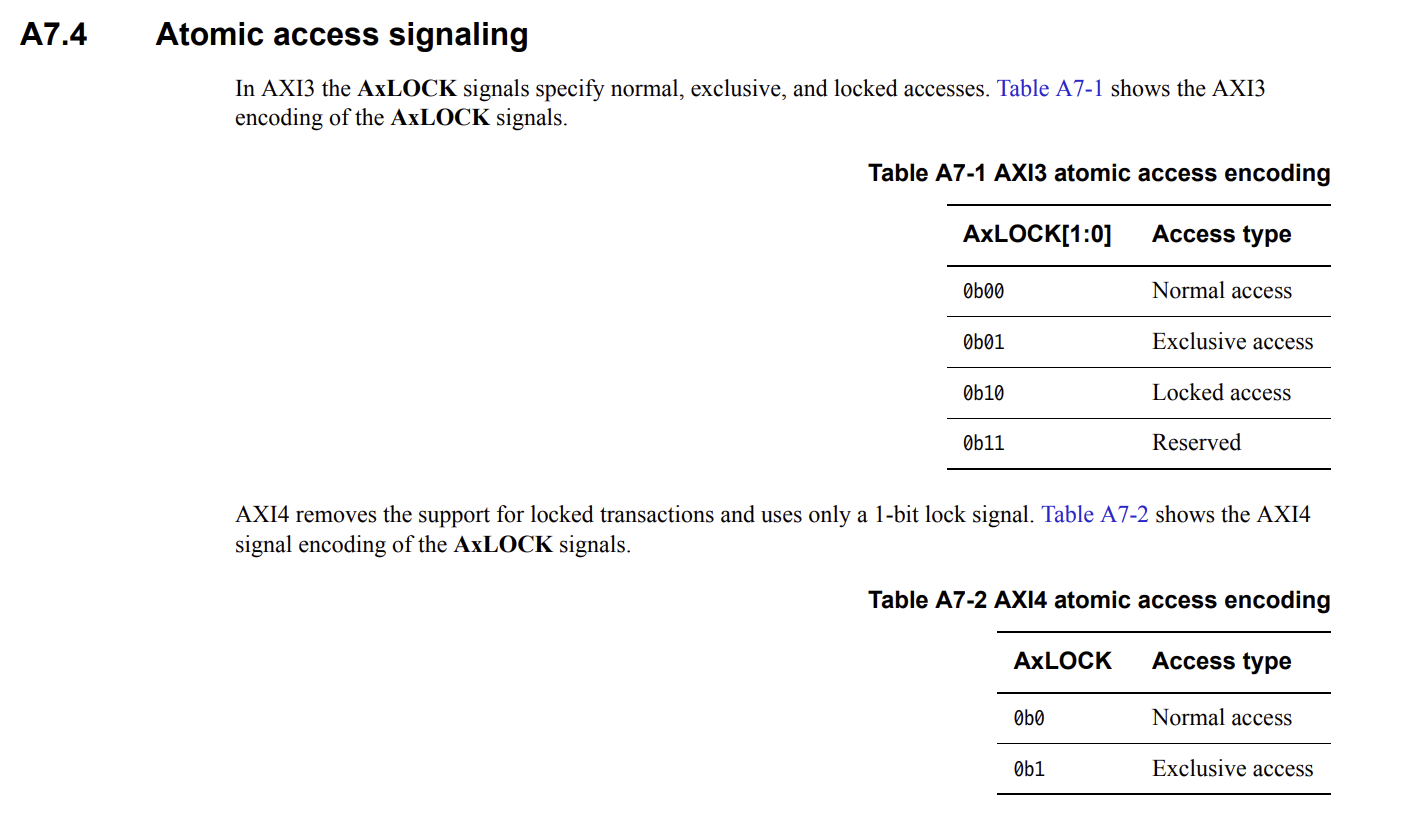

AXI4 에서는 Lock 비트수가 '1' 인데, 설계에서 2 비트수를 유지하는 것은 VIP 와의 연결을 위해서인가요?

clog2 자체가 해당 인자에 대한 필요 비트수를 출력하니 '+1' 보정은 없어도 될 것 같습니다.

답변 2

0

설계독학맛비

지식공유자

안녕하세요 :)

AXI VIP 연결때문이 맞아요.

현재 IP 가 Normal Access 만 사용하기 때문에, 동작에 문제는 없어보입니다.

현재 IP 가 Normal Access 만 사용하기 때문에, 동작에 문제는 없어보입니다.

정확하게 하려면, AXI4 를 검증하실 때는 하위 1bit 만 연결하시면 될 것 같아요.

즐공하세요 :)

0

안녕하세요, 인프런 AI 인턴이에요. AXI4의 Lock 비트수가 ‘1’인 이유와 설계에서 2비트 수를 유지하는 이유에 대해 알려드릴게요.

AXI4에서 Lock 비트수가 ‘1’인 이유는 Lock 신호가 여러 개의 Master 중에서 오직 하나의 Master만 사용할 수 있도록 하는데에 있어 충분한 것이기 때문이에요. Lock 비트는 단지 Master가 리소스에 액세스 할 수 있는지 여부를 나타내기 위해 사용되는 것이지, 여러 Master가 동시에 리소스에 액세스하도록 하는 것은 다른 신호들에 달려있어요.

설계에서 2비트 수를 유지하는 이유는 VIP와의 연결 관련이 아니라 다른 용도로 사용되기 때문이죠. clog2는 주어진 인자에 대한 필요한 비트 수를 나타내는 함수이고, 이 함수를 사용하면 ‘+1’ 보정을 따로 해주지 않아도 되는 장점이 있어요.

추가 질문이 있으신 경우 언제든지 물어보세요!