인프런 커뮤니티 질문&답변

read response 관련

해결된 질문

작성

·

305

답변 1

1

안녕하세요 :)

우선 AXI 스펙이 그렇게 정의되어 있다 로 해결이 될 것 같은데요.

질문주신 내용의 이유를 생각해보면

===========================

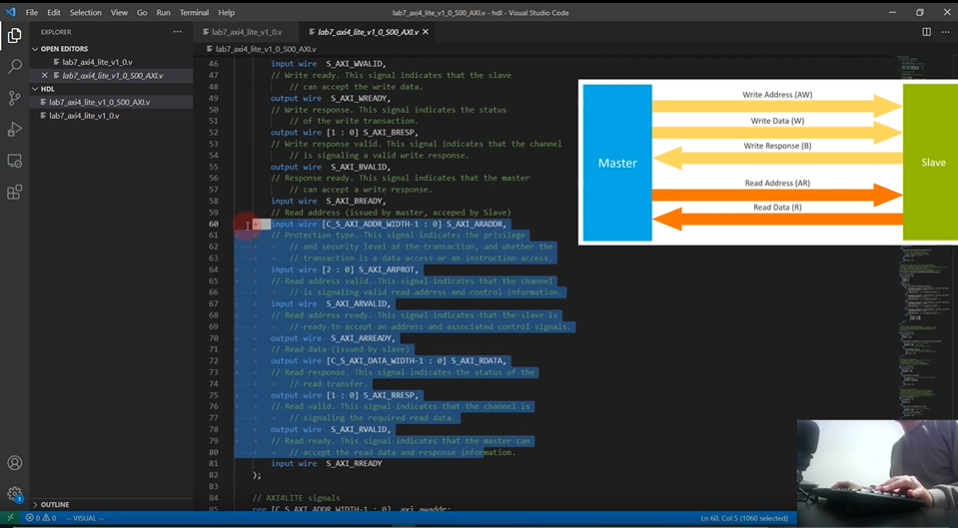

AXI-lite의 5개의 channel 과는 다르게 Read response 관련해서 S_AXI_RRESP 존재이유

Read data 가 정상인지 알기 위해서겠죠? (당연한 이야기)

(여러 다양한 변수로 인하여) 간혹 제대로 data 를 못 가져 올 수 있습니다.

read response와 관련된 ready/valid handshake가 없고 read에 관련된 handshake 만 있는 이유 또한 궁금합니다.

Write 에서는 Channel 이 3개, Read 는 2개이죠.

flow 를 생각해보면,

<Write>

Write Address

Write Data

Write Response

여기서 Write 의 Target (최종 목적지) 이 External memory 일시, Write 가 끝나는 시점은 3번입니다.

2번이 종료가 되었다고 해서 External memory 에 바로 Write 가 되지 않아요.

그 말은 3번까지 종료가 되어야 External memory 내의 Data 가 Valid 합니다.

이유는 Bus 를 통해서 Data 가 전달되고 (긴 과정)이 있기 때문이고요.

2번까지는 IP 기준에서 data 를 전달한거지, External memory 까지 도달하지 못한거죠. (2번 과정이 끝나야 request 가 External memory 에 도달함)

2번과정 이후, External memory 에 Write 를 완료해야, 이후에 3번이 종료가 됩니다.

<Read>

Read Address

Read Data (include Read response)

External memory 에서 Read 를 하게 되면, Read data 가 넘어오면 끝입니다.

앞서 Write 처럼 (긴 과정) 을 거쳐도 결국 read data 를 주는 주체(master)는 externel memory 입니다.

이미 Read 과정 1번에서 request 가 External memory 에 도달한거에요.

그래서 data 를 주면서 동시에 response 도 같이 포함합니다.

channel 을 아끼면 그만큼 Resouce (Area) 도 아낄 수 있고요.

자세한 내용은 스펙문서를 참고부탁드려요. (이게 현답일지도..?!)

즐공하세요 :)