인프런 커뮤니티 질문&답변

[HDL 22장] 실습편, rtl_v.txt 에 한줄이 더 생길 수가 있네요.

작성

·

468

1

테스트벤치에서 current state 가 S_DONE 이 되기 전에 s_valid, m_ready 둘다 '1' 이 될 수가 있어, 마지막에 o_hs 조건에 따라 fwrite 가 한번 더 발생할 수 있네요.

s_valid 나 m_ready 랜덤 생성할 때 아래 is_done 조건이 추가돼야 할 것 같습니다.

if(c_i_state == S_RUN & !is_i_done)

if(c_o_state == S_RUN & !is_o_done)

답변 2

1

n_i_state, n_o_state 에 대해 몇가지 질문이 있습니다. 선언할 때 아래와 같이 했고,

reg [1:0] n_i_state; // Next state (Variable in Combinational Logic)

always @(*) 블록에서 clk 와 상관없이 값이 갱신되고 있고, 무조건 값이 할당되도록 조치를 취하고 있습니다.

n_i_state = S_IDLE; // To prevent Latch.

저렇게 하면 n_i_state 가 reg 로 선언됐다 하더라도 합성(?) 과정에서 F/F 또는 Latch 로 변하지 않고 wire 처럼 마지막 상태를 유지하는 combination logic 으로 된다는 의미인가요?

그리고 always @(*) 블록 안에서 if / else 의 짝을 모두 맞추고 case 문 안에 default 문을 추가한다면 n_i_state 값이 한번만 변할텐데, 어쨋든 코드상으로는 2번 할당 '=' 합니다. 그러면 n_i_state 값이 아주 잠깐이라도 S_IDLE 로 변하는 상태가 발생하는지, 아니면 always @(*) 블록 안에서 최종 할당 값만 고려되어 합성(?)되는 건가요?

마지막으로, localparam 직접 사용 대신, F/F 의 Q 와 D 가 연결되듯 해도 문제될 건 없는지요?

//n_i_state = S_IDLE; // To prevent Latch.

n_i_state = c_i_state; // To prevent Latch.

0

안녕하세요 :)

말씀해주신대로 제공해드린 코드에 문제가 있을 수 있겠네요. (리포팅 감사드려요!)

혹시 실제로, 문제가 되는 케이스를 올려주실 수 있을까요? (수정 후 확인하려는 용도에요)

예를들면

seed 번호 혹은 test num 을 무엇으로 했는지

직접 수정해서 넣으셨을지

확인 해보고 수정해서 실습코드에 반영할께요.

감사합니다 :)

말씀해주신대로 수정해도 될 것 같고요.

저는 다음과 같이 수정해서 올려놓을께요. (일단 기본 case, random 은 잘 넘어가네요)

=====

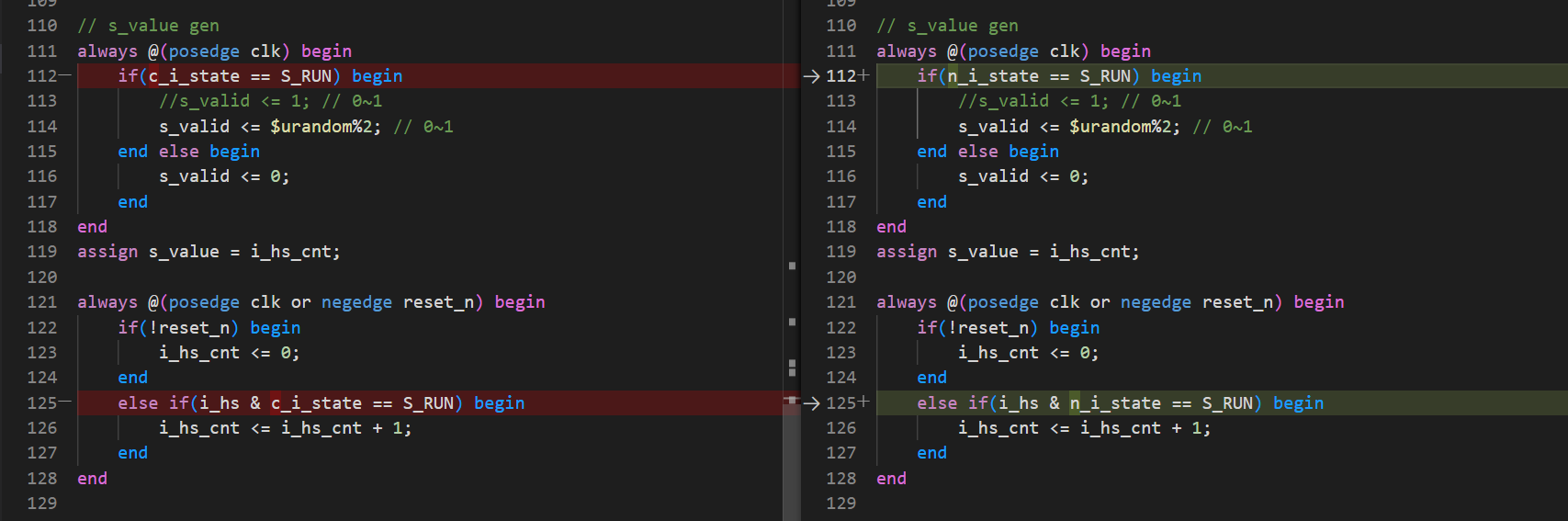

(좌 : 기존, 우 : 수정)

testbench 에서 reg(F/F) 으로 제어하는데, current 가 아닌, next state 로 control 을 하도록 변경하였습니다.

제가 의도한 타이밍은 이게 맞아요.

정답은 없으니, 편하신 것으로 사용하시면 되겠습니다.

이후 챕터에서도 (실습코드 기준 chapter 2,4,6,7) 동일한 이슈가 있어서, 제가 강의에 알려주신 이슈는 공지로 올려놓을께요.

동시에 압축파일도 업데이트 해놓을테니, 공지 올라가면 새로 받아주시면 될 것 같아요.

하시다가 안되는거 있으면 지금처럼 리포팅해주시면 감사하겠습니다!!

저렇게 하면 n_i_state 가 reg 로 선언됐다 하더라도 합성(?) 과정에서 F/F 또는 Latch 로 변하지 않고 wire 처럼 마지막 상태를 유지하는 combination logic 으로 된다는 의미인가요?

네, 맞습니다. 모든 Case 에서 Assign 값이 정의되면 Latch 가 발생되지 않아요.

그리고 always @(*) 블록 안에서 if / else 의 짝을 모두 맞추고 case 문 안에 default 문을 추가한다면 n_i_state 값이 한번만 변할텐데, 어쨋든 코드상으로는 2번 할당 '=' 합니다. 그러면 n_i_state 값이 아주 잠깐이라도 S_IDLE 로 변하는 상태가 발생하는지, 아니면 always @(*) 블록 안에서 최종 할당 값만 고려되어 합성(?)되는 건가요?

이 부분은 제가 드린 코드의 불필요한 중복성 부분이 남아서 그렇고요. (있다면 삭제해주시면 됩니다.)

(별도의 Attribute 를 강제로 주지 않는한, eg. 해당 always 문은 optimize 하지 말아라 같은)

Synthesis 의 원리가 "카르노맵" 과 같이 0,1 Table 을 분석하여 로직을 생성해 줍니다.

예를 들어

A = B;A = C;이렇게 적어두면, A=B 는 무의미 하기 때문에, 합성기의 분석에 의해서 삭제되겠죠.

따라서 최종 할당 값만 고려되어 합성합니다.

해당 코드는 어떻게 Logic 이 구성될까요? 의 답은 (합성을 안해보아도, 대략적으로 예측은 되겠지만) 합성 해보기 전까지 모른다 입니다.

마지막으로, localparam 직접 사용 대신, F/F 의 Q 와 D 가 연결되듯 해도 문제될 건 없는지요?

//n_i_state = S_IDLE; // To prevent Latch.

n_i_state = c_i_state; // To prevent Latch.

위에서 설명드린 합성기의 원리에 따라서, 코드 변경 시 Function 상 문제가 없다면 문제 없습니다.

즐공하세요 :)