인프런 커뮤니티 질문&답변

레지스터 데이터 이동 관련 질문입니다.

작성

·

695

1

안녕하세요, 양질의 강의 늘 감사합니다.

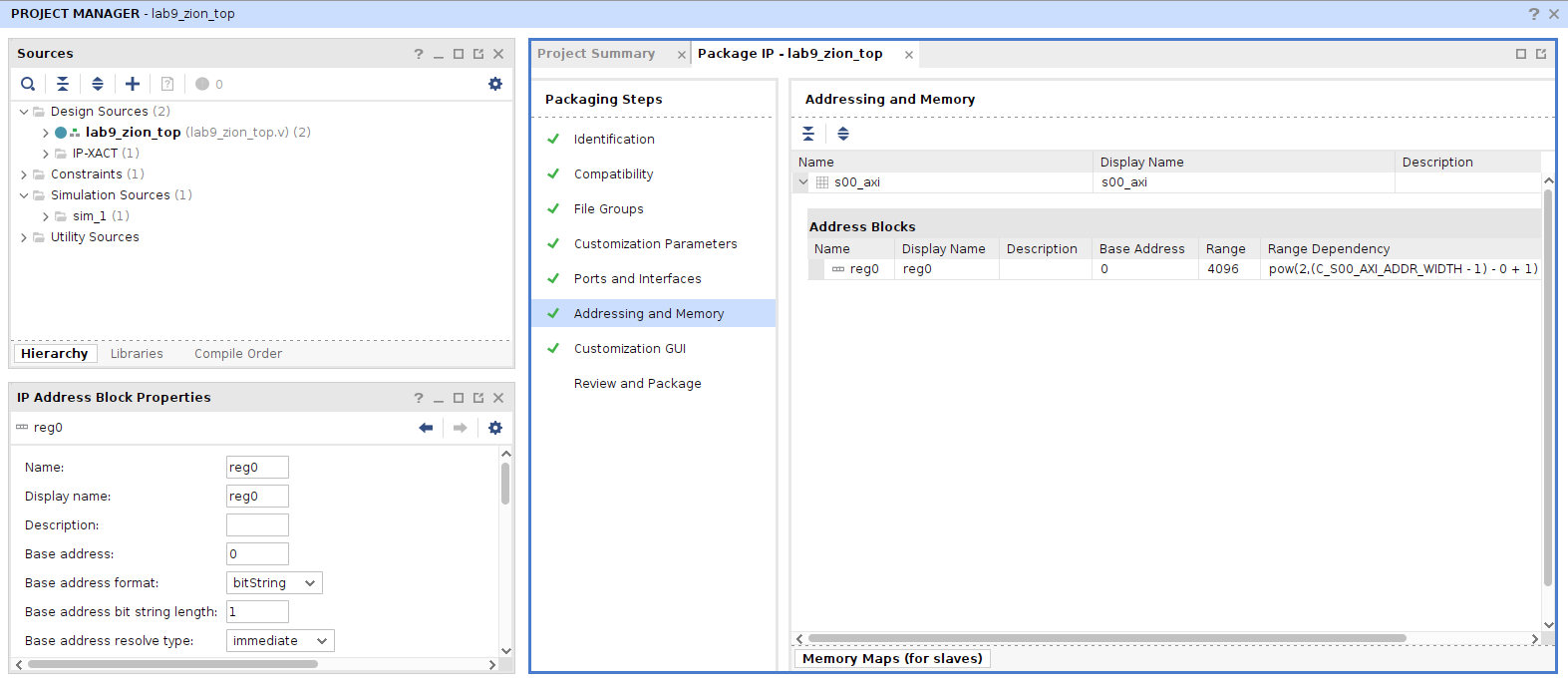

다름이 아니고, 9장 강의를 보고 직접 실습해보던 중 다른 질문에서 올라온 것 처럼 vivado에서 GUI상 address가 다르게 표시되는 문제를 겪었습니다. 아래의 사진입니다.

하지만 IP configuration을 다시 만지니 제대로 뜨기도 하여 tool의 error라고 생각하여 넘어갔습니다.

하지만 Vitis에서 PL 제어를 할 때 LED가 원하는대로 동작하지 않는 것을 확인했습니다. 그래서 vivado에서 디버거로 레지스터 단위로 주소를 확인해보려고 했습니다

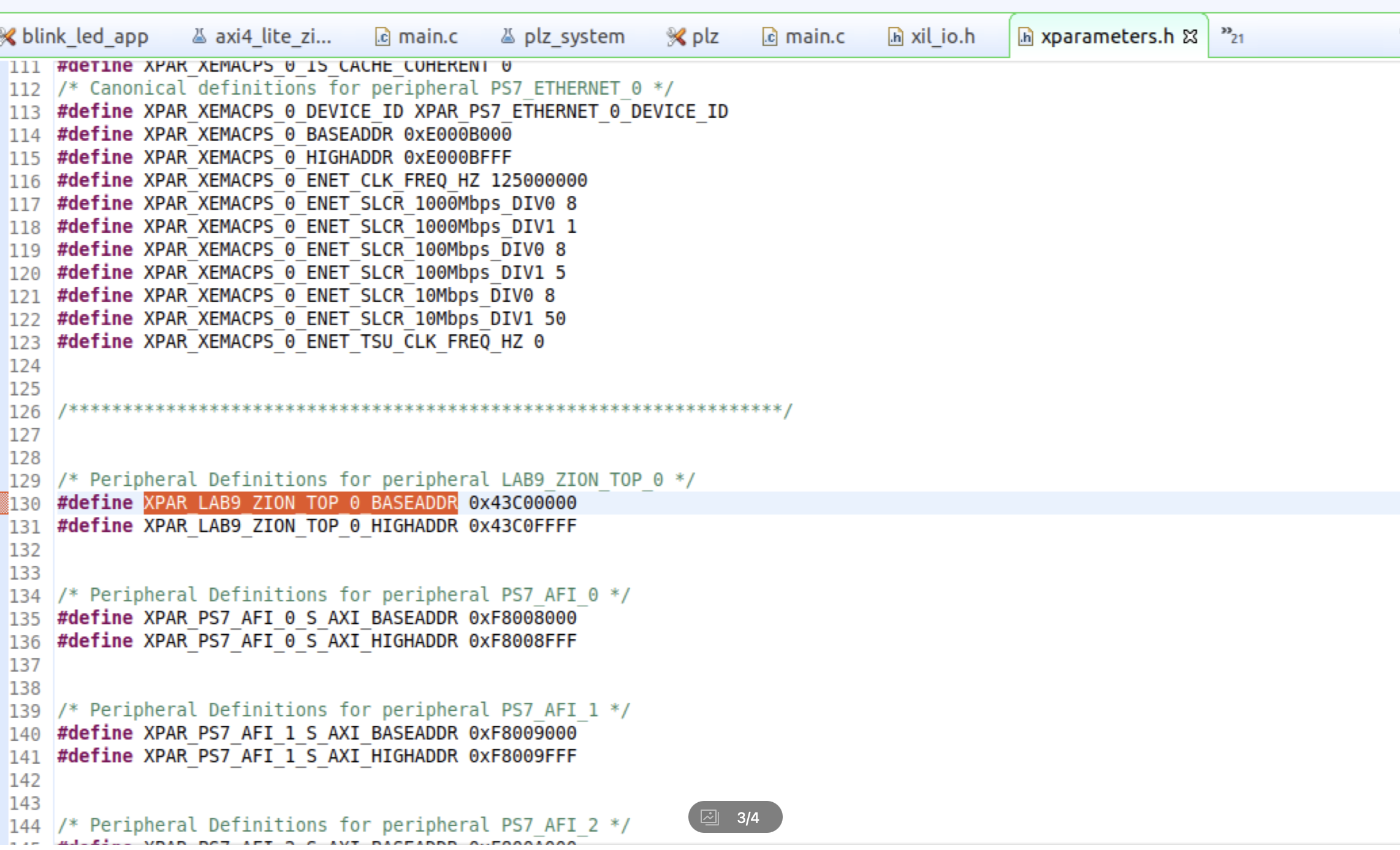

분명 이처럼 base address는 0x43c00000이지만 레지스터에 데이터를 써보아도

분명 이처럼 base address는 0x43c00000이지만 레지스터에 데이터를 써보아도

ARADDR에는 base address가 전혀 반영되지 않고 base address가 0부터 계산되고 있습니다. Xil_Out32의 첫번째 인자에 여러가지 base address를 넣어봐도 reg_num*AXI_DATA_BYTE만 반영되어 0, 4, 8, c .. 이렇게만 주소값으로 들어가네요.. 다음 랩도 주소값을 사용할텐데 진행이 어려울까 걱정됩니다.

ARADDR에는 base address가 전혀 반영되지 않고 base address가 0부터 계산되고 있습니다. Xil_Out32의 첫번째 인자에 여러가지 base address를 넣어봐도 reg_num*AXI_DATA_BYTE만 반영되어 0, 4, 8, c .. 이렇게만 주소값으로 들어가네요.. 다음 랩도 주소값을 사용할텐데 진행이 어려울까 걱정됩니다.

vivado, vitis 2022.1이고, zybo z7-10입니다.

감사합니다ㅜㅜ

답변 4

0

안녕하세요 :)

결론은 저는 잘되고요.

제가 올려드린 프로젝트하고, 갖고계신 프로젝트를 참고해서 찾아보셔요.

Zybo Z7-10 같으신데, 제 생각에는 10,20 의 차이고 질문자님 상황이 재현되기는 어려워보입니다.

vivado : 2022.1

zybo Z7-20

위 조건에서 Test 해보았습니다.

위 링크 보시면,

첫번째 영상은 두번째 프로젝트를 만들기 위한 과정전부를 날 것 그대로 찍어놓았어요.

첫번째 영상은 두번째 프로젝트를 만들기 위한 과정전부를 날 것 그대로 찍어놓았어요.

전부 보실 필요는 없고요.

Vitis 에서 running time 하는 과정 + 마지막 잘 동작한다 과정 까지 봐주시면 됩니다.

저도 오랜만에 해봐서 헷갈리네요;;

두번째 프로젝트 압축파일을 참고해주세요.

졸려서 정신이 없네요;

확인부탁드려요 :)

0

0

결론은 남은 강의에서도 잘 동작할꺼에요.

올려주신 상황을 보았을때 이렇게 해석이 됩니다.

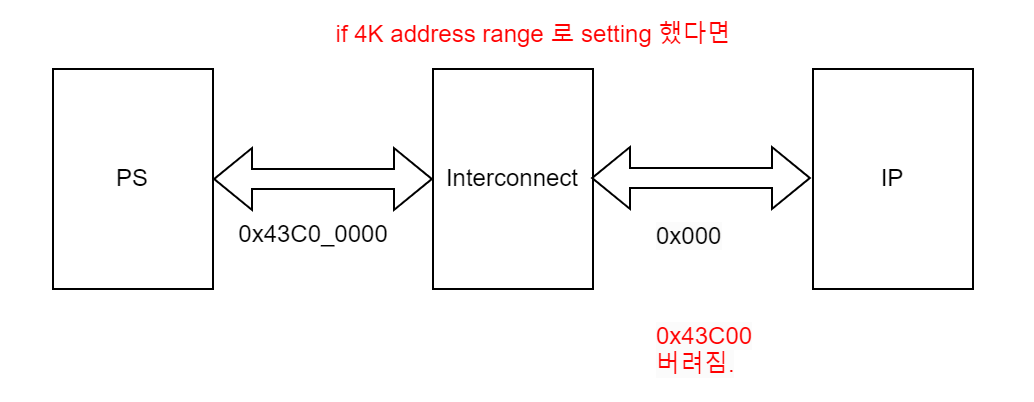

1. PS 에서는 0x43C00000 로 접근.

2. 중간의 Interconnect 를 통해서 IP 를 접근시, 상위 bit 0x43C000 의 대해서는 날림. (정확하게 Range 만큼의 bit width 만 취함. eg AXI4-Lite 의 range 가 4K byte 였다면, 4096 == 2^12 이니. 하위 12 bit은 가져가고, 상위 bit 은 모두 날림. (어떤 HW 가 날렸는지는 정확하게는 모르겠지만, Interconnect 가 PS 내에도 존재해서, 개념적으로는 날리는게 맞습니다.)

3. IP 입장에서는 하위 bit 로 address 를 받음

IP 입장에서는 System 에서 바라보는 상위 bit 는 설계단계에서 알 수 있는 방법이 없습니다.

최종 Address 는 System 관점에서 IP 를 Integration 할 때 알 수 있어요.

그래서 올려주신 현상은 지극히 자연스럽다 생각이 듭니다.

즐공하세요 :)

혹시 영상과 동일하게 따라하셨는데, 이런 현상이실까요?

만약에 맞다면, 올려주신 링크를 확인하기보단 동직하는 프로젝트를 드리는게 더 좋아보이는데요.

확인부탁드릴께요.

https://drive.google.com/drive/folders/1yJqw-JLIfoE8boMJTmYsJqN461WuL9yv?usp=sharing

안녕하세요, 이 링크에 동작하는 영상 첨부했습니다.

의도와는 다른 값들이 레지스터에 들어가는 것 같은데, 저런 식으로 led가 다 켜졌다가 두개만 켜지는 등 입력(vitis에서 넣어주는 값)과는 무관한 동작을 합니다.

code는 주신 자료 그대로 사용한 영상입니다.

0

오늘까지 디버깅 해보았는데, 결과가 일관성이 없어 분석하기에 어려움이 있습니다..! 아무래도 address에 의도대로 접근하지 못하는 것 같은데, 혹시 한번만 확인해주실 수 있으실까요ㅜㅜ.. 만약 툴 문제라면 이제 넘어가고 싶습니다.

현재 상황입니다.

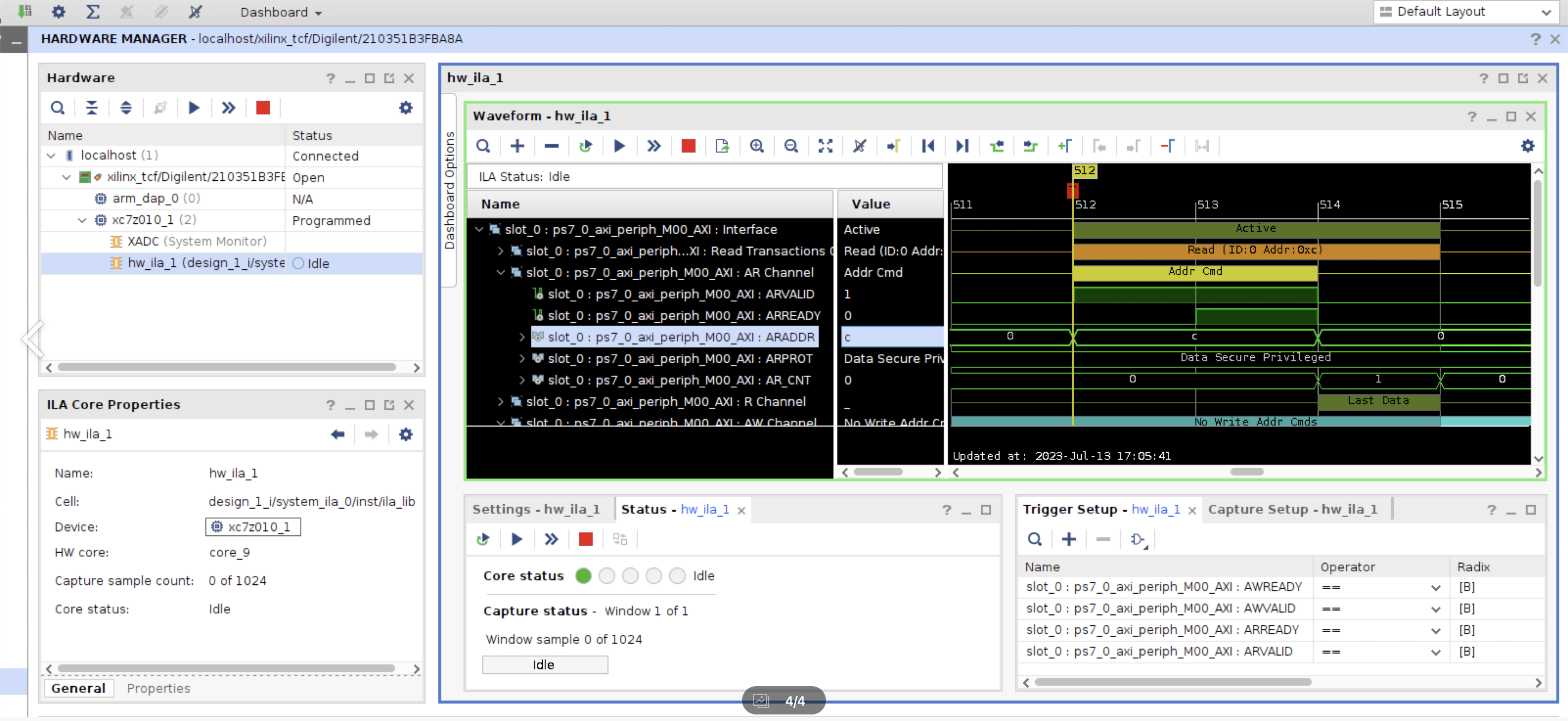

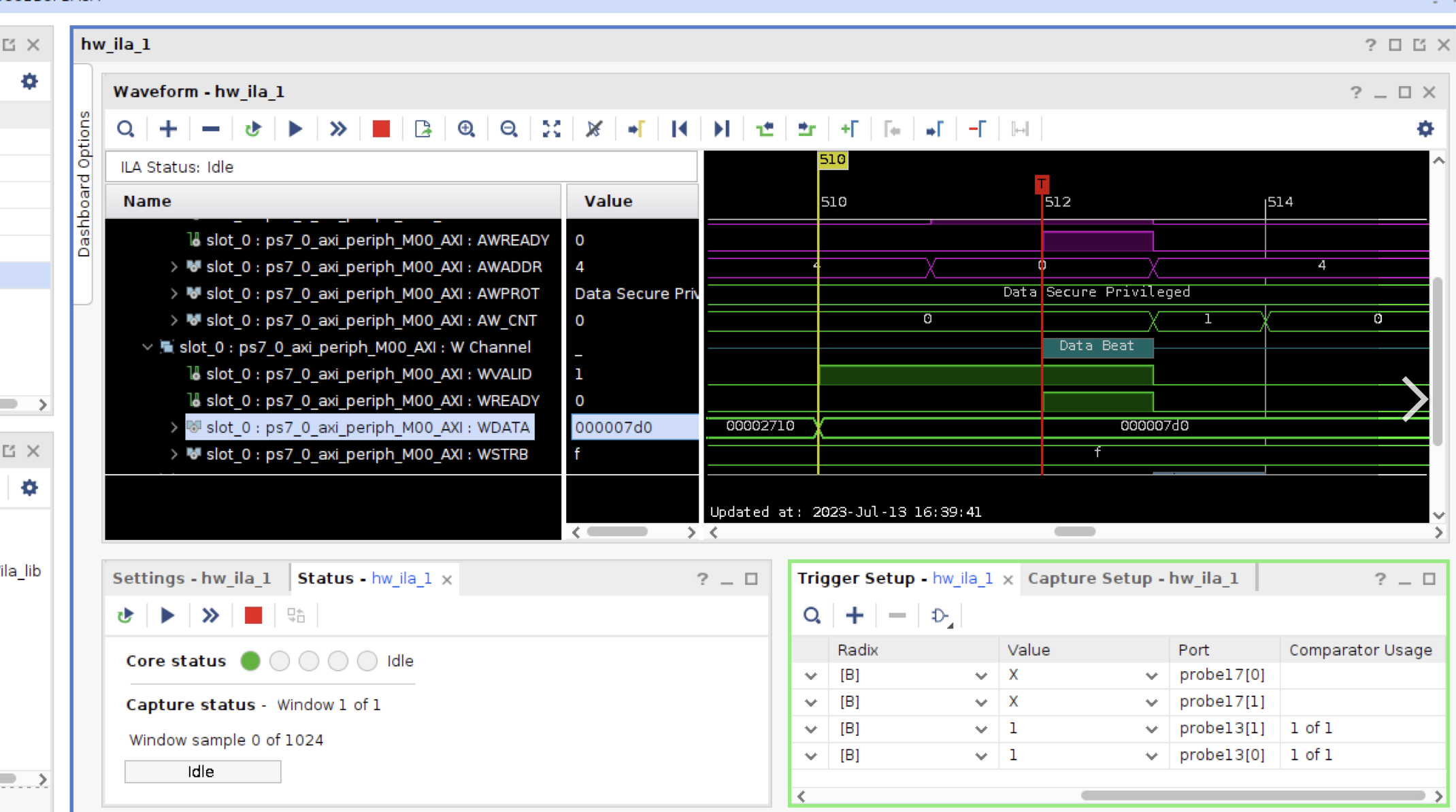

1. write는 되는 것 같습니다. address range에 맞게 하위 12bit에 작성되는걸 waveform에서 확인했습니다.

2. 하지만 레지스터에 쓴 data가 IP의 th_count에 제대로 연결되지 않는 것 같습니다. led가 의도대로 작동하지 않습니다.

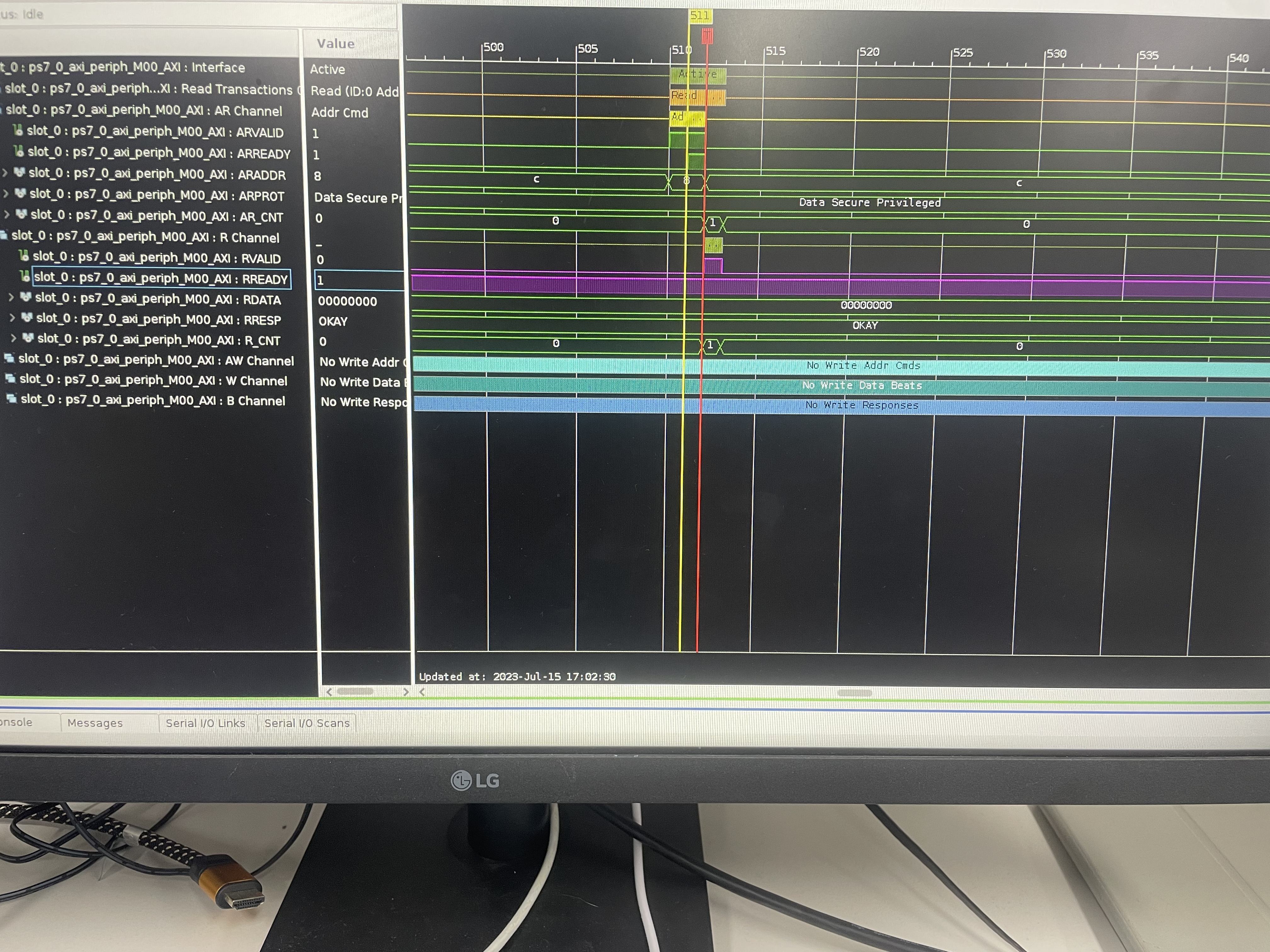

3. read 동작을 했을 때 ILA의 arready 신호가 계속 1로 떠있고 데이터가 RDATA가 알맞게 들어오지 않습니다. 아래는 해당하는 사진입니다. (연구실 컴퓨터 인터넷 문제로 사진 찍어서 보낸 점 죄송합니다 :( )

4. 프로젝트, SW 코드 upload 한 링크 보내드립니다.

https://drive.google.com/drive/folders/1yJqw-JLIfoE8boMJTmYsJqN461WuL9yv?usp=sharing

lab9_zion_fin이 vitis .xsa을 만든 것이고, 혹시 참조한 파일들이 없어서 실행이 안될까봐 IP 만들 때 사용된 파일들도 같이 첨부했습니다. 아래가 그 파일들 입니다.

lab9_zion/lab9_zion.gen/sources_1/bd/design_1/ipshared/7bdc/sources_1/imports/lab9_zion 에 가면 IP에 사용된 .v 파일들이 있습니다.

바쁘시겠지만 부탁드리겠습니다. 정말 감사합니다:)