인프런 커뮤니티 질문&답변

lab2 exam 시뮬레이션 시간 관련하여 질문있습니다.

작성

·

407

·

수정됨

1

안녕하세요 맛비님!

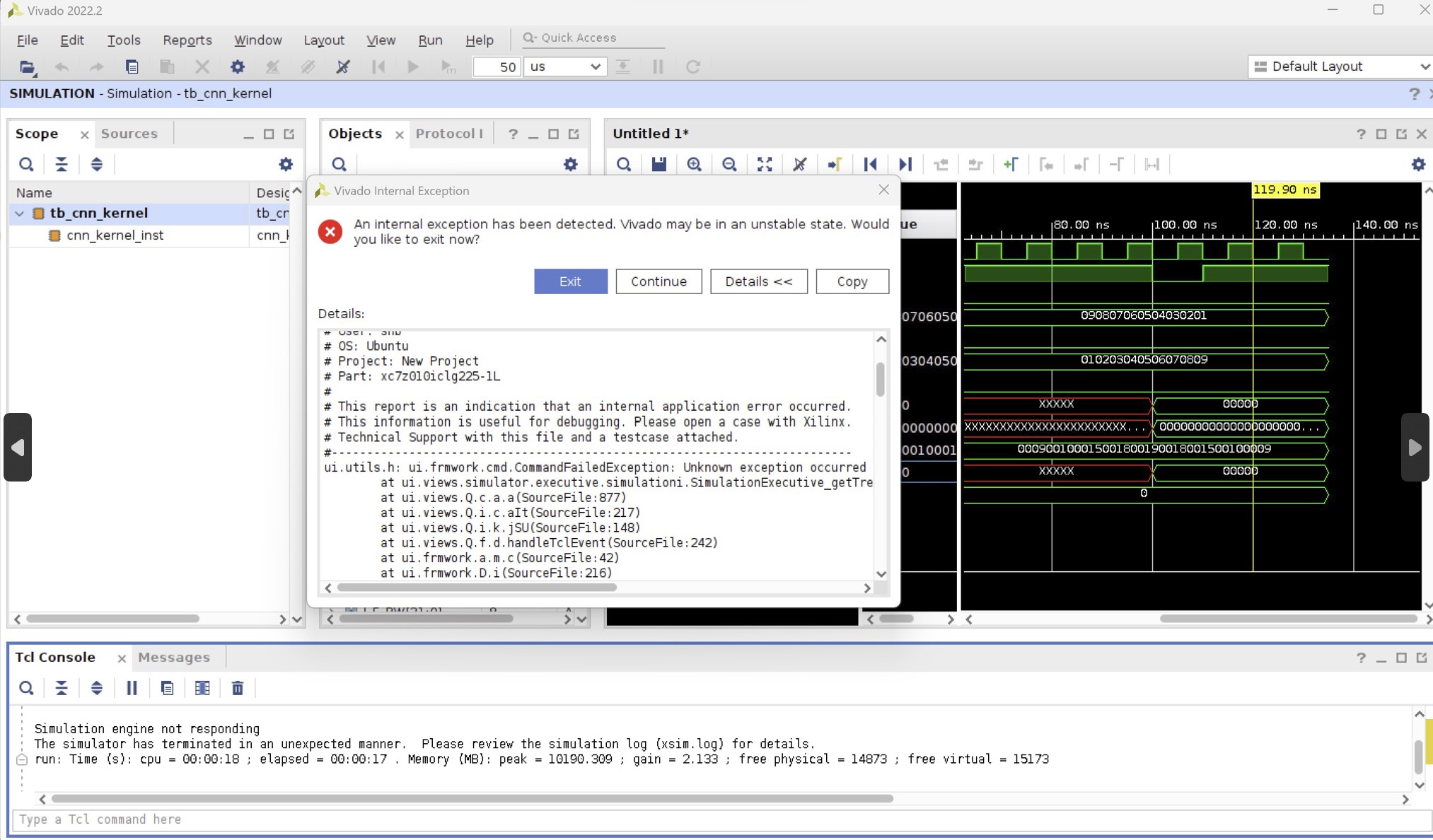

Lab2 exam부분 진행하면서 simulation을 돌릴 때 simulation이 멈추는 문제가 계속 발생합니다..

처음에는 cnn_kernel module이 가장 하위 module이라 이 module이 문제 없이 동작하게 설계하면 다른 module들도 비슷하게 하면 될 것 같아서 제가 따로 testbench 파일을 만들어서 동작을 확인해보려 했는데, input valid 신호가 들어오기 직전 부분에서 자꾸 simulation이 멈춰버립니다...

그래서 제가 구글링을 해봤는데 testbench 작성이 bad 해서 그럴 수 있다는 얘기 정도밖에 안나오네요...(testbench 작성은 지금까지 제공해주신 testbench 파일과 거의 비슷한 flow로 reset_n을 주고 i_in_valid 를 high로 주고 output관찰하려고 했던 단순한 testbench였습니다)

그래서 나머지 모듈도 모두 코딩을 하고 맛비님이 제공해주신 run.py를 통해서 제대로 동작하는지 simulation 해보려고 했는데, 또 simulation이 멈춰버립니다..

여기서 더 진행이 안됩니다..

여기서 더 진행이 안됩니다..

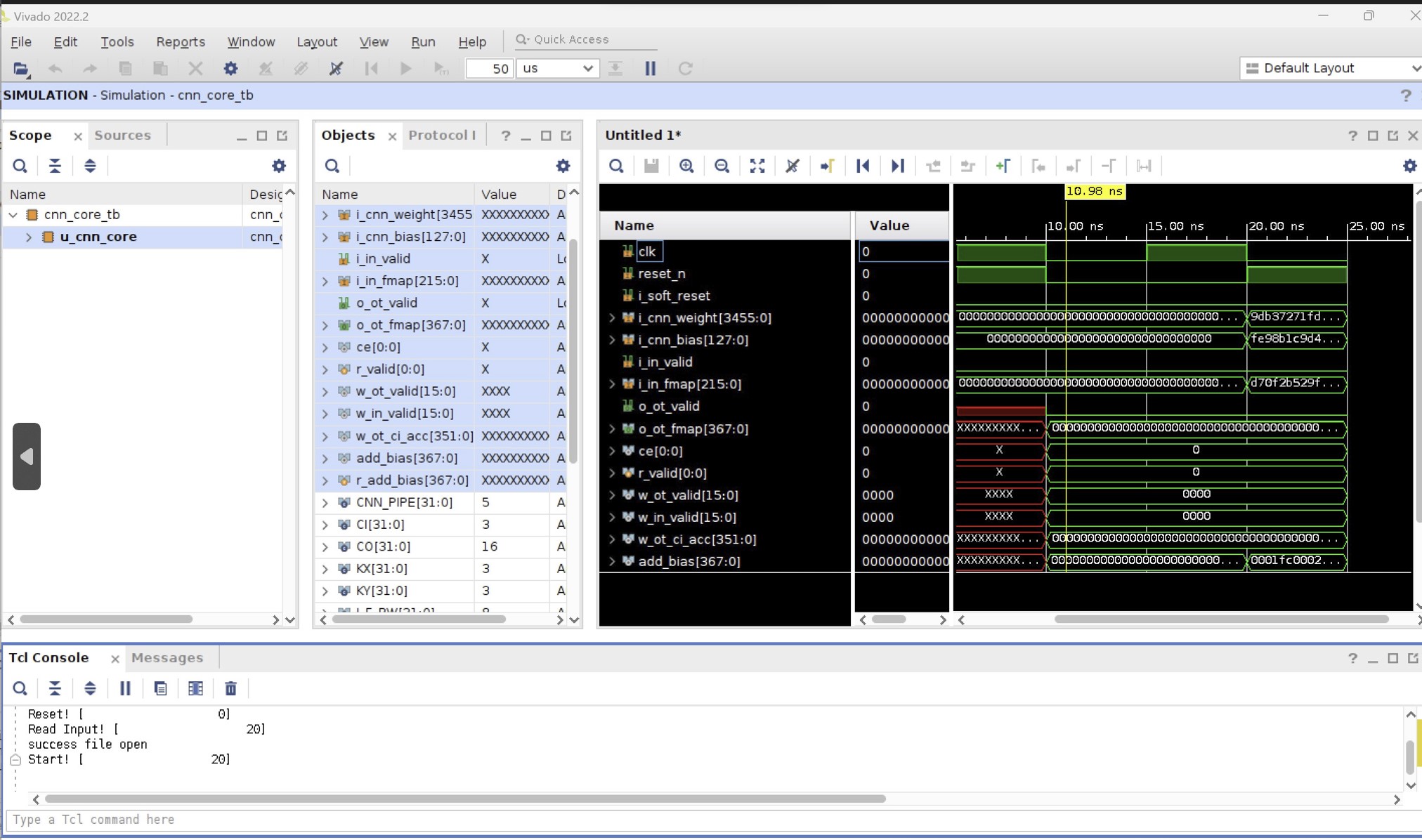

waveform 옵션이 있어서 그런가 하고 그냥 waveform gui없이 돌려봐도 Start이후에 진행이 안됩니다...

강의 중에 3D이상의 array 선언을 하면 simulation time에 문제가 있어 vector 선언 후 Indexed part select를 통해 설계하셨다고 하셨는데, 저도 제공해 주신 frame안에서 그냥 TODO 부분만 Indexed part select를 통해서 코딩한 건데 왜 이런 문제가 발생하는지 잘 모르겠습니다.

제가 작성한 code에 문제가 있으면 simulation 결과를 보고 수정해서 정상적으로 동작하게 하고 싶은데 simulation이 완료가 안되니 어떻게 해야 할지 모르겠습니다... Matbi님의 lab2_solve 부분을 잠깐 확인을 했는데 크게 다르게 작성하지 않은 것 같은데 lab2_solve에서 run.py를 실행해보면 정상적으로 결과가 나옵니다.

Verilog HDL이랑 FPGA강의를 수강해오면서 simulation이 멈춰서 디버깅을 못하는 경우는 없었는데 simulation이 멈춰버리니까 어떻게 디버깅을 해서 진행을 해야 할지 정말 모르겠습니다... 이럴 때는 어떻게 접근해야 하는지 여쭤보고 싶습니다.

긴 글 읽어주셔서 감사합니다!

넵 .. 코드에 문제가 있어서 simulation이 멈추는 것 같은데 build시 warning은 따로 뜨지 않습니다 ㅜㅜ