인프런 커뮤니티 질문&답변

안녕하세요 i2c master 부분에 관련하여 질문있습니다.

해결된 질문

작성

·

523

·

수정됨

0

reg scl_o;

always @(posedge mclk or negedge reset)

begin

if(~reset) scl_o <= 1'b1;

else scl_o <= s_idle ? 1'b1 :

s_start_runw ? ((srw_cnt1==period2) ? ((srw_cnt2==5'd20) ? 1'b0 : ~srw_cnt2[0]) : scl_o) :

s_runw ? (( rw_cnt1==period2) ? ((rw_cnt2 ==5'd19) ? 1'b0 : rw_cnt2[0]) : scl_o) :

s_stop_runw ? ((prw_cnt1==period2) ? ((prw_cnt2==5'd19) ? 1'b0 : ((prw_cnt2>=5'd20)&&(prw_cnt2<=5'd22)) ? 1'b1 : prw_cnt2[0]) : scl_o) :

s_start_runw ? ((srw_cnt1==period2) ? ((srw_cnt2==5'd20) ? 1'b0 : ~srw_cnt2[0]) : scl_o) :

s_runw ? (( rw_cnt1==period2) ? ((rw_cnt2 ==5'd19) ? 1'b0 : rw_cnt2[0]) : scl_o) :

이 부분에서 ~srw_cnt2[0] 부분과 rw_cnt2[0]부분을 왜 이렇게 설계하신건지 알수있을까요?

답변 1

0

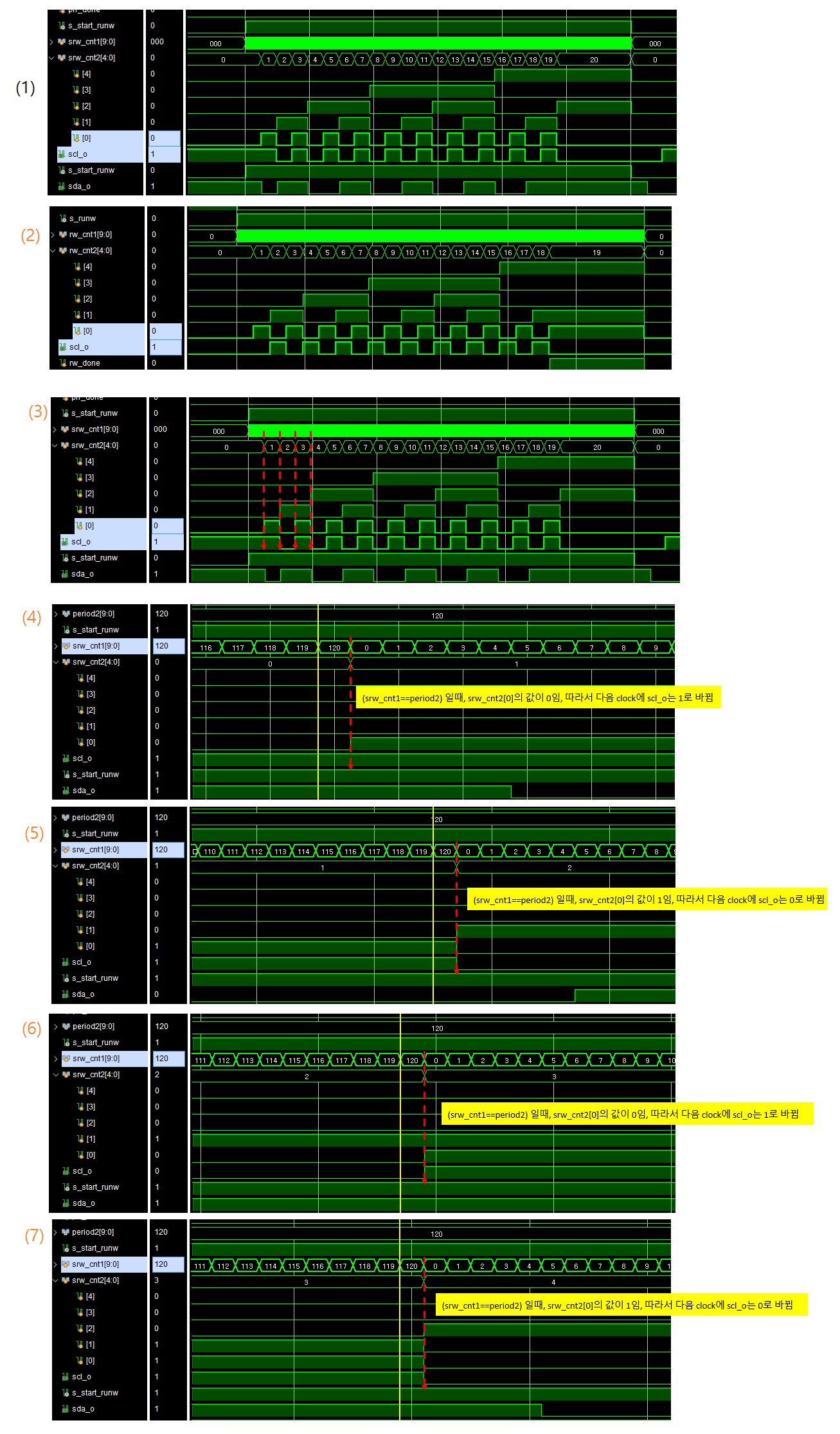

아래 파형 참조하세요.

(파형이 잘 안보이면, 브라우저를 확대해서 보세요)

(1) s_start_runw 전체 파형

(2) s_runw 전체 파형

파형에서 알 수 있듯이, s_start_runw 구간에서는 scl_o : H -> L -> H -> L 로 변하고

s_runw 구간에서는 scl_o : L -> H -> L -> H 로 변하기 때문입니다.

(3) ~ (7) 파형도 참조하세요.

(3) s_start_runw 전체 파형

(4) 첫번째 red line 확대 파형

(5) 두번째 red line 확대 파형

(6) 세번째 red line 확대 파형

(7) 네번째 red line 확대 파형