인프런 커뮤니티 질문&답변

Fault 관련 질문 드립니다.

해결된 질문

23.03.25 15:54 작성

·

346

1

강사님. 강의 잘 보고 있습니다. 감사합니다.

질문이 있는데요.

Hardfault 같은 경우 다양한 원인으로 익셉션이 발생할 수 있는 것으로 알고있습니다.

그만큼 디버깅이 어려운데

설명을 들어보니까 SCB:SHCSR에서 USGFAULTENA, BUSFAULTENA, MEMFAULTENA를 enable하지 않으면 위와 같은 문제가 발생할 경우 전부 Hardfault 익셉션으로 처리가 되는 것 같은데요.

만약 USGFAULTENA, BUSFAULTENA, MEMFAULTENA를 전부 1로 설정하고 각각 익셉션을 정의하면 적어도 어떤 문제로 fault가 발생했는지 더 알기 쉬울 것 같은데 왜 이 값을 default로 설정한 것인지 또 실무에서 자주 사용이 되는지 궁금합니다.

정리하자면 USGFAULTENA, BUSFAULTENA, MEMFAULTENA를 1로 설정하지 않은(default) 상태에서 Hardfault 가 발생한다면 원인 찾기가 어려울 것 같지만, USGFAULTENA, BUSFAULTENA, MEMFAULTENA를 1로 설정하면 디버깅에 좀 더 도움이 되지 않는가?

그런데 왜 default로 설정되어 있는지

실무에서는 많이 사용 안하는지가 되겠네요.

답변 1

0

2023. 03. 26. 08:35

안녕하세요. 김상현님!

질문하신 내용은 CORTEX-M 을 사용하는 개발자라면 한번쯤 궁금하게 생각할 수 있는 주제인 것 같네요. SHCSR 레지스터의 주요 비트(USGFAULTENA, BUSFAULTENA, MEMFAULTENA) 값이 디폴트로 비활성 되어 있으면 개발자가 초기 단계에서 더 간단한 오류 처리 메커니즘을 사용할 수 있게 해주는 장점이 있지 않을까 하는 것이 제 생각입니다. 다만 이 답변은 공식적인 어떤 자료에 근거를 둔것은 아니므로 참고로만 해주세요.

실무에서는 이 기능을 많이 사용하는지 질문하셨는데, 개발자들마다 각자의 선택지가 다를것 같습니다. 오류익셉션은 일반적인 다른 익셉션(타이머, I2C, ADC... 익셉션)들과 달리 개발자가 오류의 원인을 찾도록 도와주는 것이 가장 중요한 목적입니다. 그렇기 때문에 오류 익셉션이 발생되었을 때 하드폴트 핸들러를 이용해서도 그 오류를 쉽게? 찾아 해결할 수 있다면, 굳이 SHCSR 레지스터의 조작 없이 그냥 사용할 것 같네요. 우리에게는 백 트레이스가 있잖아요 ^^

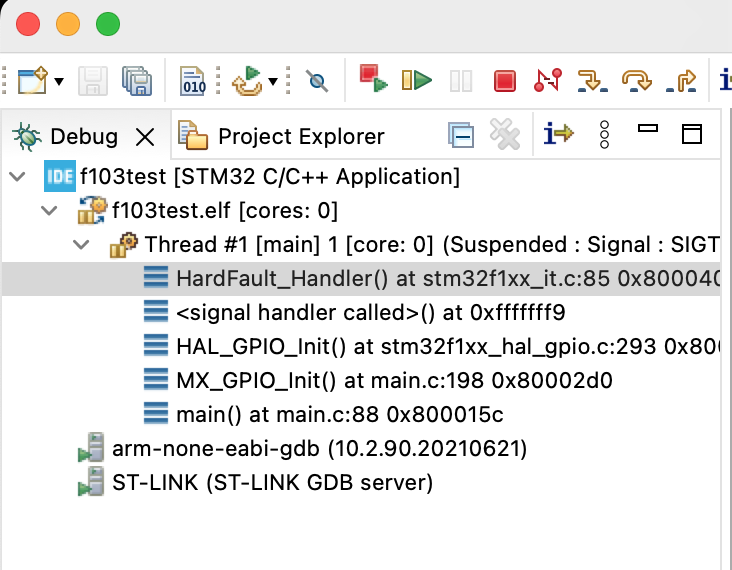

▼자료그림