인프런 커뮤니티 질문&답변

[FPGA 13장] 16regster = Address width는 왜 6인가요?

작성

·

1K

답변 2

0

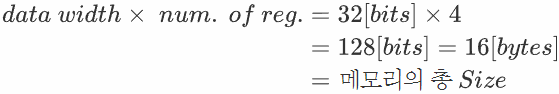

저번 코드리뷰에선

계산한 메모리의 총 Size는 16[bytes]이고

byte단위의 address는 총 16개 라고 볼 수 있고

4개의 입력이 있고 16개(2^4)의 출력이 있는 디코더처럼

4개의 bit로 16을 표현할 수 있기 때문에 4인거고

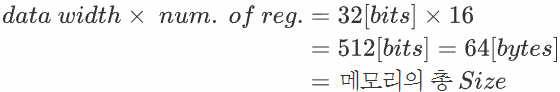

이번 실습편에선

계산한 메모리의 총 Size는 64[bytes]이고

byte단위의 address는 총 64개 라고 볼 수 있고

6개의 입력이 있고 64개(2^6)의 출력이 있는 디코더처럼

6개의 bit로 64을 표현할 수 있기 때문에 6인건가요??

제가 제대로 이해했는지 모르겠어서 질문드립니다 ㅠㅠ

0

설계독학맛비

지식공유자

안녕하세요 :)

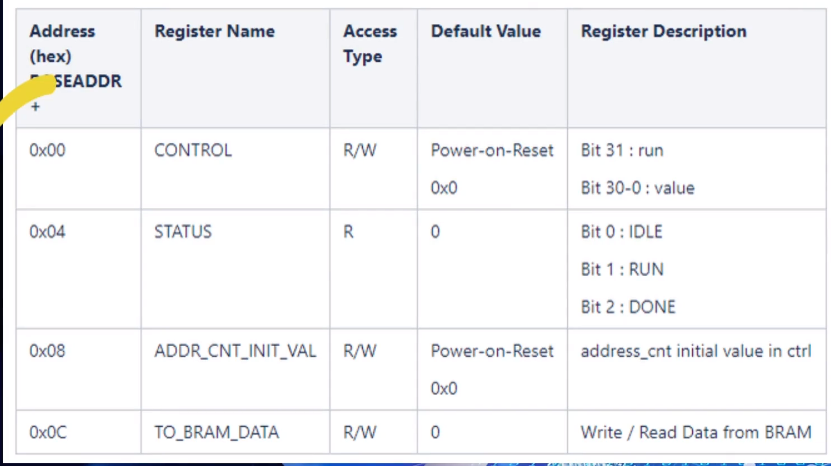

각각의 F/F (register) 은 Address 를 가졌습니다. 0x00, 0x04, 0x08, 0x0c 이렇게요.

Address 의 단위는 Byte 이고요.

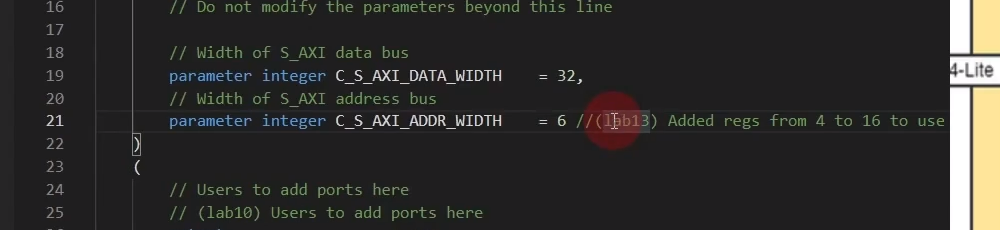

AXI4-Lite 의 data bit width 는 32 bit, 4byte 입니다. 그래서 4 byte 로 주소가 결정되었어요.

그렇다면, 1개의 reg 당 2bit 씩 뛰는거고, 16개는 2의 4승이죠?

그래서 6개의 address bit width 가 되겠습니다.

즐공하세요 :)

Register 16개를 사용한다고 했는데,

Register 16개를 사용한다고 했는데, Address Map에서 Base Address는 4씩 증가하는데,

Address Map에서 Base Address는 4씩 증가하는데,

Byte 단위로 Address 를 계산합니다.

6bit 의 address 가 있으면, 2^6 = 64 byte 를 접근할 수 있습니다.

AXI4-Lite 의 Data width 는 32bit = 4 byte 입니다.

64 / 4 = 16 개의 4 byte reg 를 가질 수 있었습니다.

즐공하세요 :)