인프런 커뮤니티 질문&답변

Lab2 Practice 3 강의 중 genvar 코드 질문입니다.

작성

·

1.3K

·

수정됨

1

안녕하세요,

Lab2 Practice 3 강의에서 cnn_kernel.v 코드에 3가지 질문이 있습니다. (4분 47초 경)

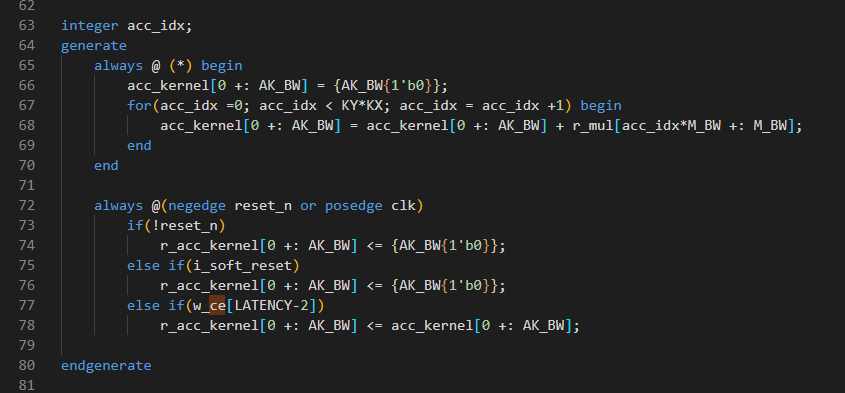

43번 라인에서 사용된 mul_idx 변수는 genvar 키워드로 선언했는데, 63번 라인에서 사용된 acc_idx 변수는 왜 integer 키워드로 선언된건가요?

동일한 generate 구문에서 사용되는데 이유가 궁금합니다.

두번째 궁금증인데요,

코드에서 2번째 generate 구문은 왜 generate를 사용한 건가요?

반드시 generate 가 있어야 simulation뿐만이 아닌 synthesis에서도 for 문을 사용할 수 있기 때문인가요?

3번째는 위 코드 65~70 라인에서

always @ (*) 구문을 사용하는데, 조합회로(맞나요?)인데도 blocking(=)으로 코드를 기술하면 순차적으로 수행되는것으로 이해하면 되는건가요?

좀 더 구체적으로 말씀드리면 for문에서 반복되는 blocking 대입을 unloop 했을 때 코드들의 순서가 보장이 되는지?

감사합니다.

답변 1

0

안녕하세요 :)

문법 질문으로 생각이 되고요. 문법은 스스로 극복하시는 것을 추천드려요.

A1. genvar 와 integer 의 문법은 서로 다릅니다.

다음링크가 도움이 되실꺼에요

https://electronics.stackexchange.com/questions/520681/verilog-for-loop-genvar-vs-int

A2. 중복되는 HW 를 생성하기 위함입니다. (이게 전부... 입니다)

A3. 조합회로 입니다.

좀 더 구체적으로 말씀드리면 for문에서 반복되는 blocking 대입을 unloop 했을 때 코드들의 순서가 보장이 되는지?

순서 보장 됩니다.

즐공하세요 :)

정리를 잘해주셨네요. (제가 알고있느 ㄴ지식도 이정도 입니다.)

맞아요.

(이건 틀릴 수 있는데, 저는 이렇게 사용합니다.) always 내부에서 사용하면 integer, always 외부라면 genvar

always 를 통한 조합회로라면 inteager, assign 을 통한 조합회로라면 genvar (이건 아닐 수 있어요)

정확하지못한 답을 드릴 수 있어서, 앞으로는 강의와 관련된 질문을 꼭 부탁드릴께요. (유독 강의에서 다루지 않은 질문을 많이 올리시는 것 같아요. 그래서 여기에 적습니다.)

다음 링크를 읽어보시면 제 상황이 조금이라도 이해는 되시리라.. 생각합니다.

https://www.inflearn.com/news/312949

문법은 Verilog-2001 (IEEE Standard 1364-2001) 참고 부탁드립니다.

저도 올 여름 때 학생인턴분들하고 완독 계획중입니다. (아직 제 실력이 멀었다는거죠)

즐공하세요 :)

안녕하세요

https://electronics.stackexchange.com/questions/520681/verilog-for-loop-genvar-vs-int

이 사이트와 다른 사이트를 참고해보니,

genvar는 integer와 다르게, 변수가 아니다. 라는 점과,

always 문중 sequential logic문 밖에서 for loop을 사용할 때는 integer가 아닌 genvar를 쓴다.

조합회로 안에 for 문이 쓰인다면 integer를 쓴다

이렇게 세 개 정도 나왔는데, 이 중 틀린 것 혹은 구체적으로 설명해주실 수 있나요?

(생각보다 인터넷에 자료가 몇 없네요,,)