인프런 커뮤니티 질문&답변

10장 질문

해결된 질문

작성

·

453

답변 1

0

설계독학맛비

지식공유자

안녕하세요 :)

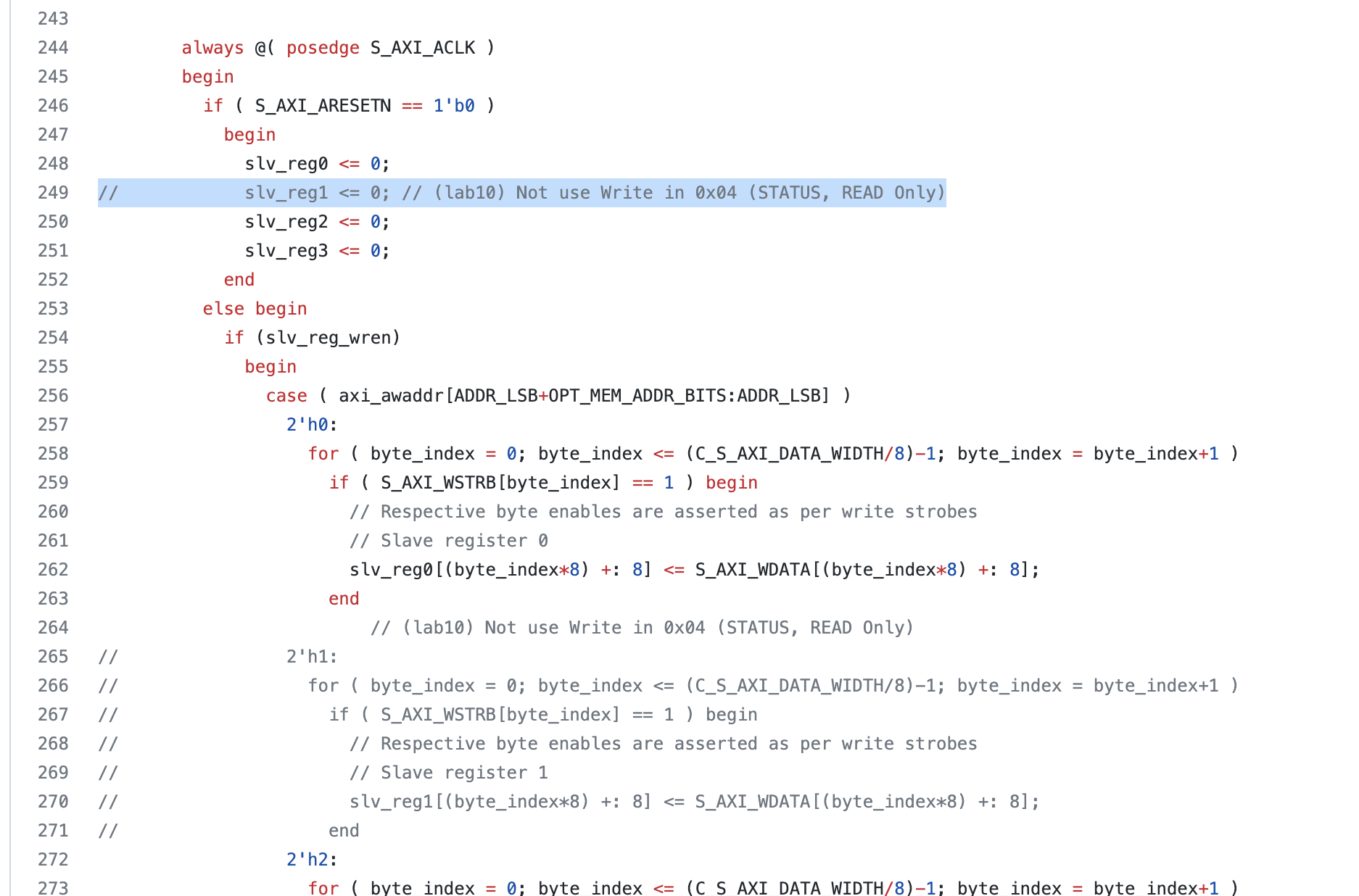

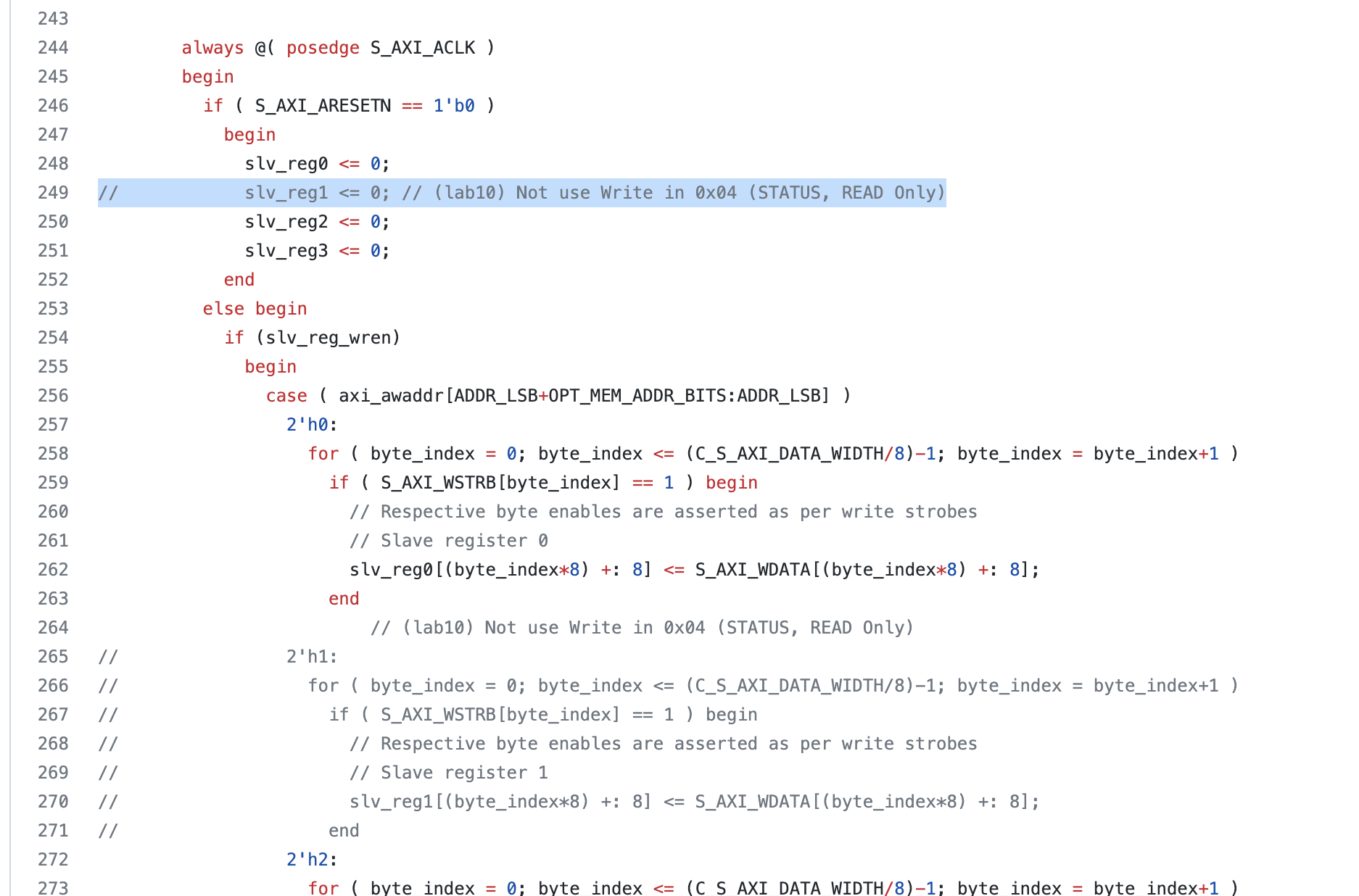

HW 코드를 보시면 답이 될 것 같아요.

1 번부분에는 reg 가 없습니다. SW 에서 값을 쓸 수 없죠.

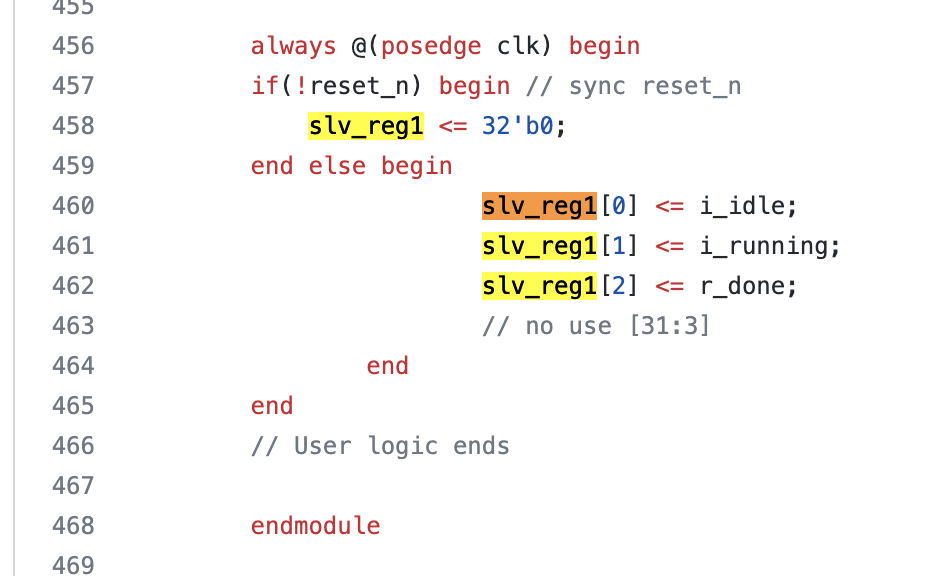

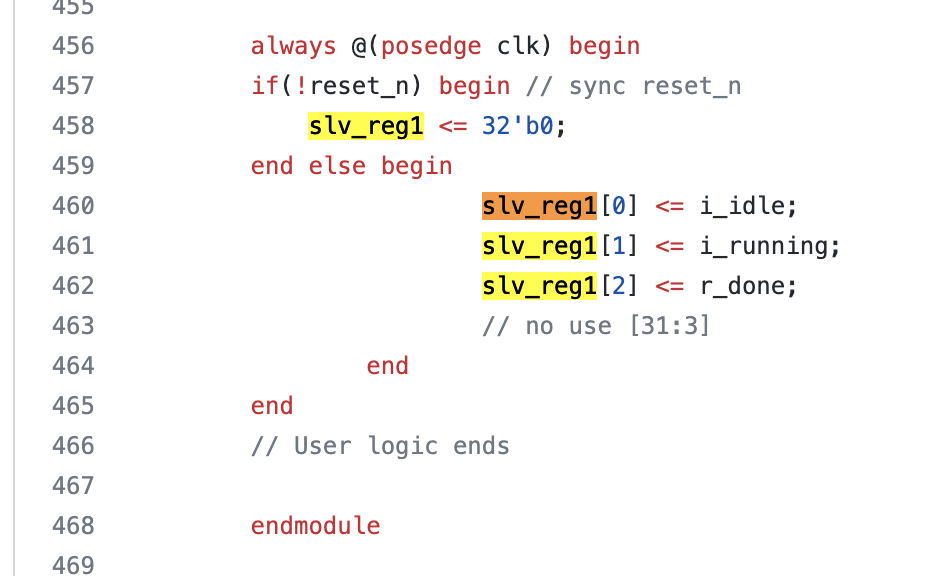

1번은 상태를 나타내고요.

5 라고 하셨으니까, 2'b101 이겠네요.

r_done 이 나왔고, idle 인상태입니다.

즐공하세요 :)

해결된 질문

작성

·

453

답변 1

0

안녕하세요 :)

HW 코드를 보시면 답이 될 것 같아요.

1 번부분에는 reg 가 없습니다. SW 에서 값을 쓸 수 없죠.

1번은 상태를 나타내고요.

5 라고 하셨으니까, 2'b101 이겠네요.

r_done 이 나왔고, idle 인상태입니다.

즐공하세요 :)

이해했습니다

항상 친절한 답변 감사해요!! :)