인프런 커뮤니티 질문&답변

[fsm_hardware_code 질문]

작성

·

747

1

안녕하세요 맛비님,

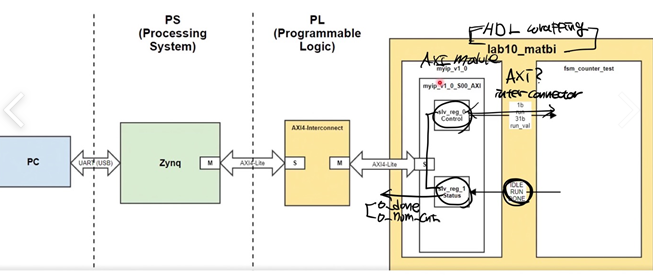

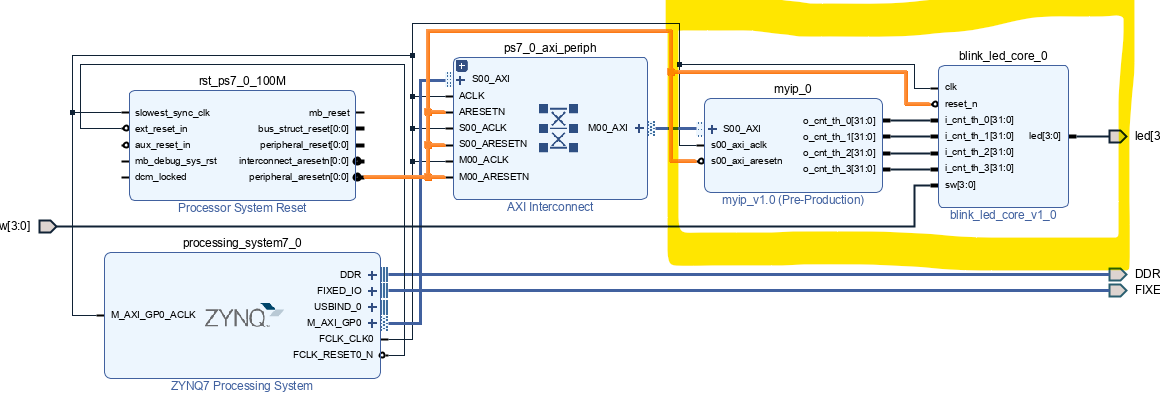

fsm 실습을 진행중에 code 분석을 하다가 질문이 생겼습니다. lab_10_matbi라는 top모듈에 axi4 lite가 counter모듈과 레지스터 2개와 통신하면서, i_run 신호와 i_value값을 주는것은 알았습니다.[그림 1]

하여 비바도 환경에서 counter 모듈을 넣고, create block design으로 IP를 만들고 싶어서, 진행하던 중

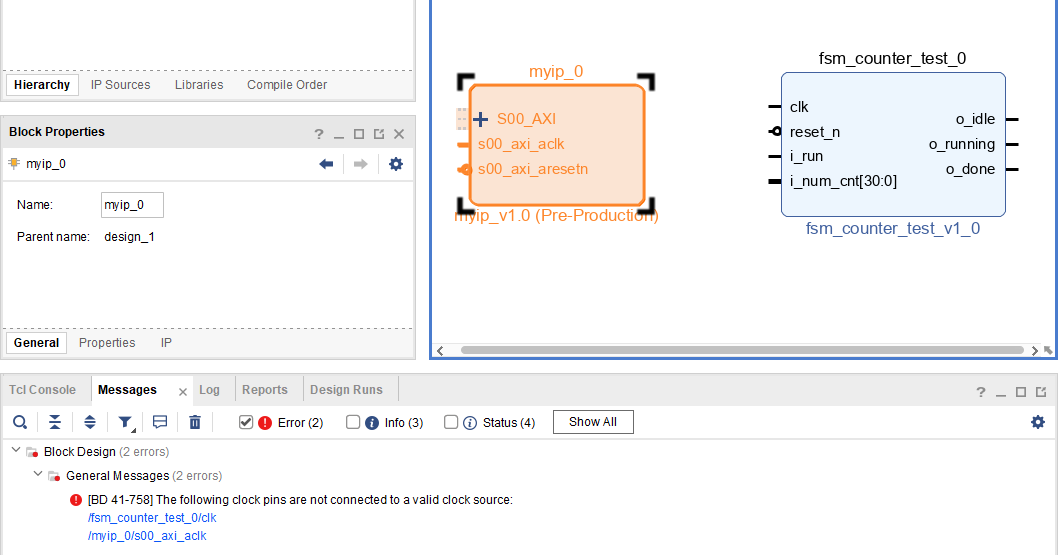

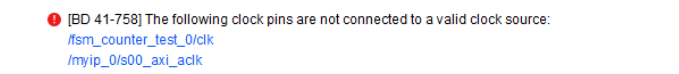

하여 비바도 환경에서 counter 모듈을 넣고, create block design으로 IP를 만들고 싶어서, 진행하던 중 아래와 같이 my ip라는 내부 axi4 모듈과 fsm 모듈을 이어주는데 valid 한 클럭이 없어 automation을 진행하기 어렵다는것을 알았습니다.

아래와 같이 my ip라는 내부 axi4 모듈과 fsm 모듈을 이어주는데 valid 한 클럭이 없어 automation을 진행하기 어렵다는것을 알았습니다.

혹시 IP를 coding을 하여 넣는것이 아니라, create block design으로 만드는 법이 있을까요 ?

감사드립니다 :)

답변 2

0

안녕하세요 맛비님!

시도 도중 제공해주신 topmodule_code를 보고 어떻게 해야할지 감을 잡았다고 생각했습니다!

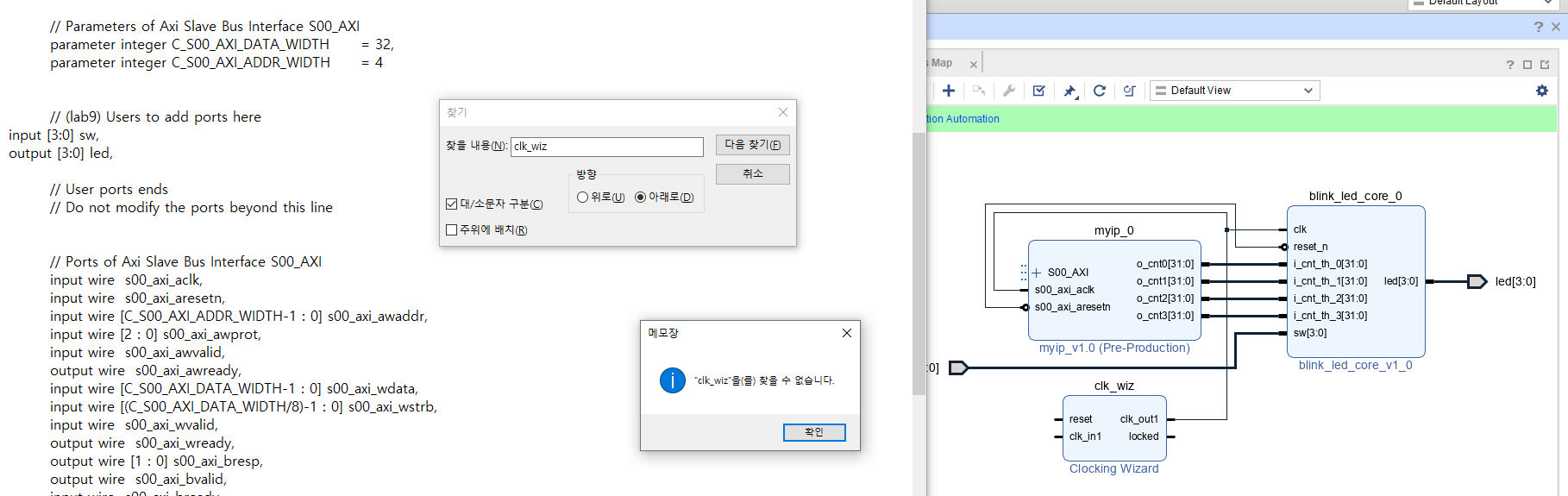

하지만 clk이 없다고 워닝 사인이 떠서 run block auto mation을 해보았는데 갑자기 clk_wiz라는 모듈이 생겨서 top모듈에가서 찾아 보았습니다.

하지만 clk_ wiz부분의 서술이 topmodule에 나와있지 않아서 고민을 계속하던중

질문드리는것이 좋겠다 생각하여 글남깁니다:)

(클럭 부분을 input wire로 뺴야 하는것인지 고려해보았는데 탑모듈 인풋단자에는 external으로 뺀것이 sw,led 밖에 없어서 주저하고 있었습니다)

새해복 많이 받으세요!

감사합니다

안녕하세요 맛비님! 많은 시행착오를 겪으며 많이 배우느라 답변이 느렸습니다.

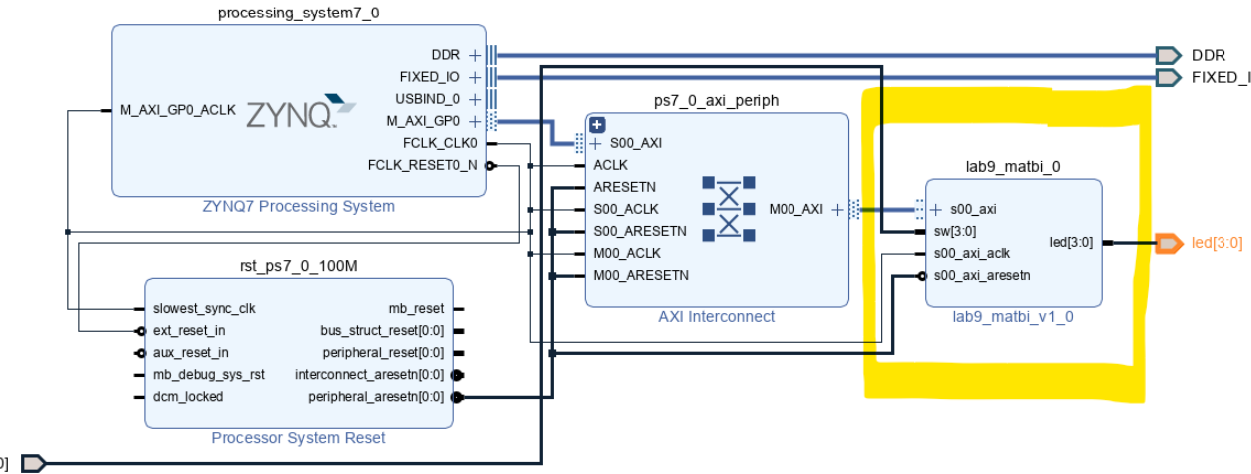

위 BD는 맛비님 께서 만드신것이구

위 BD는 맛비님 께서 만드신것이구

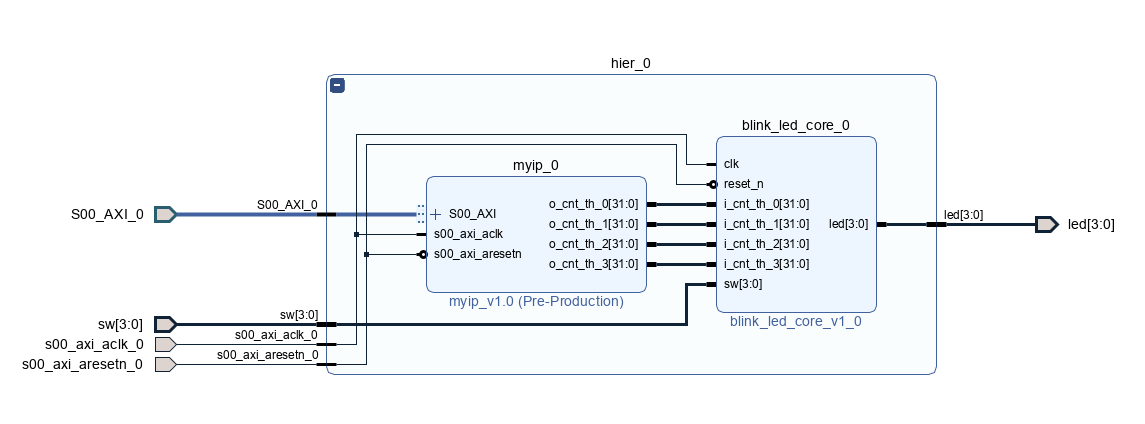

위 BD는 제가 만든 것입니다.

위 BD는 제가 만든 것입니다.

위 질문들에서 제 필력이 약해서 이해가 잘안되어 혼선을 드린거 같습니다.

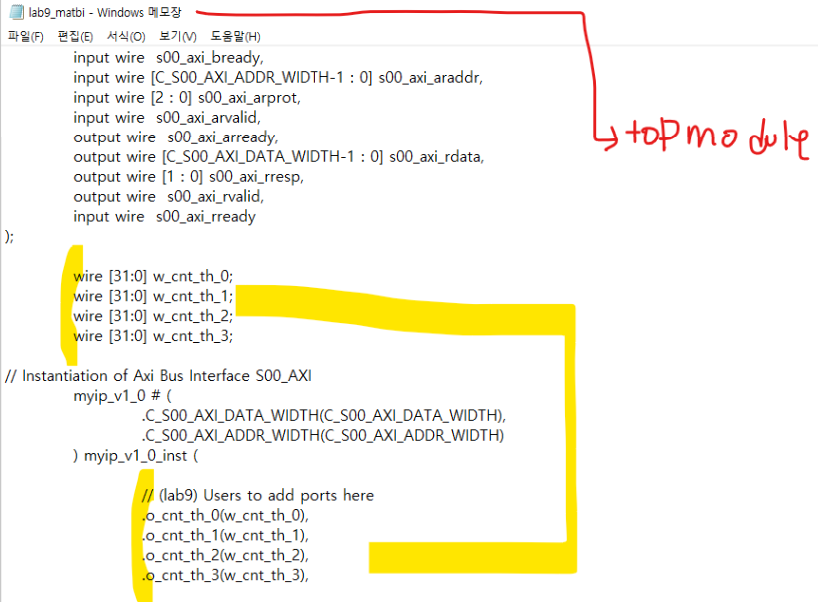

저는 아래의 형광펜 친부분을 위 부분같이 제가 Instantiating Block Designs을 해보고자 하였습니다. 위 질문들도 system clk을 사용하는 것이 아닌 PS clk을 주고 싶은데 HDL wrapping을 하면 위 그림처럼 되지 않을까 하며 시도 해본 것이었구요!

맛비님이 lab9_matbi.v를 어떻게 gui상으로 BD로 만드셨을까 하며 역추적 하며 공부해볼려고 했는데 뜻이 잘전달이 되지 않은것 같습니다. 이부분은 강의와 필수적으로 관련되어 있다고 생각이 들어 다시 질문하게 되었습니다!

아래의 형광펜이 된부분과 위 형광펜이 된 박스를 같게 만들려면 ip wrapping 과정에서 어떻게 진행해야 하나요? (clk이 없이 instance화는 에러가 자꾸 발생하여서 질문드립니다)

=================================================================================

혹시 ip integrater 를 쓰신 것이면 hireachy의 wrapping 된 top모듈상

위와 같은 instanciation은 어떻게 처리해야 하는지 궁금합니다 :)

위와 같은 instanciation은 어떻게 처리해야 하는지 궁금합니다 :)

답변 감사합니다 :)

넵 저두 간단하다구 생각을 했지만, ip 설계에서 vaild clk이 없다고 나와서 잘 안됐거 였습니다.

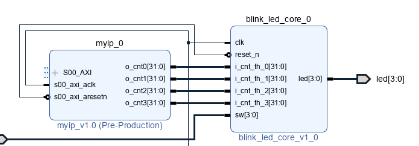

아래와 같이 따로 ip 설계를 wrapping을 하려고 했는데

아래와 같이 따로 ip 설계를 wrapping을 하려고 했는데

위와 같은 에러 사인이 나더라구요.

위와 같은 에러 사인이 나더라구요.

매번 이렇게 성의껏 답변해 주셔서 감사합니다 .

에러리스트에 나온 clk 을 연결할 순 없을까요?

있는데 연결이 안되서 나오는 에러 같은데요..... (개인적으로 수정하신거라 강의와 관련된 질문인지는 잘 모르겠네요ㅠ)

무언가를 해보시는 태도는 박수를 쳐드리고 싶어요. 다만 저의 입장도 생각해주셨으면 합니다...

https://www.inflearn.com/news/312949

양해 부탁드립니다. 난이도를 떠나서 제가 괴롭네요 ㅠ

0

안녕하세요 :)

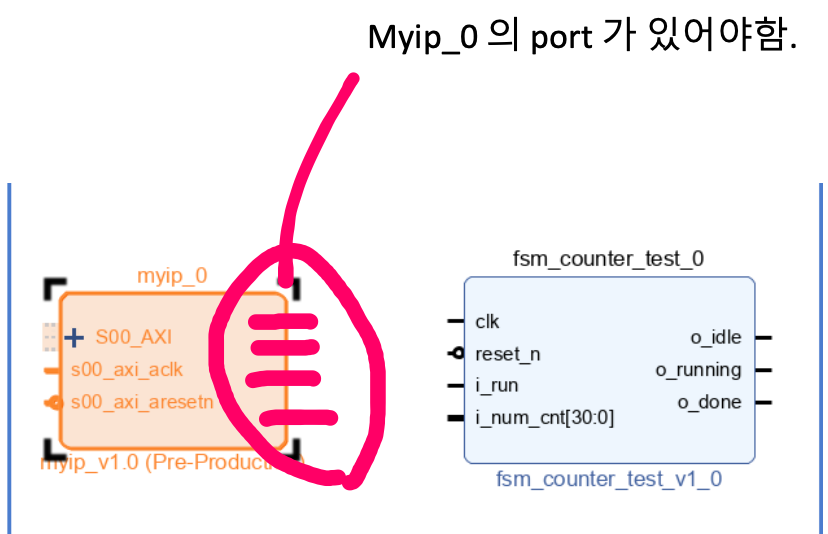

ip 로 만들모듈 (create block design) 의 top 포트를 만들어주시면 될 것 같아요.

port 가 없어서 안나온 것으로 보이고, port 기술해주고 ip 생성해주시면, gui 상에 보일 것으로 예상합니다.

즐공하세요 :)

안녕하세요 :)

(강의내용과 무관한 질문이다 판단은 되는데요....) 개인 질문은 앞으로 양해 부탁드립니다. :)

https://www.inflearn.com/news/312949

=========================================

<들어가기에 앞서>

혹시 보드가 다르실까요? Clock 을 인가하는 방법은 여러가지가 있겠지만.

강의에서 다룬 PS 에서 생성된 Clock 을 그대로 사용하시면 될 것 같은데요.

만약에 PS clock 이 아닌, 지금처럼 외부 Clock 을 사용해서 IP 를 엮으신다고 하셔도.

결국 AXI4-Lite 를 동작시킬 CPU 가 없다는 이야기와 같습니다.

즉, 동작이 불가합니다. 라고 판단이 되네요.

<Clock 사용법>

Clock 사용법에 대해 여쭤보셨으니, 답변드리도록 하겠습니다. Zybo 기준으로 설명드리며, 아니더라도 방법은 동일합니다.

Zybo board 에는 보드 외부에서 125MHz clock 이 들어옵니다. (보드내에 오실레이터가 존재하고 pin 으로 연결되어 있음)

https://github.com/Digilent/digilent-xdc/blob/master/Zybo-Z7-Master.xdc

해당 -name 을 보시면 "sys_clk_pin" 으로 되어 있죠.

즉 해당 xdc 파일을 적용하고, 다음과 같이 input port 를 만드시면 됩니다.

그러면 sys_clk_pin 에 125 MHz 의 clock 은 들어오고 있는 상태입니다.

<clk_wizard>

clock 을 생성하려면 input clock 이 필요합니다.

해당 ip 는, 고정된 오실레이터의 input clk 을 받아서 원하는 Clock Freq 을 생성하는 IP 입니다.

sys_clk_pin 을 clk_in1 에 연결하시고, IP 의 Configuration 을 바꿔주시면 되겠습니다.

=========================

해당 내용은 예전에 해본적이 있네요. (Clock wizard 를 사용하진 않았지만)

https://blog.naver.com/chacagea/220956152746

즐공하세요 :)