인프런 커뮤니티 질문&답변

FSM Code 질문입니다!

작성

·

387

1

안녕하세요 맛비님 고생많으십니다.

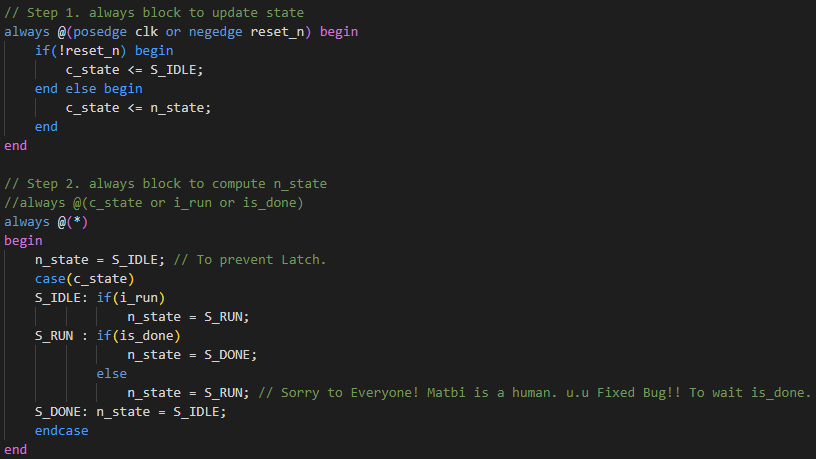

맛비님께서 알려주신 코드는 위와 같으며, 위와 같이 설계할 경우

맛비님께서 알려주신 코드는 위와 같으며, 위와 같이 설계할 경우

예를 들어

c_state 가 A 일 때 output 이 B가 된다고 가정한다면,

n_state가 A로 바뀌면 다음 clock에 c_state는 A가 됩니다. 이 때 바로 output이 B가 되지 않습니다. output은 그 다음 clock에 B가 c_state가 A가 됨을 알아차리고 B가 됩니다.

이렇게 Timing 적으로 출력값이 밀릴 바에

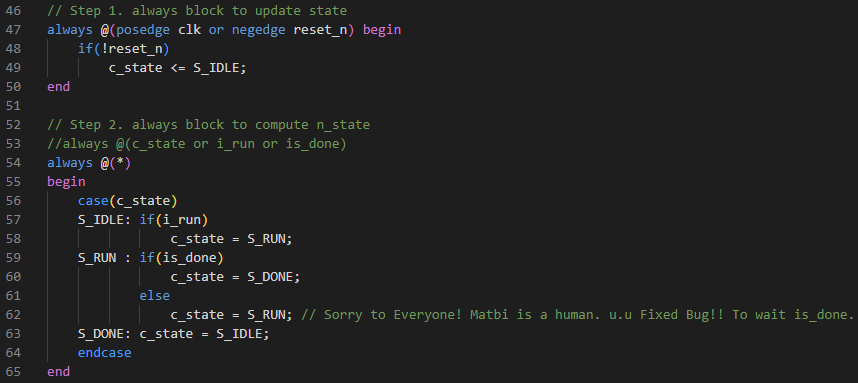

위 사진처럼 바꾸는 것은 어떨까요? (n_state를 없애는 겁니다)

위 사진처럼 바꾸는 것은 어떨까요? (n_state를 없애는 겁니다)

위로 했을 때의 문제점과

문제가 있다면 clock이 안밀리고 위 예시에서 n_state가 바뀔 때 output이 바뀌도록 설계하려면 어떻게 해야할까요?

답변 1

0

안녕하세요 :)

위로 했을 때의 문제점과

동작여부는 잘 모르겠어요. 환경은 전부 드렸으니, 직접 확인해보시는 좋은 방법이 있습니다. :)

syntax error 같은데요..? c_state 를 blocking, non-blocking assign 둘다 사용하셨네요.

문제가 있다면 clock이 안밀리고 위 예시에서 n_state가 바뀔 때 output이 바뀌도록 설계하려면 어떻게 해야할까요?

n_state 를 보고 output 을 출력하면 됩니다.

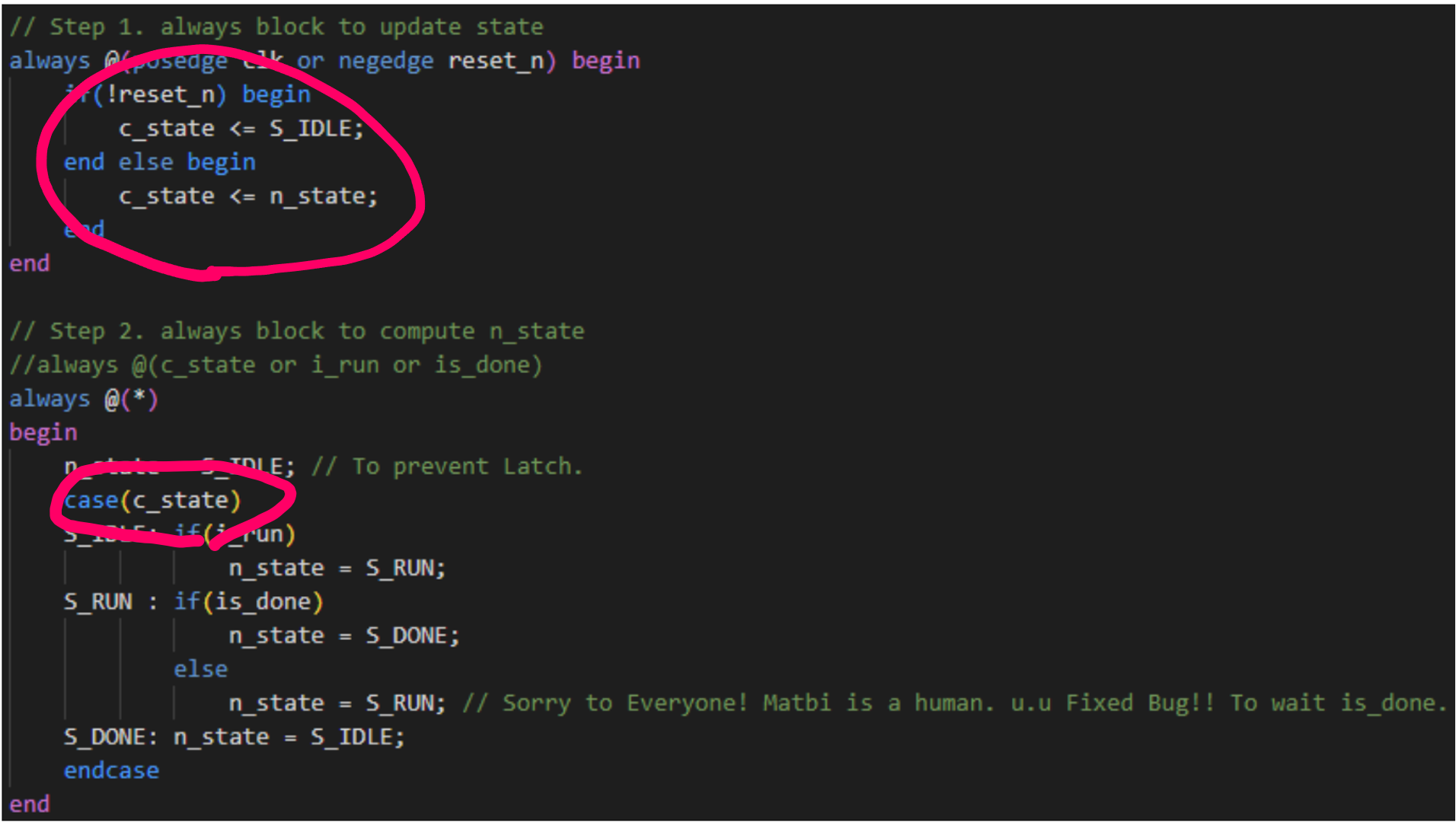

ex. 하기 코드를 a -> b 로 수정. 그러면 n_state 에 맞춰서 output 이 출력될꺼에요.

assign o_running = (c_state == S_RUN);

assign o_running = (n_state == S_RUN);

즐공하세요 :)

맛비님 코드에서는 c_state에 따라 출력값을 결정하던데

엄밀하게 말하자면, 본인이 설계하고자 하는 IP에 따라 c_state, n_state가 출력값을 결정해도 되나요??

(예를 들어 출력값이 A와 B가 있다고 했을 떄

A는 c_state에 의해 결정되고

B는 n_state에 의해 결정되는 식으로 코드를 짜도 되겠네요?!?!)

c_state 는 필요합니다. (현재 상태를 저장해야죠.)

c_state 는 필요합니다. (현재 상태를 저장해야죠.)

답변 감사합니다 :)

맛비님 말씀대로 a->b로 수정되면 c_state는 필요없다고 생각되는데, c_state없이 combinational logic으로 표현된 n_state만 가지고 설계하게 된다면, 이를 FSM이라고 할 수 있을까요?

1) 밀리머신

외부 출력 결정 시 입력과 현재 상태 모두에 영향을 받는다.

2) 무어머신

외부 출력 결정 시 입력이 개입하지 않는다. 현재의 상태만을 보고 출력한다.

만약 c_state 없이 (sequential logic) n_state만 쓰게 된다면 무어머신을 활용한 FSM이라고 봐야하나요?