인프런 커뮤니티 질문&답변

build파일 생성 + 디버깅 관련 질문

22.09.18 17:35 작성

·

429

1

수고많으십니다!

강의 정주행을 모두 마쳤는데, 여전히 혼자서 뭘 만드는 능력이 턱없이 부족해서...다시 정주행 하고 있습니다.

강의를 단순히 따라하는게 아니라, 처음부터 끝까지 직접 만든다고 생각하고 임하고 있는데 리눅스는 도저히 익숙해지질 않네요 ㅠㅠ

강의에서 컴파일 및 실행할 때 ./build를 사용하는데, 이건 이전에 다른 학생분께서 맛비님께 질문한 내용을 보고 build파일을 작성했지만...문제가 있어서 질문드립니다.

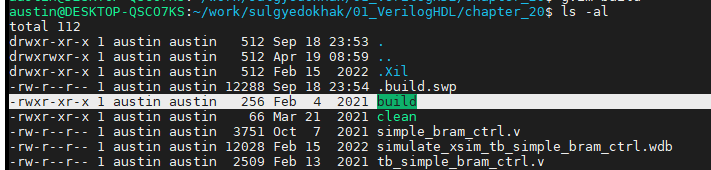

build파일은 확장자 없이 vi (이름) 으로 작성 후 안에 작성하였고, 원본 build와 비교하여 이상 없는것을 확인하였습니다. 실행할 수 없는 파일이길래 chmod +x를 사용해 build를 초록색 실행파일로 만들었지만

/bin/bash: ./build: Permission denied 라는 오류가 나타나는데...어떻게 해야할까요?

강의를 보고 따라하면 컴파일 에러가 없으니 문제가 안되었는데, 직접 코드를 짜면 실수하기도 하죠. 코드에 문제가 있을 경우 이를 디버깅 하는 작업을 해보려 하는데, 컴파일 오류메시지도 기존에 사용하던 modelsim과 너무 다르고 시뮬레이션 할때도 매번 vivado를 재실행해야하는 번거로움이 있습니다. 어떻게 해결하면 좋을까요?

답변해주시면 감사하겠습니다!!

답변 2

1

2022. 09. 19. 09:31

컴파일하고 에러메시지 읽는거는 다시 적응하는 방법밖에 없나 보네요 ㅠㅠ

권한 부여는 말씀하신대로 알아보니까 chmod 777로 하니까 되더라구요!

친절한 답변 감사합니다~

0

2022. 09. 18. 23:58

안녕하세요 :)

Q1. build파일은 확장자 없이 vi (이름) 으로 작성 후 안에 작성하였고, 원본 build와 비교하여 이상 없는것을 확인하였습니다. 실행할 수 없는 파일이길래 chmod +x를 사용해 build를 초록색 실행파일로 만들었지만 /bin/bash: ./build: Permission denied 라는 오류가 나타나는데...어떻게 해야할까요?

A1. 말그대로 실행권한에 문제가 있어서 생기는 문제입니다.

여러가지 이유가 있겠으나 주신정보로만 생각을 해보면,

다음 그림처럼 build 파일에 'x' 가 없음.

계정에 대한 권한이 없음. (예를들어 root 만사용할 수 있게 되어 있다거나?)

build 파일 작성 자체의 오류가 있음

이정도 생각이 나네요.

Q2. 강의를 보고 따라하면 컴파일 에러가 없으니 문제가 안되었는데, 직접 코드를 짜면 실수하기도 하죠. 코드에 문제가 있을 경우 이를 디버깅 하는 작업을 해보려 하는데, 컴파일 오류메시지도 기존에 사용하던 modelsim과 너무 다르고 시뮬레이션 할때도 매번 vivado를 재실행해야하는 번거로움이 있습니다. 어떻게 해결하면 좋을까요?

A2. 네 에러가 날 수 있죠. 저 또한 에러메세지를 보고 해결합니다. 이정도면 나름? 편한 방법이라 생각이 들어요.

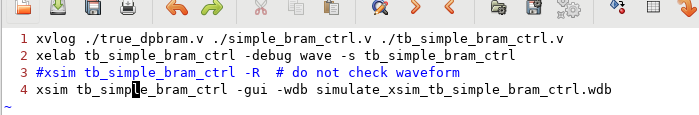

다음 그림은 build 를 open 한 것입니다.

Vivado sim 에서 총 3단계를 거쳐서 waveform 으로 시뮬레이션을 확인하시게 되는데요. xvlog

xvlog

xelab

xsim

위 내용은 구글링 해서 찾아보시기 바랍니다.

여기서, 각 단계를 매번 실행할 필요는 없습니다.

"#" 이라는 키워드를 사용해서 필요없는 단계를 주석처리 하시면 됩니다.

문법 에러만 체크하실 꺼면,

xelab, xsim 을 주석처리하시면 됩니다.

2022. 09. 19. 14:34

현업가시면 vivado simulator 보다 더 좋은? 툴을 사용하실꺼에요. 하지만 전반적인 에러 메세지는 유사하니까, 미리 연습하신다 생각하시면 될 것 같아요 :)