인프런 커뮤니티 질문&답변

Bit Width 설정 관련해서 질문합니다.!

해결된 질문

작성

·

785

2

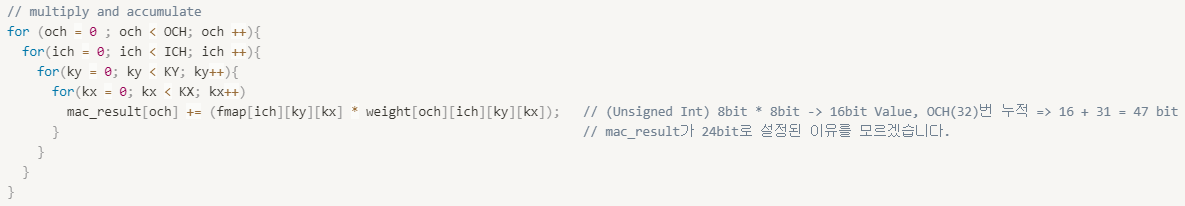

Unisigned Value의 곱셈에 대한 Bit Extension을 통해 16 Bit , 이 값을 32번 누적하게 되면 Overflow를 방지하기 위해 47비트가 필요한 것이 아닌가요? 24비트로 설정된 이유를 여쭤보고 싶습니다!

Unisigned Value의 곱셈에 대한 Bit Extension을 통해 16 Bit , 이 값을 32번 누적하게 되면 Overflow를 방지하기 위해 47비트가 필요한 것이 아닌가요? 24비트로 설정된 이유를 여쭤보고 싶습니다!

답변 1

0

설계독학맛비

지식공유자

안녕하세요 :)

말씀하신대로 Unsigned type 의 fmap, weight 를 사용했다면 Overflow 가 발생합니다. :)

C 로는 HW 의 결과값과 동일한지의 matching 용도의 modeling 이고요.

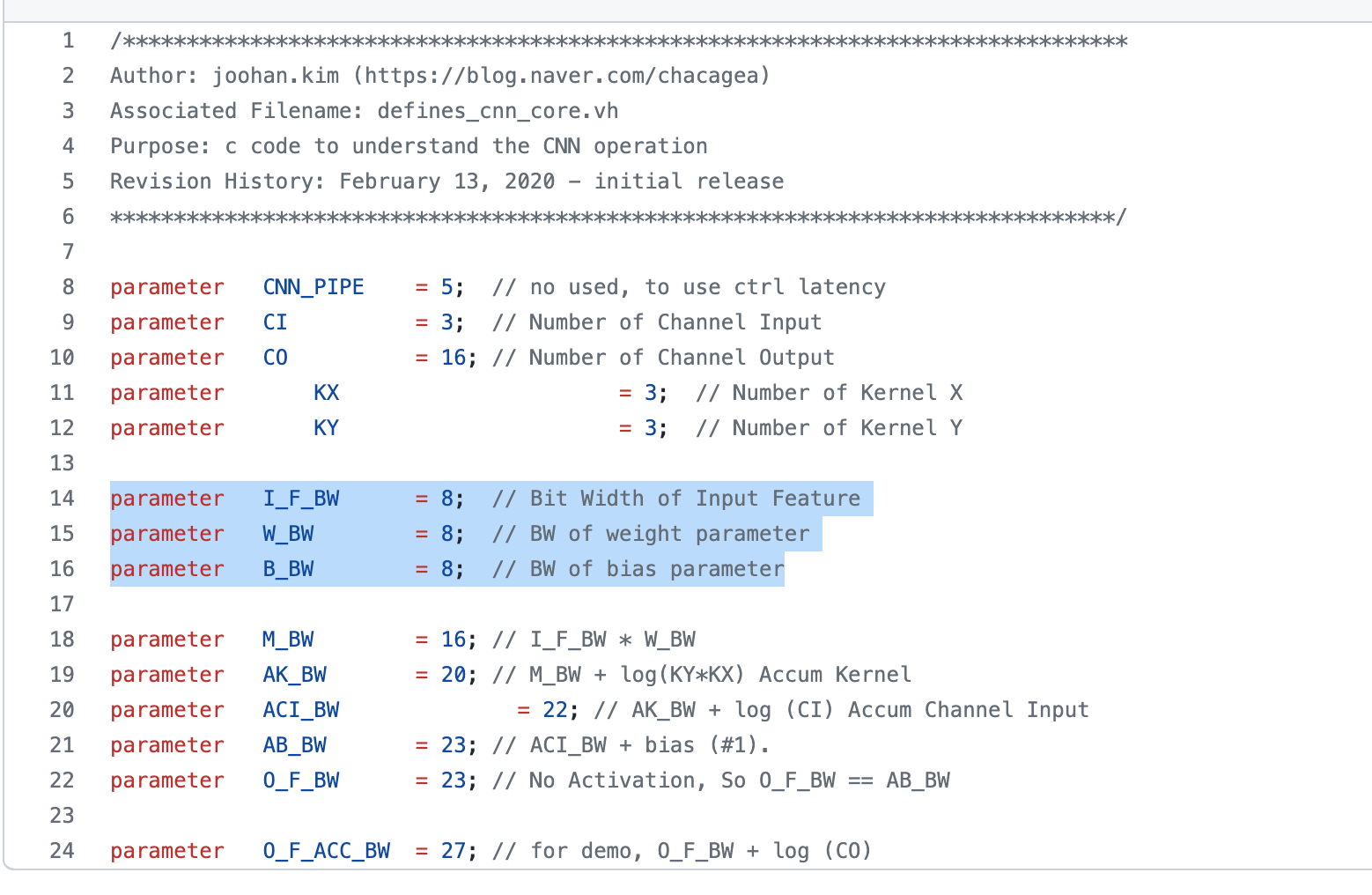

HW 실습까지 보셨는지 모르겠지만, fmap, weight 의 bit width 는 8b 입니다.

위 Parameter 들의 bit width 값을 고려해보시면, 필요한 bit 수가 계산이 되실 거에요.

위 Parameter 들의 bit width 값을 고려해보시면, 필요한 bit 수가 계산이 되실 거에요.

즐공하세요 :)

설계독학맛비

지식공유자

헷갈리신 부분을 이해했습니다. 다음 내용만 설명드리면 되겠네요.

16bit 가 32 개 누적이면 31bit 이 아닙니다.

16bit + 5bit (2^5) 인 21b 이 필요하겠네요. (저의 예제는 OCH 는 16 개 이니까, 20b 입니다.)

생각해보시면,

unsigned 16 bit 의 max 값은 65536 (2^16) - 1 인 65535 입니다.

이를 32 번 더했다고 생각해보셔요.

그러면 65535 * 32 가 Max value 가 되겠죠? (2097120 입니다.)

이는 21bit 면 충분히 표현가능하죠.

2^21 = 2097152

위 내용을 이해하신다면, 해결이 되실 것 같아요. 이후 내용은 스킵할께요.

즐공하세요 :)

답변 감사합니다.!

주석으로 달아 놓으신 Bit Width 부분이 이해가 잘 되지 않아 다시 여쭤보려고 하는데요.

fmap과 weight의 bit width는 각각 8bit로 이 둘의 곱셈을 하게되면 overflow를 방지하기 위해

총 16bit가 필요한 것이 아닌가요? 이 16bit Data를 총 OCH(32)만큼 누적을 하니까 총 31bit 만큼

비트를 늘려주어야해서 mac_result에 대해서는 총 47bit가 필요한 것이 아닌가 여쭤보고 싶습니다.

( mac_result 부분에서 16 + 4 + 4 = 24bit로 계산된 부분이 잘 이해가 되지 않습니다. )