인프런 커뮤니티 질문&답변

case문 우선순위

작성

·

1.4K

1

안녕하세요

다른 분께 남겨주신 if-else문과 case문의 차이에 대한 답변을 봤는데, case문은 우선순위가 없다는 말에 대해 혼란이 생겨 질문 남깁니다.

기존에 verilog를 학습했을때, verilog의 case문은 C의 switch case문과는 다르게 각각의 조건에 break가 있는 것과 같다. 그래서 맨 위 조건부터 우선순위가 있다고 알고있었는데요.

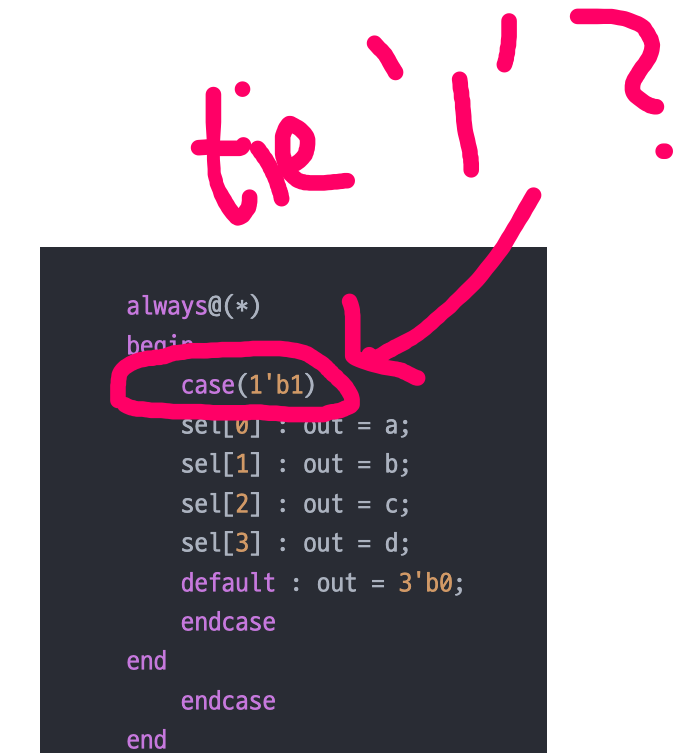

예를 들어 아래의 모듈의 시뮬레이션 결과로 sel=4'b0011인 경우에 out=a가 나옵니다. 따라서, case문에서 맨 위 조건부터 우선순위가 있다고 생각했습니다.

module priorityencoder(

input [2:0] a,

input [2:0] b,

input [2:0] c,

input [2:0] d,

input [3:0] sel,

output reg [2:0] out

);

always@(*)

begin

case(1'b1)

sel[0] : out = a;

sel[1] : out = b;

sel[2] : out = c;

sel[3] : out = d;

default : out = 3'b0;

endcase

end

endcase

end

endmodule그런데, 남겨주신 답변에 case문에는 우선순위가 없다고 하셔서 조금 혼란이 생겼는데..

말씀하신 'case문에 우선순위가 없다'는 말은, 코드상의(=function상의 ) 우선순위를 말하는 것이 아닌

합성에서 생기는 우선순위(?)가 없다는 말로 생각하면 될까요?

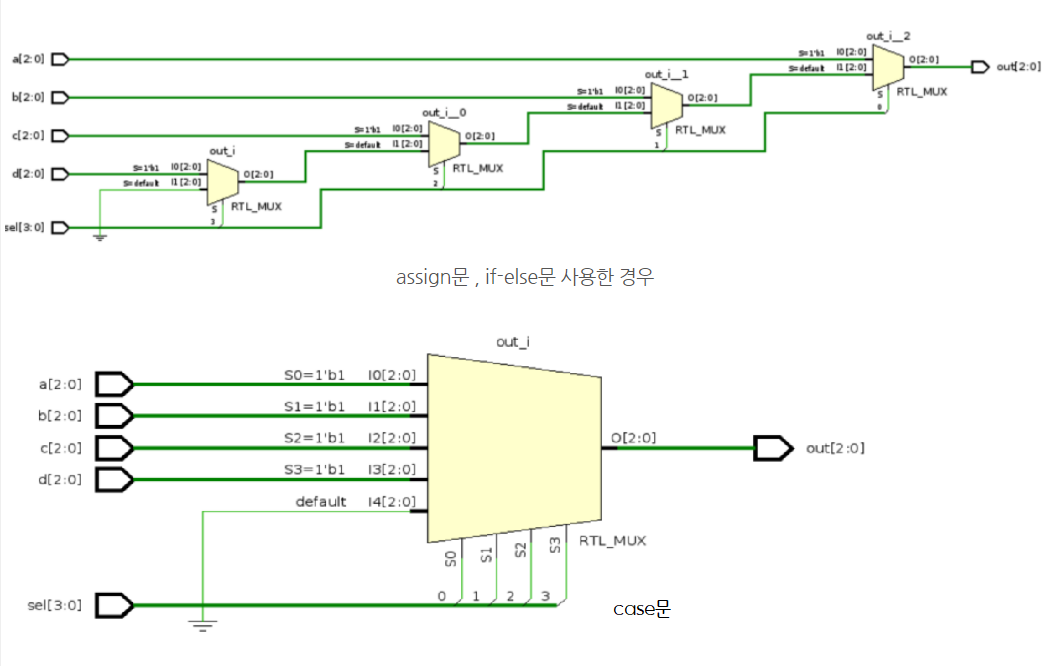

(위의 예시 모듈을 합성하면 아래 그림처럼, if-else로 적으면 mux chain형태로 합성되고 case로 적으면 하나의 mux로 합성됨을 확인하긴했습니다..) 그러면 이렇게 case문이 합성된 회로(위 그림의 아래의 회로)는 그럼.. function적으로는 우선순위가 있는데 형태는 우선순위가 없는(??)것.. 인건가요?

그러면 이렇게 case문이 합성된 회로(위 그림의 아래의 회로)는 그럼.. function적으로는 우선순위가 있는데 형태는 우선순위가 없는(??)것.. 인건가요?

답변 1

0

case 조건이 왜 1'b1 fix 인지 모르겠으나... 그건 주제에 벗어나니, 답변을 시작해보겠습니다.

먼저 혼란을 드려서 죄송합니다.

습관이 이렇게 무섭네요. + 저의 무지로 인한.. ㅠ

(제 습관은 priority 가 존재하는 경우라면 if-else 를 사용하고, 그 외의 priority 가 필요없는 경우에는 case 문을 사용합니다.)

case 문은 priority 가 존재합니다. 하지만 priority 가 없게도 가능합니다.

다음 처럼 full case (latch 방지) + parallel case (조건에 종속성이 없음) 일때는 priority 가 없고요. 평소에 이런식으로만 case 문을 쓰다보니..;; Test 하신 case 문 결과가 Single Mux (N to 1) 로 완성되었다면, priority 는 없습니다.

(ref link : https://www.chipverify.com/verilog/verilog-case-statement)

module my_mux (input [2:0] a, b, c, // three 3-bit inputs

[1:0]sel, // 2-bit opt for signal to choose on from a, b, c

output reg [2:0] out); // Output 3-bit signal

always @ (*) begin

case(sel)

2'b00 : out = a; // If sel=0, output can be a

2'b01 : out = b; // If sel=1, output is b

2'b10 : out = c; // If sel=2, output is c

default : out = 0; // If sel is something, out is commonly zero

endcase

end

endmodule 알고 계시겠지만, priority 가 필요없는 경우라면 case 문을 통해서 작성하시는 것이 좋습니다.

priority 가 존재한다는 것은 logic 의 delay 와 그리고 필요이상의 로직을 사용하게 할 수 있습니다.

그럼 case 문의 priority 를 완전 쓰지 말라는것인가..? 그건 또 아니고요. (case 문 자체가 파고들면 헷갈리는 부분이 많고 저도 아직 부족한지라, 가장 정확한건 IEEE 문서를 참고 부탁드립니다. 130 page 에 case 문이 있네요 https://inst.eecs.berkeley.edu/~cs150/fa06/Labs/verilog-ieee.pdf 별도 공부 부탁드립니다.)

예를들면 casez 문의 "?" type 으로 interconnector (조건에 따른 data 분배 ) 설계할때 사용한 기억이 있어요.

즐공하세요 :)

감사합니다. 큰 도움이 되었습니다. 첨부해 주신 자료도 추가적으로 확인해 보겠습니다!