인프런 커뮤니티 질문&답변

Design Runs에서 BRAM 타일에 대한 질문 드립니다.

해결된 질문

작성

·

609

답변 1

0

설계독학맛비

지식공유자

안녕하세요 :)

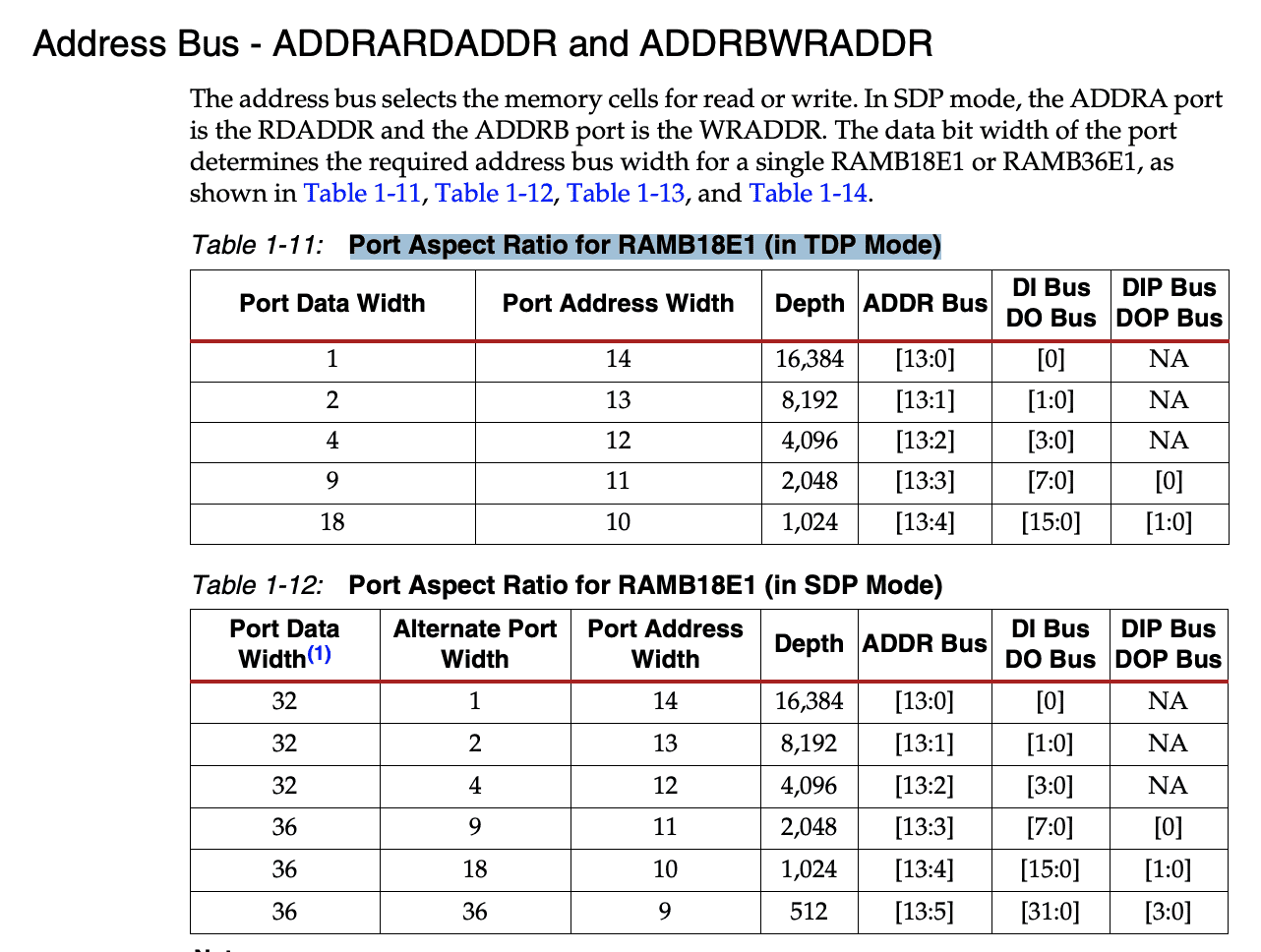

당연히 문서를 보시는게 가장 정확합니다. (모든 정답은 문서에 있어요.)

https://www.xilinx.com/support/documentation/user_guides/ug473_7Series_Memory_Resources.pdf

답변 드리겠습니다.

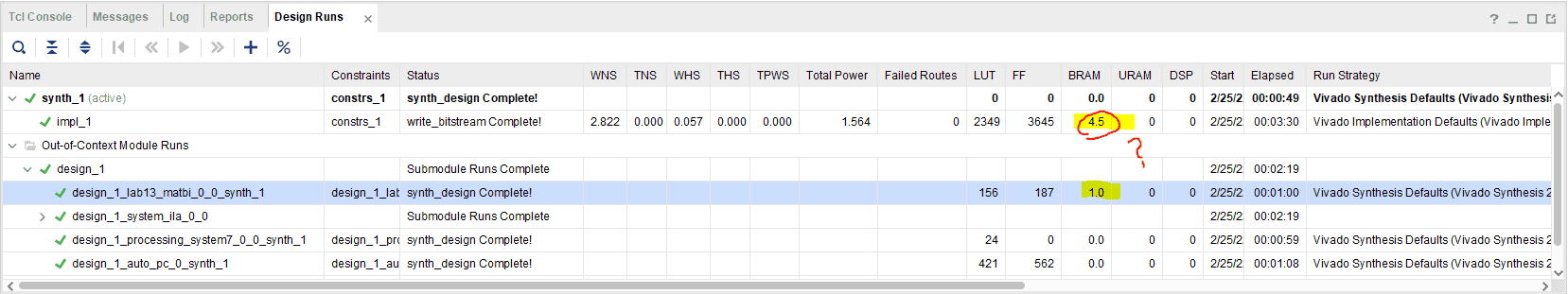

.5 부분은 System (Zynq) 관련 부분이구요. (3.5 tile 을 사용중이죠?) 내부구성은 저도 잘 모르겠습니다.

True DP BRAM 기준에서는 영상에서 설명드린 내용이 맞다 이구요.

다음 부분을 보시면 True DP BRAM 도 .5 가 가능합니다. 다만 문서에 나와있는 것처럼 512 Depth 기준 Data Width 가 18 이하가 되야합니다. 현재 저희는 512 Depth 기준 Data Width 32를 사용중 이구요. 그래서 "1" 로 나오는 것이 맞습니다.

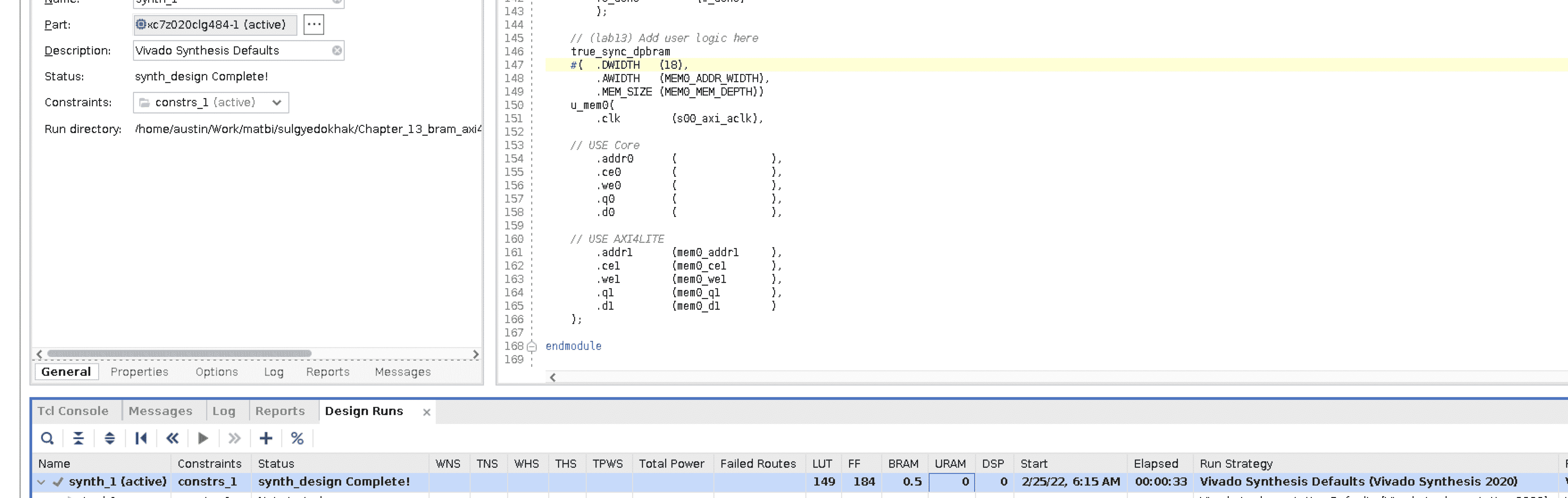

.5 를 보여드리려고 강제로 Data width 에 18 을 할당하였습니다. (동작은 32bit 기준으로 설계가 되어서 안되겠죠? 참고용으로만 봐주세요.)

즐공하세요 :)