인프런 커뮤니티 질문&답변

read data의 1cycle delay에 대해 질문드립니다.

작성

·

1K

1

- 학습 관련 질문을 남겨주세요. 상세히 작성하면 더 좋아요!

- 먼저 유사한 질문이 있었는지 검색해보세요.

- 서로 예의를 지키며 존중하는 문화를 만들어가요.

- 잠깐! 인프런 서비스 운영 관련 문의는 1:1 문의하기를 이용해주세요.

- 먼저 유사한 질문이 있었는지 검색해보세요.

- 서로 예의를 지키며 존중하는 문화를 만들어가요.

- 잠깐! 인프런 서비스 운영 관련 문의는 1:1 문의하기를 이용해주세요.

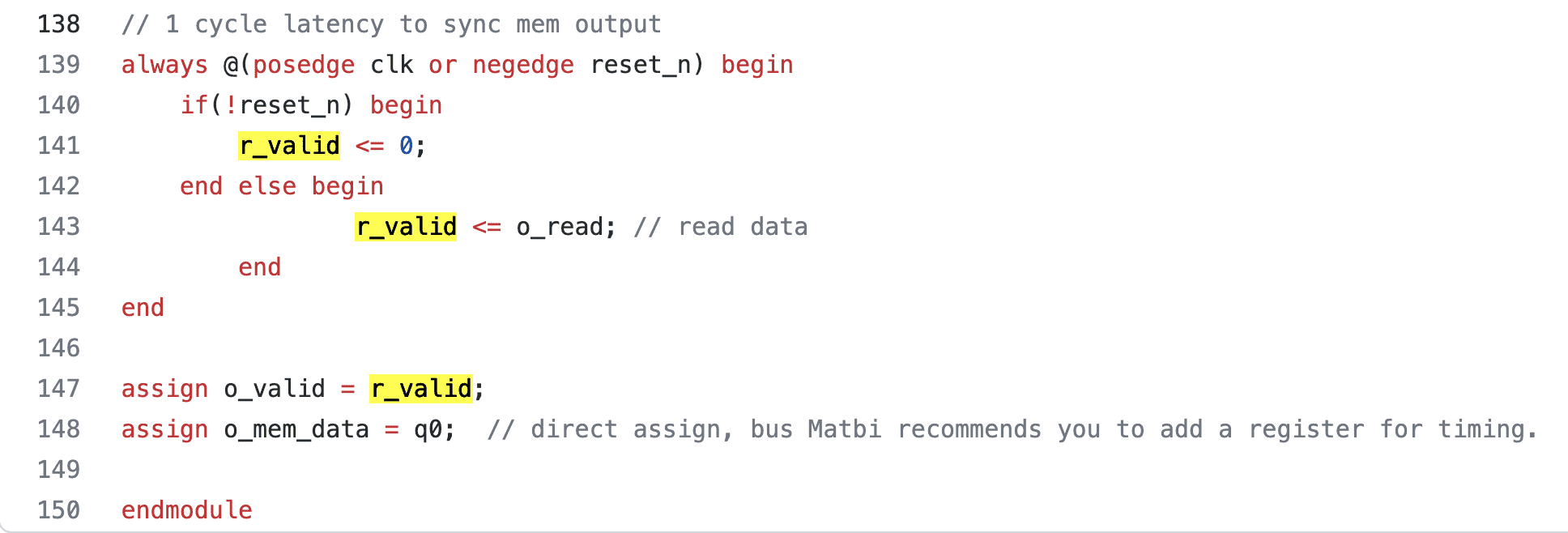

강의 때, 아래 코드가 1cycle delay를 위한 코드라고 말씀하셨는데요.

(B RAM의 Read data가 올라오는 타이밍이 1cycle 뒤이므로 해당 타이밍을 위해 1cycle delay가 필요하다는 점은 이해했습니다.)

왜 아래 코드가 1cycle delay가 되는지 이해를 못했습니다. ㅠㅠ

죄송하지만 설명부탁드립니다.

// 1 cycle latency to sync mem output

always @(posedge clk or negedge reset_n) begin

if(!reset_n) begin

r_valid <= 0;

end else begin

r_valid <= o_read; // read data

end

end

assign o_valid = r_valid;

assign o_mem_data = q0; // direct assign, bus Matbi recommends you to add a register for timing.

답변 3

1

0

안녕하세요 맛비님 simple_bram_ctrl.v 모듈에 질문이 있습니다! memory I/F input/output port 정의하는 부분에서 q0를 input으로 두셨는데 마지막 줄에 보니까 output port o_mem_data 에 input port q0를 할당하셨더라고요. 이렇게 해도 코드상 문제가 없을까요?

0

설계독학맛비

지식공유자

안녕하세요 :)

r_valid 는 F/F 이구요. o_read 신호를 1 cycle delay 시키게 됩니다. (waveform 을 띄워서, o_read 와 r_valid 시그널을 보시면 좋을 것 같아요. 바로 이해 되실 겁니다.)

147, 148 line 을 보시면, memory 에서 나오는 출력 신호 q0 는 이미 1cycle delay 가 되어 있고, read data 가 유효한 Timing 의 Sync 를 맞춰주기 위해서, o_read 신호를 1 cycle delay 시켰어요.

즐공하세요 :)