인프런 커뮤니티 질문&답변

latching 부분과 코드에 대해 질문드립니다.

작성

·

232

1

- 학습 관련 질문을 남겨주세요. 상세히 작성하면 더 좋아요!

- 먼저 유사한 질문이 있었는지 검색해보세요.

- 서로 예의를 지키며 존중하는 문화를 만들어가요.

- 잠깐! 인프런 서비스 운영 관련 문의는 1:1 문의하기를 이용해주세요.

- 먼저 유사한 질문이 있었는지 검색해보세요.

- 서로 예의를 지키며 존중하는 문화를 만들어가요.

- 잠깐! 인프런 서비스 운영 관련 문의는 1:1 문의하기를 이용해주세요.

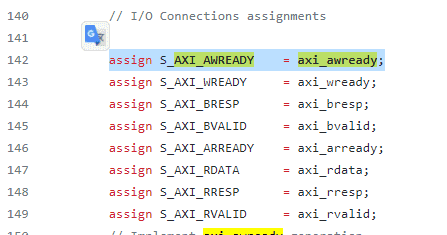

1. 리뷰해주신 코드에서 아래와 같은 구문이 있는데요.

강의 도중 85번 줄에서 부터 94번 줄이 latching을 위한 것이라고

말씀하셨는데요. 배움이 부족하여 왜 latching을 위한 것인지

이해를 못했습니다(뭘 봐야 하는지라도... 부탁드립니다.)

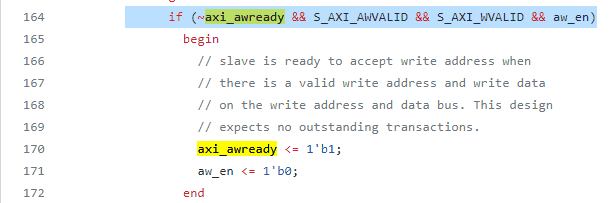

2. 177번 줄을 보면 write address 정보를 넘기는 것으로 보이는데요

- 왜 조건문에 ~axi_awready인지 => awready awvalid가 둘다 1이여야 데이터가 넘어 가지 않나요? 왜 ~axi_awready 즉 0일 때, 데이터가 넘어가나요?

- S_AXI_WVALID는 Write data를 넘길때 확인해야 할 것 같은데 왜 여기서 확인하나요?

항상 훌륭한 강의 및 답변 감사드립니다.

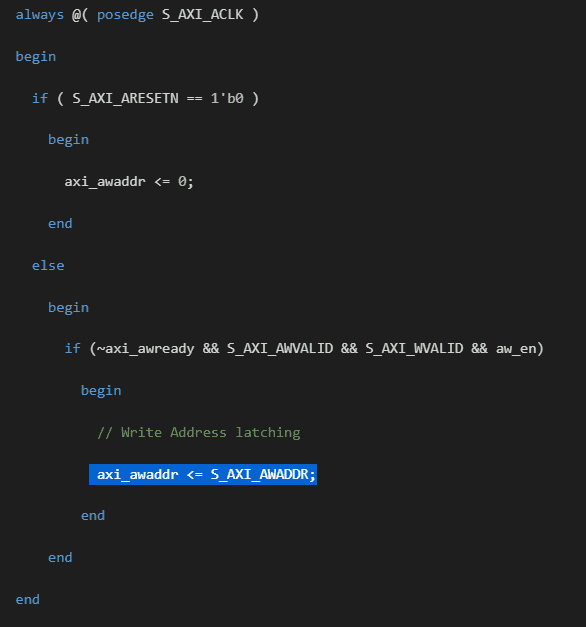

// Implement axi_awaddr latching

// This process is used to latch the address when both

// S_AXI_AWVALID and S_AXI_WVALID are valid.

always @( posedge S_AXI_ACLK )

begin

if ( S_AXI_ARESETN == 1'b0 )

begin

axi_awaddr <= 0;

end

else

begin

if (~axi_awready && S_AXI_AWVALID && S_AXI_WVALID && aw_en)

begin

// Write Address latching

axi_awaddr <= S_AXI_AWADDR;

end

end

end

답변 2

1

0

설계독학맛비

지식공유자

안녕하세요 :)

답변하기 어려운 질문이네요 ㅎ 난이도가 있습니다. (제 설명이 부족해도 이해 부탁드립니다.)

답변하기 어려운 질문이네요 ㅎ 난이도가 있습니다. (제 설명이 부족해도 이해 부탁드립니다.)

"HW 의 지식" 을 쌓으시면 자연스럽게 해결되실 겁니다.

어려우니까 보람있는 직업이니까 꼭 즐공하시기를 부탁드립니다.

완독하시면 jump up 에 도움이 되시리라 생각해요 :)

추천 도서는

1. https://book.naver.com/bookdb/book_detail.nhn?bid=1912296

2. Advanced chip design Practical Example (구글에 검색하시면 pdf 가 아마? 나오실 겁니다.)

2번 도서는 어렵지만, 완독하시면 정말 도움이 되실겁니다. (저는 오래되어서.. 가물가물하지만 좋은 도서입니다.)

이해의 도움이 되기위해서 글을 길게 적었습니다. 읽기전에 미리 양해부탁드립니다.

1. 리뷰해주신 코드에서 아래와 같은 구문이 있는데요.

강의 도중 85번 줄에서 부터 94번 줄이 latching을 위한 것이라고

말씀하셨는데요. 배움이 부족하여 왜 latching을 위한 것인지

이해를 못했습니다(뭘 봐야 하는지라도... 부탁드립니다.)

data 가 동작중에 변하면 안되는 것들이 있습니다. 현재 코드에서는 addr 가 되겠네요.

hand shake 를 앞두기전, address data 를 유지하고 싶은겁니다.

즉, 입력으로 들어오는 addr 대신, 내가 F/F 로 저장해서 F/F 에 저장한 addr 을 사용하는 겁니다.

왜냐하면, System 에서 Black box IP 와 수 많이 연결 될텐데, 간혹 이상한 IP의 AXI I/F 는 addr 를 바꿀 수 있습니다. 또하나의 이유는, F/F 으로 저장해놓은 신호를 사용하면, Timing 에 유리합니다. Timing 에 유리한 이유는 Verilog HDL 강의의 Pipeline 편을 참고해주세요.

정리하면,

정상동작을 위해서, 나만의 Timing 에서 사용하기 위해서 input 을 F/F 에 저장합니다.

이것을 input 신호를 latching 한다. 라고 실무에서 표현합니다. 물론 input 외에 내부 신호도 나만의 timing 을 위해서 latching 가능합니다.

2. 177번 줄을 보면 write address 정보를 넘기는 것으로 보이는데요

- 왜 조건문에 ~axi_awready인지 => awready awvalid가 둘다 1이여야 데이터가 넘어 가지 않나요? 왜 ~axi_awready 즉 0일 때, 데이터가 넘어가나요?

- S_AXI_WVALID는 Write data를 넘길때 확인해야 할 것 같은데 왜 여기서 확인하나요?

앞선 latching 과 유사한 형태인데요.

Timing 을 좋게 하기 위해서, F/F 으로 axi_awready 신호를 출력합니다.

즉, registered output 입니다. axi_awready 는 F/F, AWREADY 는 output 시그널입니다. (코드 보셔요)

앞서 모르는 IP 와 붙을 수 있다라고 했구요. 회사마다 정책은 다 다르지만,

보통 output 은 registered output 을 합니다. 이유는 IP를 붙였을 때, Timing 을 확률적으로 좋게하기 위함입니다. (어떤 IP랑 붙을지 모르니까)

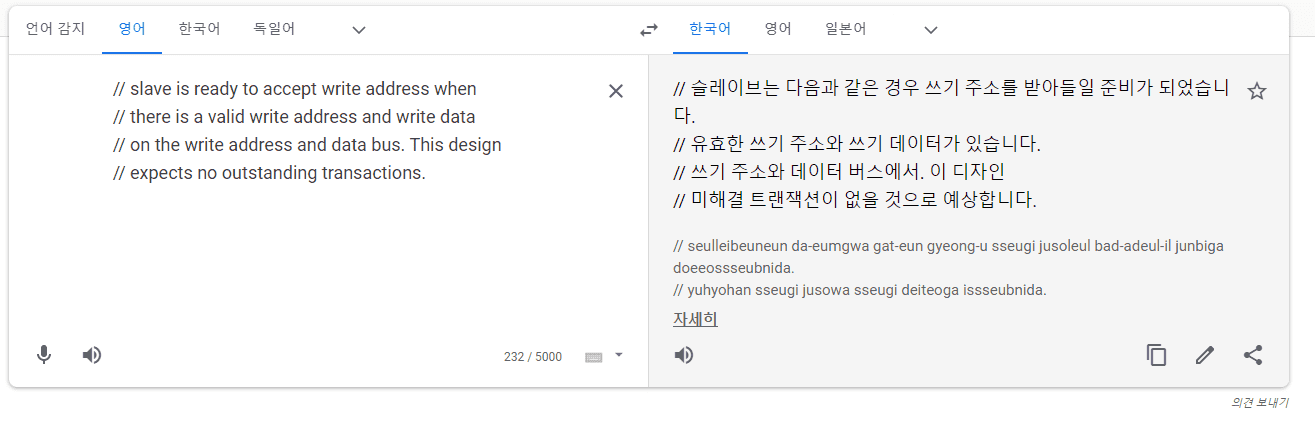

영어 주석으로 적혀있지만, 재 해석해 드리면

입력으로 AWVALID 와 WVALID 와 aw_en 신호가 1 이면, 나는 axi_awready 를 1로 하겠다.

이말은, Transaction 을 위한 유효한 Data 가 전부 준비가 되면, 내가 axi_awready 를 띄우겠다 입니다.

즉, AXI 의 Write 동작 주체는 "해당 모듈"이 되겠습니다.

주체가 이 모듈이고, 따라서 올려주신 코드는 앞서 설명드린 latching 에 해당됩니다.

열린 사고를 위해서, 이 코드가 정답은 아닙니다. 다르게 설계하셔도 됩니다. 전체 System 을 파악하고 있다면 latching 을 빼도 됩니다. 다만 잘짠 코드를 따라하는 과정은 중요합니다 :)

이해가 되셨는지 모르겠네요. 어렵습니다. 모르셔도 좌절하지 마세요. 공부하면 됩니다.

추천도서 완독 + AXI I/F 문서를 보시고 설계를 해보시면 자연스럽게 해결이 되실겁니다.

시간과 노력이 약이다.

즐공하세요 :)