인프런 커뮤니티 질문&답변

Pipeline 실습 관련 질문드립니다

해결된 질문

작성

·

486

5

안녕하세요 양질의 강의 영상 감사합니다!

Pipeline 실습에서는 Valid 신호를 3개의 Flip Flop을 죽 늘어선 형태로 사용하셨는데 이게 혹시 실제로도 이렇게 코딩하여 합성하면 Hold Time 위반이 발생하는게 맞나요? Flip Flop 사이에 아무런 조합회로가 안붙고 플립플롭의 출력이 입력으로 바로 들어가면 Hold Time 위반이라고 학교에서 얼핏 배운 기억이 났습니다

만약 Hold Time 위반이 맞다면 실제 합성시에는 사이에 Buffer를 사용하여 해결하면 될까요?

또한 실무에서 그렇게 Buffer를 추가하는 것은 RTL 엔지니어가 Hold Time 위반 나겠다 싶은 곳에다가 Verilog 코드에 추가해주는 식으로 해결하는지 아니면 합성 이후 Back End쪽(??)단계에서 버퍼를 추가시켜서 해결하는지 궁금합니다

답변 1

1

안녕하세요 :)

좋은 질문 감사합니다. 결론은 가장 밑에 두었습니다.

Setup Time Violation 은 Clock 의 Operating Freq 을 낮추면 동작할 수 있지만, hold time violation 은 Freq 를 낮춘다고 해결할 수 없는 Critical 한 (무서운..) Violation 입니다.

Flipflop 사이에 Combinational Logic 이 없다면, 알고계신대로 Hold time violation 이 발생할 수 있습니다.... 만! Tool 에서 해결이 가능합니다. 즉, 연속적인 F/F 을 기술하는 코드는 사용 가능합니다. (FPGA 강의에서 연속적인 F/F 을 기술한 코드를 사용했었고, 동작함을 확인했습니다.)

ASIC 에서는 Backend 에서 Holdtime Violation 을 처리 합니다. (buffer 를 삽입한다던지, 위치를 변경하여 Delay 를 변경한다던지.. 등등 아주 다양한 방법들이 존재합니다.)

마찬가지로 FPGA 에서도 Hold time fix 가 가능합니다.

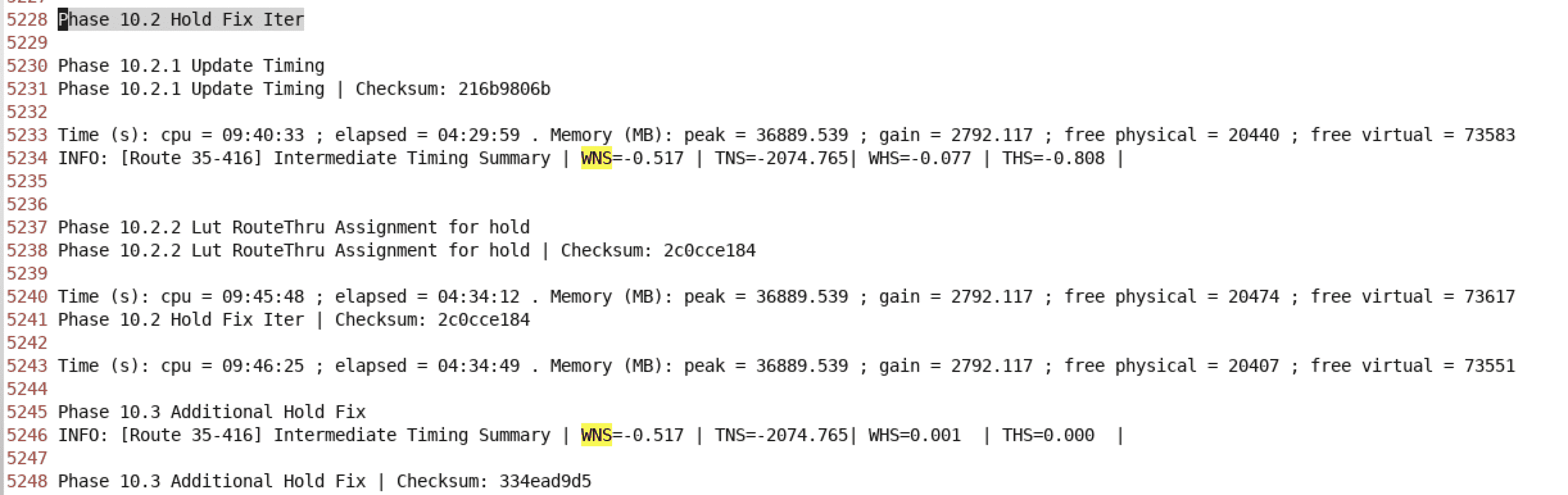

Xilinx Tool 에서 Implementation 단계에 hold time violation 을 해결하는 단계가 있습니다. 다음은 예시입니다. Hold Fix Iter 를 수행하면서, hold time violation 이 fix 됩니다.

결론은 Tool 혹은 Backend 엔지니어를 믿고, 연속적인 F/F 을 Verilog HDL 을 통해 기술하셔도 됩니다. (코드에 직접 버퍼를 추가한다던가 하지 않아요. 그대로 사용합니다.)

즐공하세요 :)