인프런 커뮤니티 질문&답변

test bench 코드 질문 있습니다.

작성

·

264

1

- 학습 관련 질문을 남겨주세요. 상세히 작성하면 더 좋아요!

- 먼저 유사한 질문이 있었는지 검색해보세요.

- 서로 예의를 지키며 존중하는 문화를 만들어가요.

- 잠깐! 인프런 서비스 운영 관련 문의는 1:1 문의하기를 이용해주세요.

- 먼저 유사한 질문이 있었는지 검색해보세요.

- 서로 예의를 지키며 존중하는 문화를 만들어가요.

- 잠깐! 인프런 서비스 운영 관련 문의는 1:1 문의하기를 이용해주세요.

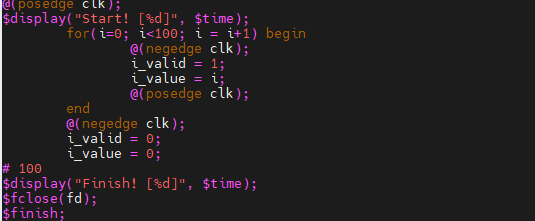

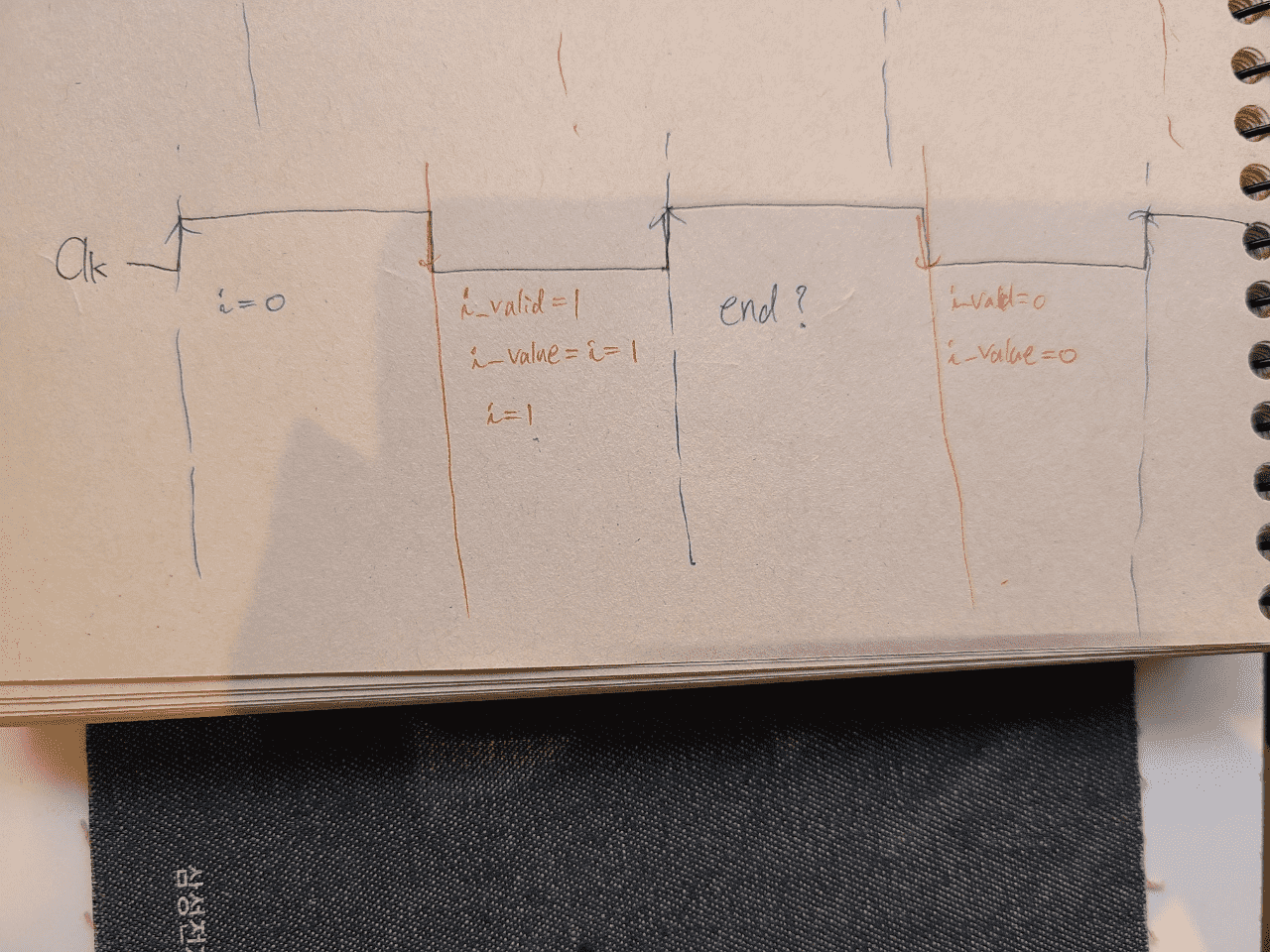

이 부분을 clk 시그널에 맞춰서 생각해봤는데 .. 혹시 clk 시그널에 맞춰서 i랑 i_valid, i_value의 흐름을 그려주실수 있나요?..

답변 2

0

Taiwan

질문자

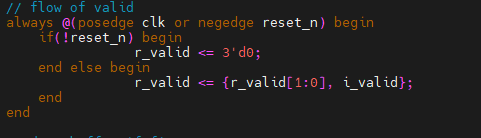

혹시 이 부분은

첫번째 posedge clk에서

r_valid = r_valid[1] r_valid[0] i_valid

두번째 posedge clk에서

r_valid = r_valid[0] i_valid(1클럭 pos신호) i_valid(2클럭 pos신호)

세번째

r_valid = i_valid(1클럭 pos신호) i_valid(2클럭 pos신호) i_valid(3클럭 pos 신호) 인건가요?

질문1. shift 된다는 의미가 무엇인지 모르겠습니다. shift되며 flip flop에 저장된 값들이 어느 시점에 온것인지 판단을 위해 valid 신호를 넣는건가요?

질문2. o_valid는 처음 r_valid의 MSB로 부터 온 것이고 1사이클, 2사이클 까지 값이 나오지 않다가 3사이클 부터 1사이클에 넣어준 i_valid값이 나오게 되는 것인가요?!

질문이 이해가실지 모르겠습니다 허접한 머리라 이해가 부족합니다 ㅠㅠ

0

설계독학맛비

지식공유자

안녕하세요 :)

waveform 이 있기 때문에, 직접 확인해보시면 되지 않을까 싶어요.

손으로 그리신거와 비교해서 보세요.

그 다음 어떤 부분이 이해가 안되시는지 세부적으로 적어주시면 답변에 도움이 될 것 같아요.

즐공하세요 :)

허접한 머리가 어딨나요. 자책하지 마세요 ㅠ

제 생각에 기존에 달아주신 질문들을 봤을때, verilog hdl 공부에 있어서 순서를 건너 뛰신 것 같아요. 제 강의의 필독 문서와 소개에도 적혀있지만, 현재 강의는 verilog hdl 을 알고계시다는 전제에서 만든 강의입니다. 전자과 3학년 이상의 지식이 필요하다고 생각해요. 그만큼 난이도가 쉽다고 생각하지 않아요. 그렇다고 소화할 수 없다 는 아닙니다. 지금처럼 질의응답 과정을 통해서 해결하실 수 있다 생각해요!

긴 글 결론은 순서를 지키시면, 실력향상에 도움이 되실겁니다 :)

거의 유사한? 질문을 받은 경험이 있어서 링크 공유드려요!

https://inf.run/FWkA

두번째? 댓글 부터 있구요. 확인부탁드릴께요.

모르는게 죄는 아니잖아요 ㅠㅠ

직접 설계해보시고, 돌려보시고 결과를 확인해보셔서 경험을 쌓으시길 바랄께요.

즐공하세요 :)