인프런 커뮤니티 질문&답변

Counter 설계관련 질문

해결된 질문

작성

·

299

1

맛비님 counter 설계를 보고 제가 나름대로 찾아서 설계를 생각해봤습니다.

생각하다보니 질문이 있습니다.

1. D flip flop을 설계할 때 맛비님의 경우에는 output port를 wire 상태로 그냥 두시고 reg 변수를 따로 선언하셨습니다.

찾다보니

output port를 output reg 타입으로 선언해서 d flip flop을 설계하는 경우도 있던데 두 차이 점이 무엇인지 궁금합니다

나중에 합성할때 맛비님 방식이 더 유리한 것인가요?

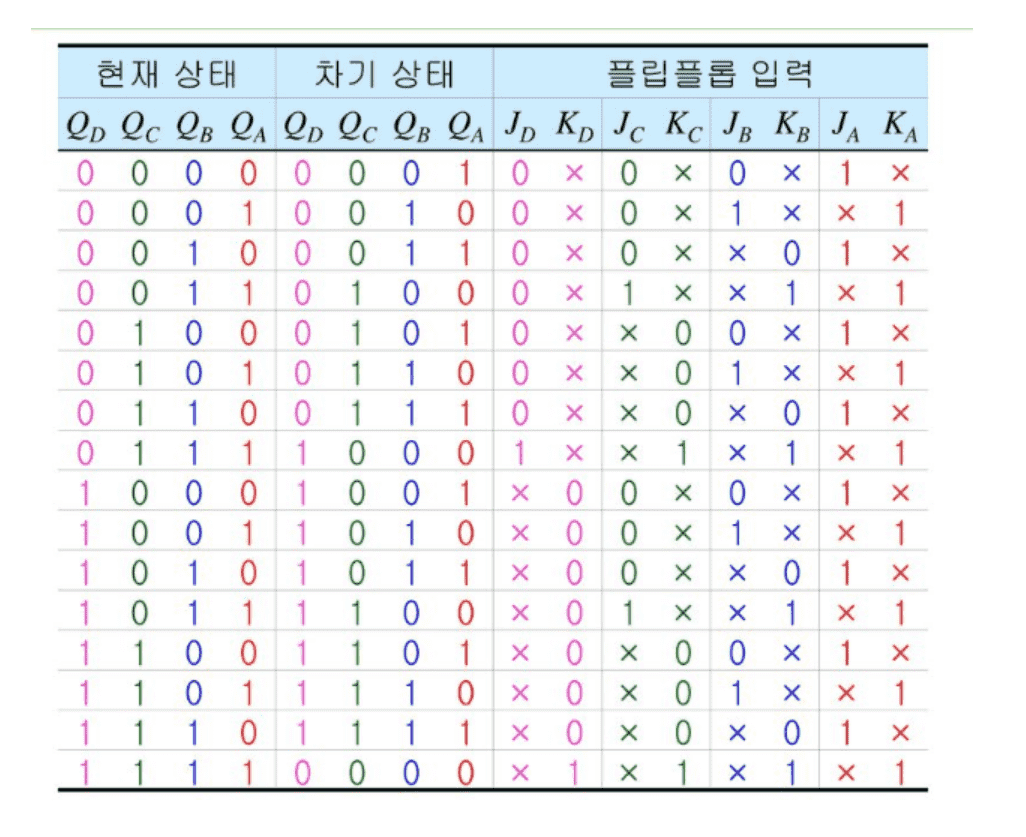

2. 맛비님은 counter 설계시 한번에 하셨는데 동기식/비동기식 counter를 찾아보면 여러개의 D flip flop으로 설계한 것들을 찾아볼 수 있었습니다. 여기서 질문이 있습니다. 아래 첨부한 사진을 보시면 4bit 동기식 counter를 설계했을 뿐인데도

truth table의 양이 많은 것을 알 수 있습니다. 만약 제가 16bit 동기식 counter를 설계한다고 하면 훨씬 더 많은 truth table이 요구되고 이 truth table을 가지고 카르노맵을 그리는 것이 훨씬 더 복잡해 질텐데 실무에서는 그럼 어떻게 설계를 하는건가요??? 혹시 이런 복잡함을 줄이려고 맛비님이 counter 설계 설명시 내부에 reg를 선언해서 +1씩 해주신건가요??(훨씬 단순하게 설계를 하기 위해 강의하신 내용대로 하는 것인지 궁금합니다)

답변 1

1

안녕하세요 :)

1. D flip flop을 설계할 때 맛비님의 경우에는 output port를 wire 상태로 그냥 두시고 reg 변수를 따로 선언하셨습니다.

찾다보니

output port를 output reg 타입으로 선언해서 d flip flop을 설계하는 경우도 있던데 두 차이 점이 무엇인지 궁금합니다

Verilog HDL 문법에서 port 는 기본 wire 입니다. reg 를 output port 에 적어도 돼요!

저는 port 는 wire, reg 는 reg 이런 식으로 나눠서 설계를 합니다. 케바케 겠지만 저의 가독성을 높이는데 도움이 돼요 :)

혹, 별로시라면 output reg 를 사용하세요. 해도 됩니다!!

나중에 합성할때 맛비님 방식이 더 유리한 것인가요?

Out Port 에 reg 를 사용하나, 별도로 reg 를 사용하나, 합성 결과는 동일합니다. (회로적으로 동일하기 때문에, 어느 문법이 불이익을 받아야 할 이유가 없다 생각합니다.)

2. 맛비님은 counter 설계시 한번에 하셨는데 동기식/비동기식 counter를 찾아보면 여러개의 D flip flop으로 설계한 것들을 찾아볼 수 있었습니다. 여기서 질문이 있습니다. 아래 첨부한 사진을 보시면 4bit 동기식 counter를 설계했을 뿐인데도 truth table의 양이 많은 것을 알 수 있습니다. 만약 제가 16bit 동기식 counter를 설계한다고 하면 훨씬 더 많은 truth table이 요구되고 이 truth table을 가지고 카르노맵을 그리는 것이 훨씬 더 복잡해 질텐데 실무에서는 그럼 어떻게 설계를 하는건가요??? 혹시 이런 복잡함을 줄이려고 맛비님이 counter 설계 설명시 내부에 reg를 선언해서 +1씩 해주신건가요??(훨씬 단순하게 설계를 하기 위해 강의하신 내용대로 하는 것인지 궁금합니다)

Behavior 모델로 설계를 하였다 라고 먼저 답변드립니다. 모든 로직을 카르노 맵으로 그리면서 설계하면, 제품이 나오려면... 얼마나 오래 걸릴까요? 현업 와서 카르노맵 그려본적이 없습니다. 그렇다면 카르노맵이라는 로직을 줄일 수 있는 알고리즘이 중요하지 않은거냐?! 그건 아닙니다. 이미 사용하고 계시는 합성 Tool 에서 이런 진리표 기반의 Optimize 를 하고 있습니다. 카르노맵은 합성 Tool 의 영역입니다.

PS 진리표 나와서 깜짝놀랐습니다! 이 말은 현업가시면 자연스럽게 이해가 되실거라 생각해요.

(시간과 사람은 한정적입니다. 설계할 로직은 세상에 많구요.)

답변 감사합니다!