인프런 커뮤니티 질문&답변

답변 1

1

안녕하세요 :)

와.. 이걸 물어볼줄은 생각조차 못했네요.

(솔직히 맛비도 모르고 있었다는 뜻이죠? 하핫;; 이러면서 하나 배웁니다.)

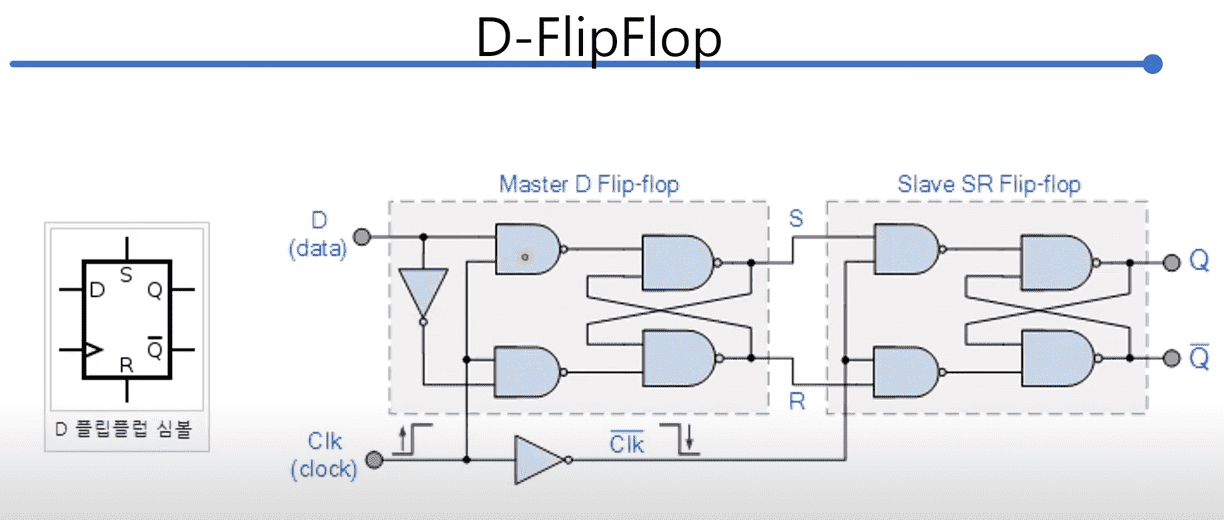

다음 그림을 말씀하시는 것 같아요.

먼저 왼쪽의 Symbol 은 말그대로 symbol 이구요. 실제 회로는 오른쪽과 같이 구성됩니다. (완벽하게 동일한지는, 소자쪽의 Low Level 하시는 분이 더 잘아시겠지만요)

다음링크에 상세하게 설명이 되어 있어요. (작동을 알고 싶으시면 꼭 읽어보세요!! 직접 0,1 을 넣어보시면 답이 되십니다.)

https://www.electronics-tutorials.ws/sequential/seq_4.html

읽어봤는데, 개인적으로 작동보다는 Master, Slave 로 D F/F 을 구성한 것이 핵심이라고 생각하는데요.

그 부분에 대해서 적어볼께요.

<D-Type Flip-flop circuit>

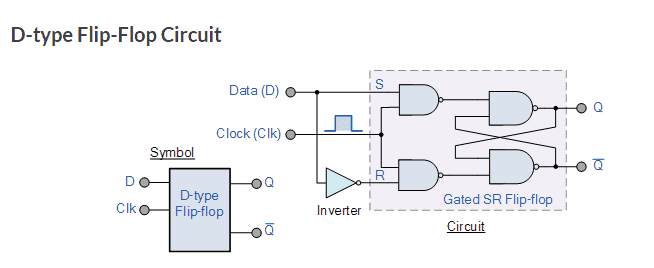

먼저 다음 그림처럼

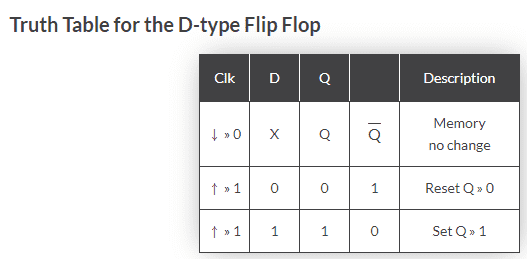

Function 적으로 봤을때, 이거 자체만으로 D F/F 이 될 수 있습니다. 다음 진리표를 갖죠.

여기서는 5개의 Gate 가 쓰이죠. ( not gate 1ea, nand gate 4ea)

여기서 clock 은 edge 일때만, D F/F 으로 동작하죠. pulse 신호 (0,1,0) 가 아니더라도 동작한다는 의미입니다. 단순히 0 -> 1 로만 가도 edge 로 인식해서 동작해요. (혹은 1 -> 0 )

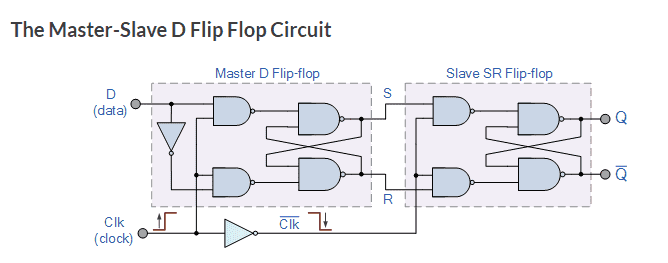

<The Master-Slave D Flip Flop Circuit>

그런데 왜, 굳이!! 위에 5개의 gate 를 갖는 D F/F 을 사용하지 않고, 다음 그림처럼 10 gate 의 F/F 을 사용할까요?? 이것도 진리표를 그려보시면 D F/F 입니다.

위의 <D-Type Flip-flop circuit> 과의 차이는.

Clock 신호의 완전한 Pulse (0->1->0) 가 인가 되었을때, D F/F 으로 동작합니다.

단순한 Edge Detector 가 아닙니다. Pulse Detector 입니다.

구글 번역기로 적습니다.

위에서 보면 클럭 펄스의 리딩 에지에서 마스터 플립플롭이 데이터 D 입력에서 데이터를 로드하므로 마스터가 "켜짐"임을 알 수 있습니다. 클록 펄스의 후행 에지에서 슬레이브 플립플롭은 데이터를 로드합니다. 즉 슬레이브는 "ON"입니다. 그러면 항상 하나의 플립플롭이 "ON"되고 다른 하나는 "OFF"되지만 마스터와 슬레이브가 동시에 "ON"되지는 않습니다. 따라서 출력 Q는 하나의 완전한 펄스, 즉 0-1-0이 클럭 입력에 인가될 때만 D의 값을 얻습니다.

제가 ASIC IP 를 설계하는 회사에 있을때, Library 마다 다르겠지만, ASIC Library 의 D F/F 은 <The Master-Slave D Flip Flop Circuit> 을 사용한다고 알고 있었구요. 1bit F/F 의 size는 10 Gate 로 계산하면 Area 가 유사하게 맞았어요.

결론

10:35초의 회로는 <The Master-Slave D Flip Flop Circuit> 이고, 이는 Clock Pulse Detector 를 갖춘 D F/F 입니다. ASIC 의 D F/F Library 에서 보통 (다른걸 사용할 수 있으니까) <The Master-Slave D Flip Flop Circuit> 를 사용하며, gate 는 10 개를 사용합니다.

작동은 Link 를 꼭 봐주세요. 읽으면 이해가 됩니다.

저도 배웠네요. 즐공하세요 :)