인프런 커뮤니티 질문&답변

Reset 관련 질문입니다.

해결된 질문

작성

·

310

1

안녕하세요! 맛비님!

강의 열심히 따라가며 수강하고 있습니다.

강의를 듣다가 보면 항상 Reset에서 막혀 다시 Reset 강의로 돌아가서 확인하고 있습니다..ㅎㅎ

어느정도 이해가 되었다고 생각했는데 궁금해서 질문 드립니다.

reset을 이용해서 처음부터 시작하는 신호와 unknown 상태를 방지하기 위해서 사용하는 것으로 알고 있습니다.(맞나요?)

하지만 코드를 따라가다 보면 reset 값만 0에서 1로 바꾸고 나머지 값에는 영향을 주지 않는거 같은데 reset을 통해서 나머지 변수들에게도 영향을 주는 건가요?

아니면 reset의 출발신호만을 알기위해서 사용하는 건가요??

답변 2

1

답변 감사드립니다.

여기에 이어 붙여서 쓰는게 맞나 싶네요..

다른 공부하시는 분들이 여쭤본 질문 중 Q3 r_valid 관련 질문이 있었습니다.

r_valid 값을 제가 시뮬레이션에 추가해서 따라가보면서 확인했습니다.

그 결과 000 001 011 111 로 변경되는 것을 확인했습니다.

0(2)0(1)0(0) 비트수 별로 번호를 매겼을 때 이렇게 표현되고 {r_valid[1:0], i_valid}는 0(1)0(0) 이 두비트에 i_valid가 추가된다고 생각하면 되나요??

좋은 자료 감사드립니다.

궁금증이 해결되지 못해 죄송합니다.

{r_vaild[1:0], i_vaild} 구문은 concatenation 연산이라고 생각되는데

예를 들어 {4'b1010, 2'b01}라고 하면 결과가 6'b101001이 되는게 아닌가요??

r_varid = 3'd0 = 3'b000 , i_valid = 1

이게 맞다면 {r_vaild[1:0], i_vaild} 는 r_valid 는 2비트, i_valid 는 1비트(? 잘모르겠습니다.)

001 이라고 봐도 될까요?

{r_vaild[1:0], i_vaild} 구문은 concatenation 연산이라고 생각되는데

예를 들어 {4'b1010, 2'b01}라고 하면 결과가 6'b101001이 되는게 아닌가요??

맞아요! concatenation 의 뭉친 bit 를 어떻게 assign 하고 있나요?!!!

그림을 그려보시면 더욱 좋아요. HW 입니다. 공부하시는 과정이시기에 꼭 이해하시기를 바랄께요.

===========================================

shift register 이구요.

보통 shift reg 를 이렇게 구현하겠네요.

reg [2:0] r_vaild;

always @( posedge clk) begin

r_valid [0] <= in;

r_valid [1] <= r_valid [0];

r_valid [2] <= r_valid [1];

end

이거를... 이렇게 바꿔볼께요. 어떤가요?

reg [2:0] r_vaild;

always @( posedge clk) begin

r_valid <= {r_valid[1:0], in};

end

지금은 r_valid 가 3 bits 인데, 이게 10................000 bits 라면?

이해 안되시는거 있으면 남겨주세요!! 되실때까지!! 끝까지 갑니다 ㅎ

1

안녕하세요 :)

reset을 이용해서 처음부터 시작하는 신호와 unknown 상태를 방지하기 위해서 사용하는 것으로 알고 있습니다.(맞나요?)

네 맞습니다!

하지만 코드를 따라가다 보면 reset 값만 0에서 1로 바꾸고 나머지 값에는 영향을 주지 않는거 같은데 reset을 통해서 나머지 변수들에게도 영향을 주는 건가요?

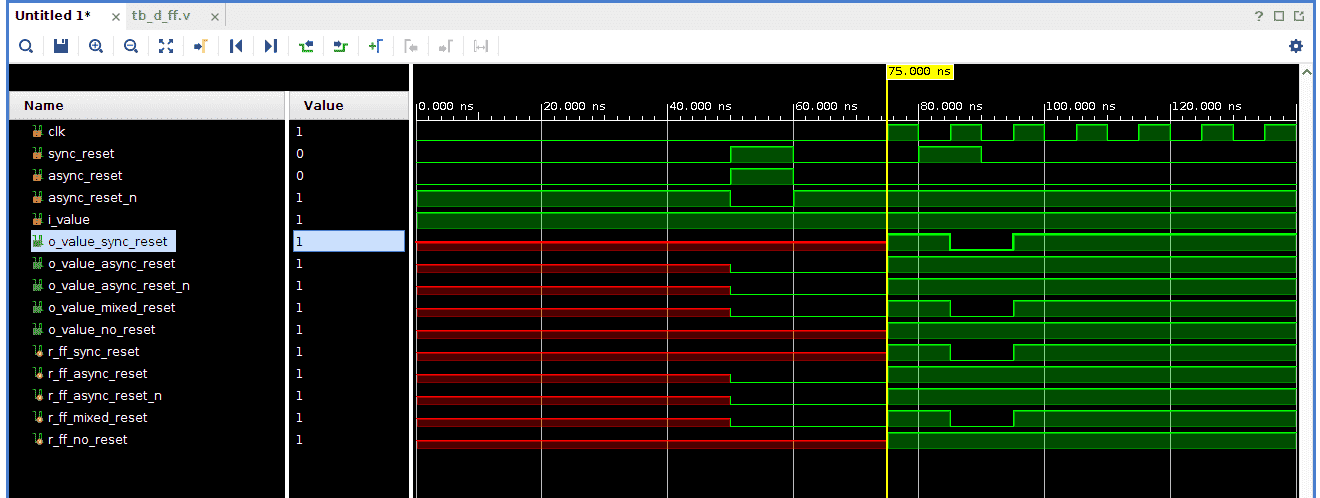

D F/F 의 출력 값에 집중해서 확인하시면 좋을 것 같아요. 다음 waveform 에서는 o_value_어쩌고 에 집중해 주세요.

reset 이 없다면 계속 unknown 상태니, 0 과 1 의 Digital System 의 동작이 원하는대로 흘러가지 않게됩니다. 물론 Designer 가 의도적으로 unknown 이어도 System 에 문제가 없음을 보장하기도 해요. (초기 값이 필요 없는경우) 하지만, unknown 을 보장할 자신이 없다면 reset 은 무조건! 넣어주세요.

아니면 reset의 출발신호만을 알기위해서 사용하는 건가요??

출발신호..? (의 의미가 이해가 잘 안되지만.)

앞서 설명드린 System 이 시작하기전에 unknown 을 0과 1의 Digital System 으로 만들어 주는 역할을 한다 생각하시면 될 것 같아요. 출발신호가, System 시작전에 하는거라.. 그런 의미라면.. 맞습니다. 가지고 계신 모든 Digital 기계에는 Reset 이 있어요. :)

그럼 즐공하세요~!

Shift Register 를 확인하시면 될 것 같아요.

다 읽어보진 마시고, 아! 라고 생각나시면 그만 보셔도 됩니다.

https://ko.wikipedia.org/wiki/%EC%8B%9C%ED%94%84%ED%8A%B8_%EB%A0%88%EC%A7%80%EC%8A%A4%ED%84%B0

Verilog HDL 설계 tip 같은 겁니다. 저는 자주 써요.