인프런 커뮤니티 질문&답변

testbench DUT 관련 질문드립니다!

해결된 질문

작성

·

531

1

안녕하세요 testbench 코드를 보던중 궁금한점이 생겨 질문합니다!

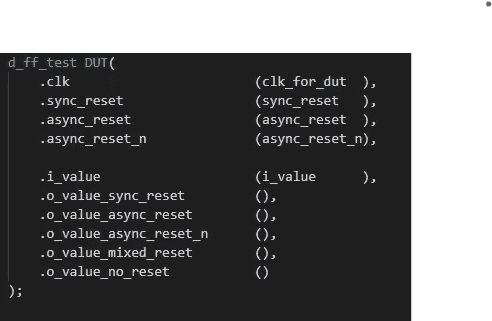

위 코드에서 DUT를 적을 때 오른쪽 괄호 안의 내용은 어떤걸 의미하나요 ? 시뮬레이션을 할 때 나타나는 이름 정도로 생각하고 있었는데 맞을까요?

output 부분은 비워져있는 이유는 무엇인가요 ?

답변 2

1

안녕하세요 :)

의미는 다음과 같습니다.

.모듈내부의_포트 (연결 wire)

여기서, 비워둔 이유는 사용하지 않기 때문입니다.

사용하지 않지만 채우셔도 됩니다.

가장 중요한 결론은

사용하지 않는다 라는 Designer 의 보장이 있다면, 비우셔도 됩니다.

즐공하세요 :)

0

안녕하세요!

i_value 값은 reg로 선언되었기 때문에 wire로 연결시켜준게 맞나요??

나머지 output 값은 reg로 선언되지 않았고 연결시켜줄 필요가 없어어 비워둔게 맞을까요??

채워도 된다는게 reg로 선언을 먼저하고 채워야 하나요??

안녕하세요. :)

Verilog HDL 의 Syntax 공부가 필요해 보이구요.

필독문서에서 언급했던 것처럼 Syntax 는 제가 별도로 설명을 자세히 안드리는 점 양해 부탁드립니다.

이 질문을 이해할 수 있는 가장 좋은 링크를 찾았습니다. (영어지만.. 아주 훌륭합니다.)

https://www.chipverify.com/verilog/verilog-module-instantiations

아니면 한글 링크도 하나 찾았는데, 개인적으로는 책을 보시는 것을 추천 드립니다. (책은 밑에 추천해 놓았어요)

https://hizino.tistory.com/entry/verilog-%EB%AA%A8%EB%93%88%EA%B0%80%EC%A0%B8%EC%98%A4%EA%B8%B0

이 링크를 읽으셨다고 가정하고 답변드리겠습니다.

i_value 값은 reg로 선언되었기 때문에 wire로 연결시켜준게 맞나요??

-> 모듈의 input port 에 값을 넣어주기 위함이고, wire 에 그 값을 연결해 놓았습니다.

나머지 output 값은 reg로 선언되지 않았고 연결시켜줄 필요가 없어어 비워둔게 맞을까요??

-> reg 와는 무관합니다. 사용하지 않아서, 연결시켜줄 필요가 없어서 비워두었습니다.

채워도 된다는게 reg로 선언을 먼저하고 채워야 하나요??

-> reg 와는 무관합니다. instantiation 이 된 모듈을 연결하기 위한 wire 혹은 reg 가 되어야합니다.

코드가 어떻게 회로로 그려질지, HW 적인 관점을 이해하신다면 훌륭한 설계엔지니어가 되실 것 같아요.

이 책을 추천드립니다.

즐공하세요 :)

감사합니다 !