인프런 커뮤니티 질문&답변

퀴즈 4 cnt f/f 변수 출력값 관련 질문

해결된 질문

작성

·

81

1

안녕하세요 🙂

[1. 질문 챕터] : fpga 외전 1 시계만들기 Chapter 1 2분 9초 퀴즈 4번 부분

[2. 질문 내용]

cnt flipflop의 변수 출력값이 1억 - 1이라고 하셨는데, 1억이 아닌지 여쭤보고 싶습니다.

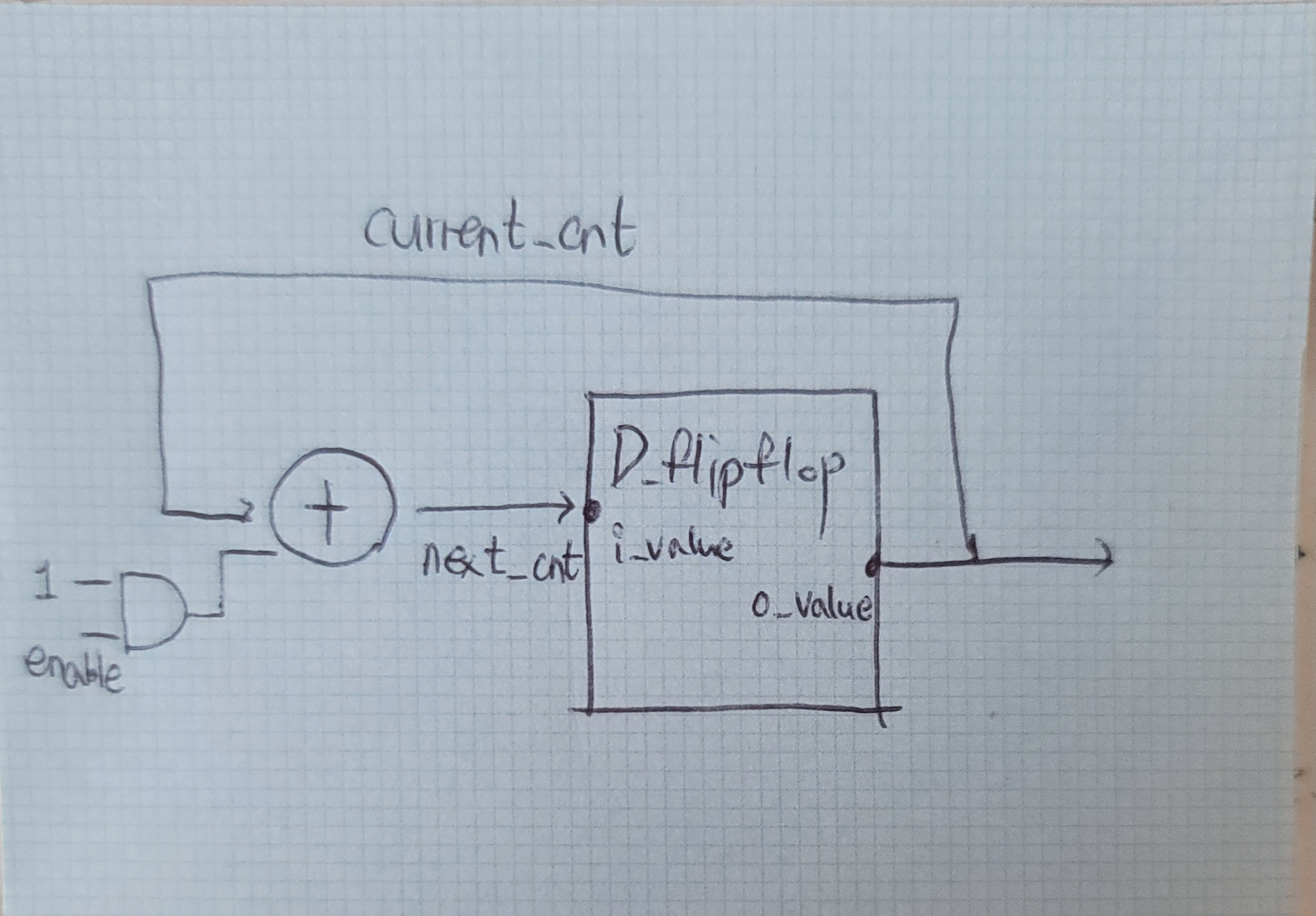

보여주신 코드 상에서는 cnt f/f 변수의 출력값이 1억 -1임을 시뮬레이션에서 어떻게 확인하는 것인지 잘 모르겠어서, 아래와 이 d_flipflop 모듈을 추가한 회로도를 사용하여 시뮬레이션을 돌려보았습니다. 그 결과 flip flop의 output 값이 1억이 나타났는데 확인해주시면 정말 감사하겠습니다

[3. 시도했던 내용, 그렇게 생각하는 이유]

처음 enable이 켜졌을 때 combinational logic에 의해 d_flipflop의 input 값이 1이 되고, rising edge일 때 해당 값이 저장되므로 첫번째 사이클부터 cnt f/f 변수의 출력값이 1로 나타난다고 생각했습니다. 따라서 1초가 지난 이후에도 출력값이 1억이 될 것이라고 생각했습니다.

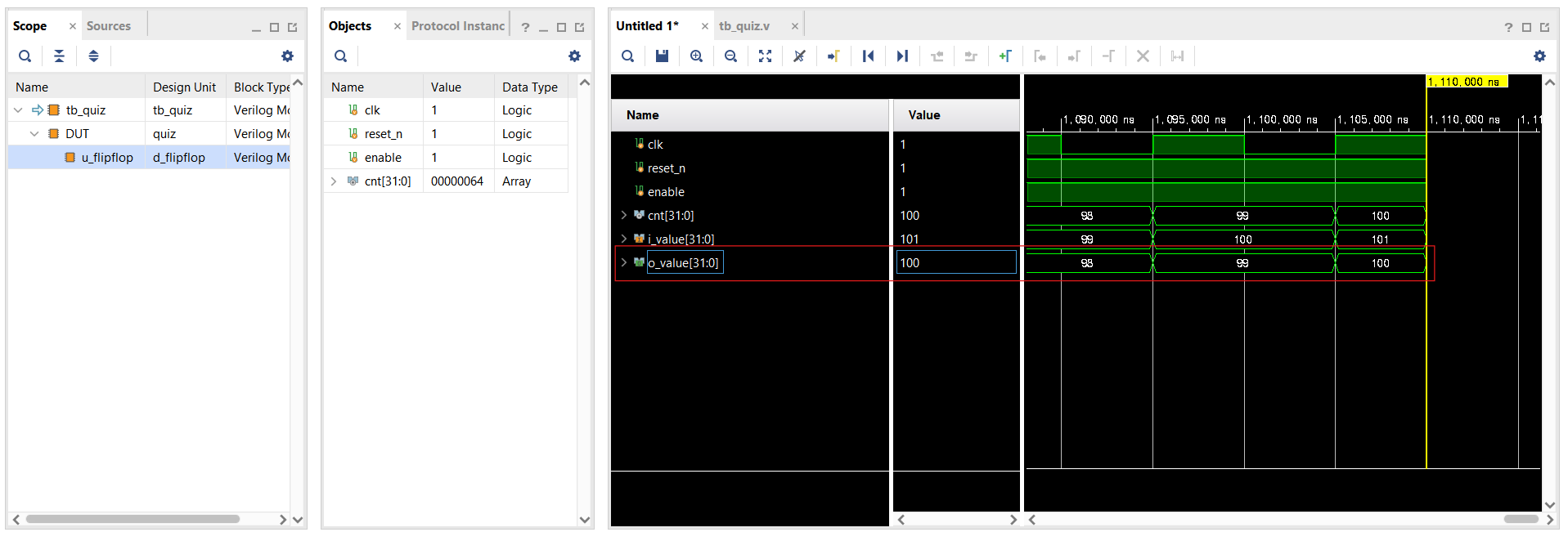

해당 회로도를 기반으로 시뮬레이션을 돌려본 결과 입니다. (편의상 100사이클만 수행하였습니다.) 100 사이클 이후 d_flipflop의 outpu이 100으로 나타나므로 퀴즈 4번의 결과 또한 1억이 나올 것 같은데, 1억 -1이 나타나는 이유가 무엇인지 궁금합니다.

+) posedge에 enable이 켜지는 상황에서는 posedge 시간에 f/f에 stable한 값이 전달되지 않으므로 첫 사이클에서의 output value가 0임을 확인했습니다. 최종적으로 cnt f/f의 출력값은 99였습니다. 그러나 이때에는 최종적인 cnt 변수 값 또한 99로 나타나므로 만약 퀴즈 4의 가정 상황이 posedge에서 enable이 켜지는 상황이라면 Q3과 Q4의 답 모두 1억 -1이 되어야 할 것 같습니다.

아래는 사용한 코드입니다. 혹시라도 시뮬레이션에서 잘못된 부분이 있다면 알려주시면 감사하겠습니다.

// tb_quiz.v

`timescale 1ns/1ps

module tb_quiz();

reg clk;

reg reset_n;

reg enable;

wire [31:0] cnt;

initial begin

clk <= 0;

reset_n <= 1;

enable <= 0;

#50

reset_n <= 0;

#10

reset_n <= 1;

#50

enable <= 1;

#1000

$finish;

end

always #5 clk = ~clk;

quiz DUT (

.clk (clk),

.reset_n (reset_n),

.enable (enable),

.o_cnt (cnt)

);

endmodule

// quiz.v

`timescale 1ns/1ps

module quiz(input clk,

input reset_n,

input enable,

output [31:0] o_cnt);

wire [31:0] current_cnt;

reg [31:0] next_cnt;

always @(*) begin

if (enable) begin

next_cnt <= current_cnt + 1;

end else begin

next_cnt <= current_cnt;

end

end

assign o_cnt = current_cnt;

d_flipflop u_d_flipflop(

.clk (clk),

.reset_n (reset_n),

.i_value (next_cnt),

.o_value (current_cnt)

);

endmodule

`timescale 1ns/1ps

module d_flipflop (input clk,

input reset_n,

input [31:0] i_value,

output [31:0] o_value);

reg [31:0] r_value;

assign o_value = r_value;

always @(posedge clk or negedge reset_n) begin

if (!reset_n) begin

r_value <= 0;

end else begin

r_value <= i_value;

end

end

endmodule

답변 1

1

안녕하세요. 🙂

기준점에 혼동이 있을 수 있겠지만, 0을 시간에 포함했기 때문에, 1억 -1 이라고 답변드렸습니다.

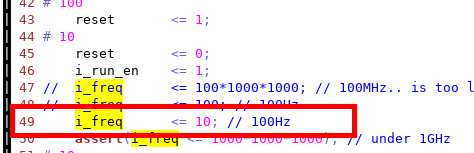

이를 확인해보기 위해서 matbi watch 1장코드에서, count 부분을 100 -> 10으로 변경하였습니다.

1억 -1 이나, 10 - 1 이나, -1 인지 확인하는 건 동일할 것 같아요.

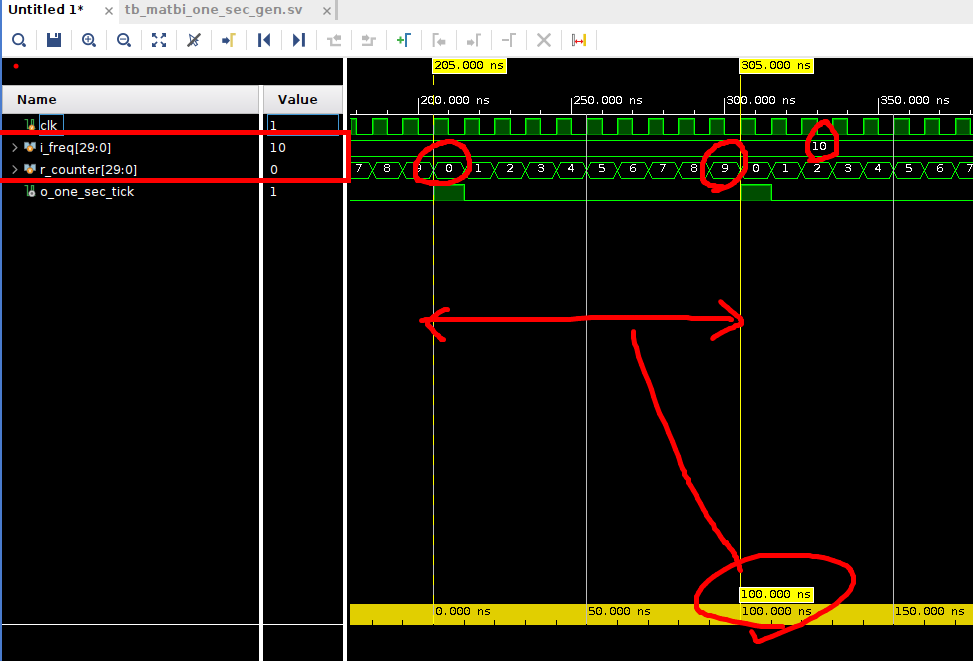

보시면, 9 다음 0 으로 넘어가죠.

그리고 0 <-> 9 까지의 시간이 100ns 의 주기를 보이고 있고요. (100 ns 부분의 마지막 count 값은 9 (= 10-1) 이라서 Q4 를 딱 1초가 지난 시점의 출력값을 1억 -1 이라고 답변드렸습니다.

하지만, 질문자님이 생각하시는 부분도 맞다고 생각해요.

논란의 요지가 있는 것 같고요. Counter 를 설계하기 위해서, -1 까지의 값을 보고 reset 을 해줘야, 정확한 1초를 만들 수 있었기 때문에, Q4 질문을 강의에 넣은거에요.

Q3 은 reset 이 없기때문에, 1억 cycle 후에 1억이라는 값이 출력될 것이고,

Q4 는 0포함 1억이 지났을때, "1억 - 1" 상태가 마지막이라서 1억 -1 이라고 답변드린거고요..

counter 의 값 기준으로 생각해주시면 감사하겠습니다.

즐공하세요!