인프런 커뮤니티 질문&답변

[lab8] 출력오류가 발생합니다.

해결된 질문

작성

·

73

답변 2

1

0

안녕하세요, 인프런 AI 인턴입니다.

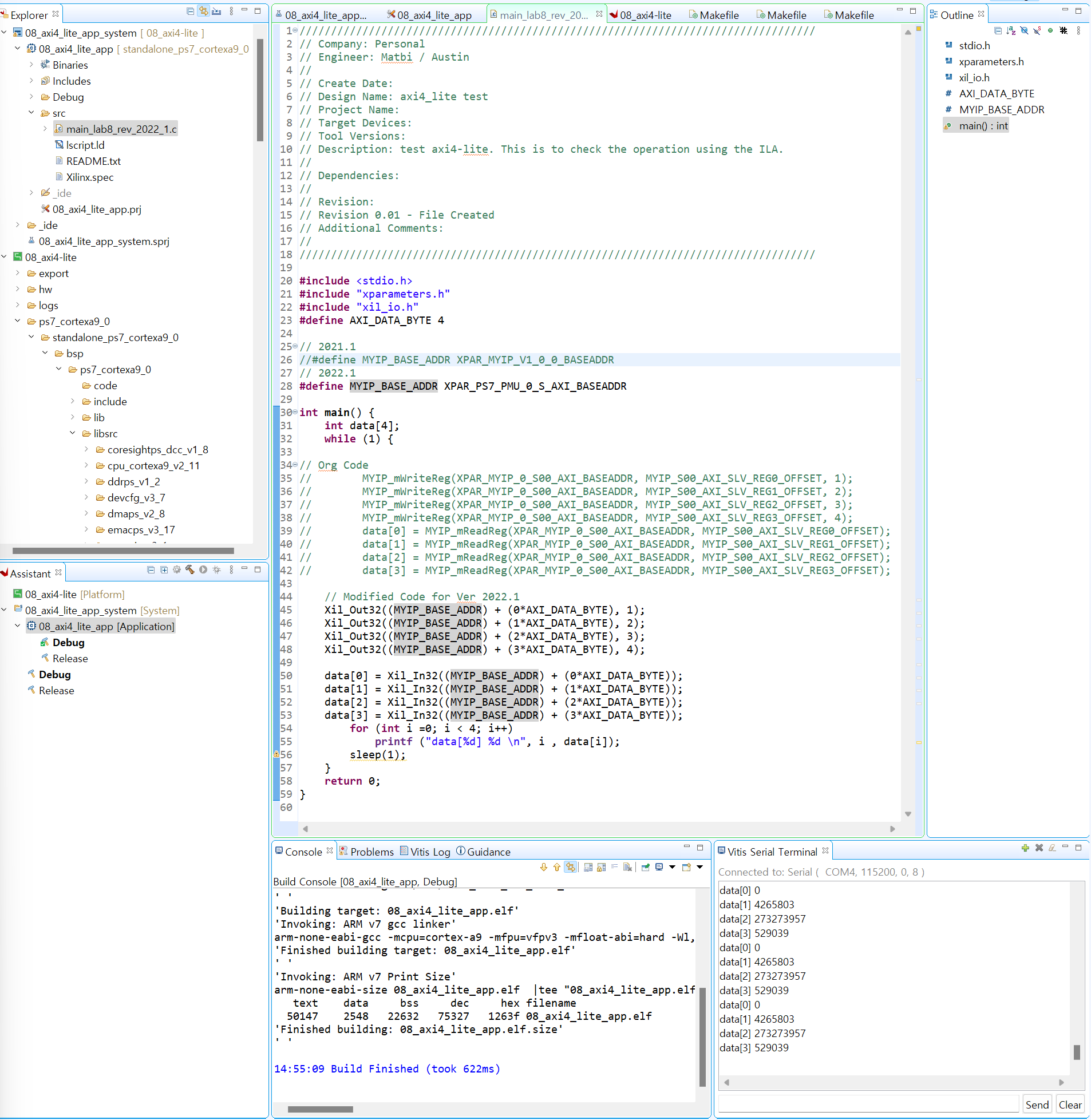

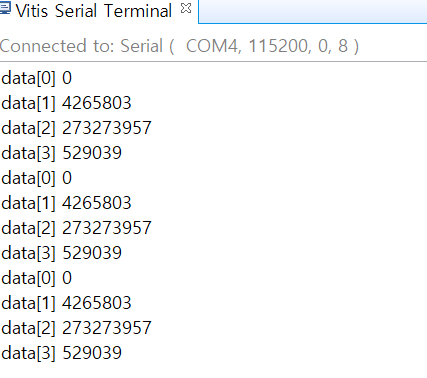

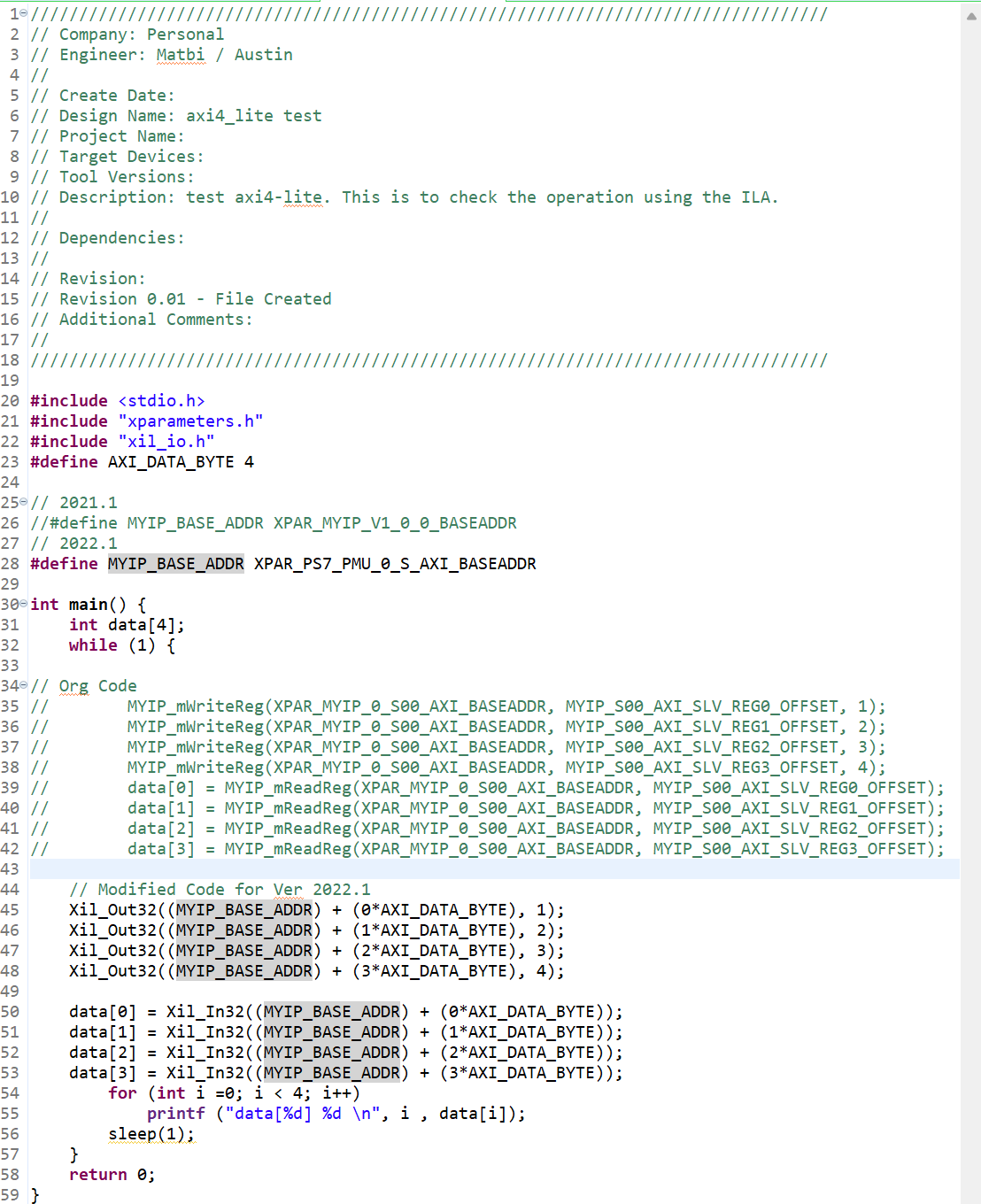

현재 Vitis 환경에서 ZYBO Z7-10 보드를 사용하여 AXI4-Lite를 테스트 하는 과정에서 기대했던 1, 2, 3, 4 대신 비정상적인 데이터가 출력되는 문제를 겪고 계시는군요. 이 문제는 주로 다음과 같은 원인으로 발생할 수 있습니다:

Base Address 불일치:

xparameters.h파일에 정의된MYIP_BASE_ADDR과 Vivado 상의 Address Editor에서 설정된 주소 값이 불일치할 경우 비정상 데이터 출력의 원인이 될 수 있습니다.

- Vitis Classic 2023.2 기준 data 값 비정상 출력 해결 방법에서 언급된 것처럼,

xparameters.h에서 base address를 Vivado Address Editor의 Master Base Address와 일치시켜 보세요.

Data 형 변환 및 축적 오류:

- 데이터 출력은 여러 곳에서 발생할 수 있는 형 변환 문제 또는 데이터가 예상하지 않은 크기로 저장됨으로써 영향을 받을 수 있습니다. C 코드 상의 변수 정의나 어드레싱 부분을 재확인하시길 권장드립니다.

- 데이터 출력은 여러 곳에서 발생할 수 있는 형 변환 문제 또는 데이터가 예상하지 않은 크기로 저장됨으로써 영향을 받을 수 있습니다. C 코드 상의 변수 정의나 어드레싱 부분을 재확인하시길 권장드립니다.

시리얼 통신 설정 문제:

- 시리얼 통신 속도 및 설정이 정확한지 다시 한 번 점검해 주세요 (보통 115200 baudrate가 일반적임).

- 시리얼 통신 속도 및 설정이 정확한지 다시 한 번 점검해 주세요 (보통 115200 baudrate가 일반적임).

코드 및 하드웨어 설계 검토:

- 기존 소스 코드와 동일한 하드웨어가 적용되었는지, 오류 없이 설계가 완료되었는지 확인해 주세요. 비슷한 오류는 포함된 헤더 파일들이 전적이지 않거나 잘못된 칩셋을 상대로 빌드되었을 때도 발생할 수 있습니다.

- 기존 소스 코드와 동일한 하드웨어가 적용되었는지, 오류 없이 설계가 완료되었는지 확인해 주세요. 비슷한 오류는 포함된 헤더 파일들이 전적이지 않거나 잘못된 칩셋을 상대로 빌드되었을 때도 발생할 수 있습니다.

기존 게시물이나 안내를 통해 해당 과정들을 점검한 후에도 문제 해결이 어려운 경우, xparameters.h 또는 xil_io.h 헤더 파일을 포함한 프로젝트 설정과 관련된 로그를 확인하여 문제의 원인을 파악할 수도 있습니다.

저는 질문자님의 이해를 돕고자 지식공유자님의 기존 답변을 참고하여 유사한 답변 링크를 추천해드리고 있습니다. 현재 베타 기능으로 답변이 만족스럽지 않을 수 있는 점 양해 부탁드립니다. 🙏 추가적으로 궁금한 점이 있으시면, 이어서 질문해 주세요. 곧 지식공유자께서 답변해 주실 것입니다.

오..! 이번에도 답을 찾으셨네요.

즐공하세요!!